# Digital Signal Theory and Components

### **Digital Fundamentals**

igital signal theory is an important aspect of Amateur Radio. With a knowledge of digital theory, there are many new worlds for the radio amateur to explore. Applications of digital signal theory include digital communications, code conversion, signal processing, station control, frequency synthesis, amateur satellite telemetry, message handling, word processing and other information handling operations.

This chapter, written by Christine Montgomery, KG0GN, presents digital-theory fundamentals and some applications of that theory in Amateur Radio. The fundamentals introduce digital mathematics, including number systems, logic devices and simple digital circuits. Next, the implementation of these simple circuits is explored in integrated circuits, their families and interfacing. Integrated circuits continue with memory chips and microprocessors, culminating in a synthesis of these components in the modern digital computer. Where possible, this chapter mentions Amateur Radio applications associated with the technologies being discussed, as well as pointers to other chapters that discuss such applications in greater depth.

#### **DIGITAL VS ANALOG**

An essential first step in understanding digital theory is to understand the difference between a *digital* and an *analog* signal. An analog value, a real number, has no end; for example, the number 1/3 is 0.333... where the 3 can be repeated forever, or 3/4 equals 0.7500... with infinite repeated 0s. A digital approximation of an analog number breaks the real number line into discrete steps, for example the integers. This process of approximating a value with discrete steps either truncates or rounds an analog value to some number of decimal places. For example, rounding 1/3 to an integer gives 0 and rounding 3/4 gives 1.

For a simple physical example, look at your wristwatch. A watch with a face — with the hands of the watch rotating in a continuous, smooth motion — is an analog display. Here, the displayed time has a *continuous* range of values, such as from 12:00 exactly to 12:00 and 1/3 second or any values in between. In contrast, a watch with a digital display is limited to *discrete* states. Here the displayed time jumps from 12:00 and 0 seconds to 12:00 and 1 second, without showing the time in between. (A watch with a second hand that jerks from one second to another could also fit the digital analogy.)

In the digital watch example, time is represented by ten distinct states (0, 1, 2, 3, 4, 5, 6, 7, 8 and 9). Digital electronic signals, however, will usually be much more limited in the number of states allowed.

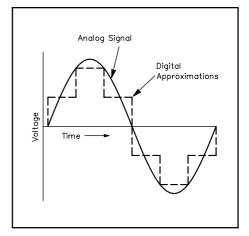

*Binary*, the most common system, has only two states: 0 and 1. Ternary (3 states), quaternary (4 states) and other digital systems also exist. **Fig 7.1** illustrates the contrast of an analog signal (in this case a sine wave) and its digital approximation.

While the focus in this chapter will be on digital theory, many circuits and systems involve *both* digital and analog components. Often, a designer may choose between using digital technology, analog technology or a combination.

Fig 7.1 — An analog signal and its digital approximation. Note that the analog waveform has continuously varying voltage while the digital waveform is composed of discrete steps.

### **Number Systems**

In order to understand digital electronics, you must first understand the digital numbering system. Any number system has two distinct characteristics: a set of *symbols* (digits or numerals) and a *base* or radix. A *number* is a collection of these digits, where the left-most digit is the *most significant digit (MSD)* and the right-most digit is the *least significant digit (LSD)*. The value of this number is a weighted sum of its digits. The *weights* are determined by the system's base and the digit's position relative to the decimal point.

While these definitions may seem strange with all the technical terms, they will be more familiar when seen in a decimal system example. This is the "traditional" number system we are all familiar with.

#### DECIMAL

The decimal system is a base-10 system, with ten symbols:  $\{0, 1, 2, 3, 4, 5, 6, 7, 8, 9\}$ . In the decimal number, 548.21, the digits are 5, 4, 8, 2 and 1, where 5 is the most significant digit since it is positioned to the far left and 1 is the least significant digit since it is positioned to the far right. The value of this number is a weighted sum of its digits, as shown in **Table 7.1**.

The weight of a position is the system's base raised to a power,  $10^{P}$  with the power determined by the position relative to the decimal. For example, digit 8, immediately to the left of the decimal, is at position 0; therefore, its weight factor is  $10^{0} = 1$ . Similarly, digit 5 is 2 positions to the left of the decimal and has a weight factor  $10^{2} = 100$ . The value of the number is the sum of each digit times its weight.

#### BINARY

Binary is a *base-2* number system that is limited to two symbols:  $\{0, 1\}$ . The weight factors are now powers of 2, like  $2^0$ ,  $2^1$  and  $2^2$ . For example, the decimal number, 163 and its equivalent binary number, 10100011, are shown in **Table 7.2**.

The digits of a binary number are now *bits* (short for binary digit). The MSD is the *most significant bit* (*MSB*) and the LSD is the *least significant bit* (*LSB*). Four bits make a *nibble* and two nibbles, or eight bits, make a *byte*. A *word* can

consist of two or four bytes, and two words (a most significant word, *MSW*, and a least significant word, *LSW*) is sometimes called a *longword*. These groupings are useful when converting to hexadecimal notation, which is explained later.

| Table <sup>·</sup> | 7.1                          |                                                  |             |                                         |             |                                       |                   |                                                     |             |                                                     |

|--------------------|------------------------------|--------------------------------------------------|-------------|-----------------------------------------|-------------|---------------------------------------|-------------------|-----------------------------------------------------|-------------|-----------------------------------------------------|

| Decimal Numbers    |                              |                                                  |             |                                         |             |                                       |                   |                                                     |             |                                                     |

| Exampl             | Example: 5(10 <sup>2</sup> ) |                                                  |             |                                         |             |                                       |                   |                                                     |             |                                                     |

| Digit = a          | 5; W                         | /eight = 1                                       | 0; F        | osition =                               | 2           |                                       |                   |                                                     |             |                                                     |

| 548.21             | =<br>=<br>=                  | 5(10 <sup>2</sup> )<br>5(100)<br>500<br>5<br>MSD | +<br>+<br>+ | 4(10 <sup>1</sup> )<br>4(10)<br>40<br>4 | +<br>+<br>+ | 8(10 <sup>0</sup> )<br>8(1)<br>8<br>8 | +<br>+<br>+<br>de | 2(10 <sup>-1</sup> )<br>2(0.1)<br>0.2<br>2<br>cimal | +<br>+<br>+ | 1(10 <sup>-2</sup> )<br>1(0.01)<br>0.01<br>1<br>LSD |

| Table 7.2<br>Decimal and Binary Number Equivalents |                     |                                          |             |   |   |                                        |   |                                       |             |                                      |             |                                      |             |                                      |             |                                      |                   |

|----------------------------------------------------|---------------------|------------------------------------------|-------------|---|---|----------------------------------------|---|---------------------------------------|-------------|--------------------------------------|-------------|--------------------------------------|-------------|--------------------------------------|-------------|--------------------------------------|-------------------|

| 163<br>10100011                                    | =<br>=<br>=         | 128<br>1(128)<br>1(2 <sup>7</sup> )<br>1 | +<br>+<br>+ | - | - | 32<br>1(32)<br>1(2 <sup>5</sup> )<br>1 |   | 0<br>0(16)<br>0(2 <sup>4</sup> )<br>0 | +<br>+<br>+ | 0<br>0(8)<br>0(2 <sup>3</sup> )<br>0 | +<br>+<br>+ | 0<br>0(4)<br>0(2 <sup>2</sup> )<br>0 | +<br>+<br>+ | 2<br>1(2)<br>1(2 <sup>1</sup> )<br>1 | +<br>+<br>+ | 1<br>1(1)<br>1(2 <sup>0</sup> )<br>1 | decimal<br>binary |

|                                                    | MSB<br>  <br>Nibble |                                          |             |   |   |                                        | I |                                       | I           | Nibb                                 | le          |                                      | LSB<br>l    | l                                    |             |                                      |                   |

#### OCTAL

Octal is a *base-8* number system, using the symbols  $\{0,1,2,3,4,5,6,7\}$ . The weight factors are now powers of 8, such as  $8^0$ ,  $8^1$  and  $8^2$ . For example, the decimal number 163 is equivalent to octal 243.

Since  $2^3 = 8$ , it is easy to switch between binary and octal just by viewing the binary number in groups of 3. (Add a leading 0 on the left most group, if the number of digits doesn't divide evenly into groups of three.)

#### HEXADECIMAL

The hexadecimal, or hex, *base-16* number system uses both numbers and characters in its set of sixteen symbols:  $\{0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F\}$ . Here, the letters A to F have the decimal equivalents of 10 to 15 respectively: A=10, B=11, C=12, D=13, E=14 and F=15. Again, the weights are powers of the base, such as  $16^0$ ,  $16^1$  and  $16^2$ . The decimal number 163 is equivalent to hex A3.

#### **CONVERSION TECHNIQUES**

An easy way to convert a number from decimal to another number system is to do repeated division, recording the remainders in a tower just to the right. The converted number, then, is the remainders, reading up the tower. This technique is illustrated in **Table 7.3** for hexadecimal, octal and binary conversions of the decimal number 163.

For example, to convert decimal 163 to hex, repeated divisions by 16 are performed. The first division gives 163 / 16 = 10 remainder 3. The remainder 3 is written in a column to the right. The second division gives 10 / 16 = 0 remainder 10. Since 10 decimal = A hex, A is written in the remainder column to the right. This division gave a divisor of 0 so the process is complete. Reading up the remainders column, the result is A3. The most common mistake in this technique is to forget that the Most Significant Digit ends up at the bottom.

Using the repeated division for binary is rather cumbersome, since the tower quickly grows large. Combining this technique with the grouping technique discussed earlier should make conversions fairly easy. Simply perform the tower division on one of the larger numbers, such as hexadecimal 16, then use grouping to put the result into binary form.

Another technique that should be briefly mentioned can be even easier: get a calculator with a binary and/ or hex mode option. One warning for this technique: this chapter doesn't discuss negative binary numbers. If your calculator does not give you the answer you expected, it may have interpreted the number as negative. This would happen when the number's binary form has a 1 in its MSB, such as the highest (leftmost) bit for the binary mode's default size. To avoid learning about negative binary numbers, always

A3 hex

use a leading 0 when you enter a number in binary or hex into your calculator.

#### BINARY CODED DECIMAL (BCD)

Scientists have experimented with many devices out of a desire for fast computations. The first generation computers were born when J. Vincent Atanasoff decided to use binary numbers instead of decimal to do his computa-

| Table 7.3<br>Number System Conversions |                                       |                                                                 |                                                                                                  |                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|----------------------------------------|---------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Remainder                              | <i>Octal</i><br>81163                 | Remainder                                                       | Binary<br>2  163                                                                                 | Re                                                                                                                                                                                                                                                                                                                                          | mainder                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 3<br>A                                 | <u>20</u><br>  <u>2</u><br>  <u>0</u> | 3<br>4<br>2                                                     | <u>81</u><br>  <u>40</u><br>  <u>20</u><br>  <u>10</u><br>  <u>5</u><br>  <u>2</u><br>  <u>1</u> | 1<br>0<br>0<br>1<br>0                                                                                                                                                                                                                                                                                                                       | LSB                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                                        | System Co<br>Remainder<br>3           | System Conversion<br>Remainder Octal<br>8  163<br>3  20<br>A  2 | System Conversions<br>Remainder Octal Remainder<br>8   163<br>3   20 3<br>A   2 4                | System Conversions           Remainder         Octal         Remainder         Binary           8   163         2   163         2   163           3           20         3           81           A           2         4           40             0         2           20           10             10           5           2           2 | System Conversions           Remainder         Octal         Remainder         Binary         Remainder $8   163$ 2   163         2         1           3 $  20 > 3$ $  81 > 1$ 1           A $  2 > 4$ $  40 > 1$ 1 $  0 > 2$ $  20 > 0$ $  10 > 0$ $  5 > 0$ $  2 > 1 = 1$ $  1 > 0$ $  1 = 0$ $  1 = 0$ |  |  |  |  |  |

243 octal

1010 0011 binary

tions. A binary number system representation is the most appropriate form for internal computations since there is a direct mathematical relationship for every bit in the number. To interface with a user — who usually wants to see I/O in terms of decimal numbers — other codes are more useful. The *Binary Coded Decimal (BCD)* system is the simplest and most widely used form for inputs and outputs of user-oriented digital systems.

In the Binary Coded Decimal (BCD) system, each decimal digit is expressed as a corresponding 4-bit binary number. In other words, the decimal digits 0 to 9 are encoded as the bit strings 0000 to 1001. To make the number easier to read, a space is left between each 4-bit group. For example, the decimal number 163 is equivalent to the BCD number 0001 0110 0011, as shown in **Table 7.4**.

A generic code could use any n-bit string to represent a piece of information. BCD uses 4 bits because that is the minimum needed to represent a 9. All four bits are always written; even a decimal 0 is written as 0000 in BCD.

The important difference between BCD and the previous number systems is that, starting with decimal 10, BCD loses the standard mathematical relationship of a weighted sum. Instead of using the 4-bit code strings 1010 to 1111 for decimal 10 to 15, BCD uses 0001 0000 to 0001 0101. There are other n-bit decimal codes in use and, even for specifically 4 bits, there are millions of combinations to represent the decimal digits

0-9. BCD is the simplest way to convert between decimal and a binary code; thus it is the ideal form for I/O interfacing. The binary number system, since it maintains the mathematical relationship between bits, is the ideal form for the computer's internal computations.

| Table 7                                | .4                 |                                         |                                        |         |  |  |  |  |  |  |

|----------------------------------------|--------------------|-----------------------------------------|----------------------------------------|---------|--|--|--|--|--|--|

| Binary Coded Decimal Number Conversion |                    |                                         |                                        |         |  |  |  |  |  |  |

|                                        | 0 0 0 1<br>        | 0 1 1 0<br>II                           | 0 0 1 1<br>                            | BCD     |  |  |  |  |  |  |

| =                                      | 1(2 <sup>0</sup> ) | 1(2 <sup>2</sup> ) + 1(2 <sup>1</sup> ) | 1(2 <sup>1</sup> )+ 1(2 <sup>0</sup> ) |         |  |  |  |  |  |  |

| =                                      | (1)                | (4 + 2)                                 | (2 + 1)                                |         |  |  |  |  |  |  |

| 163 =                                  | 1                  | 6                                       | 3                                      | decimal |  |  |  |  |  |  |

### **Physical Representation Of Binary States**

#### STATE LEVELS

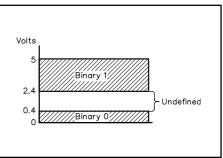

Most digital systems use the binary number system because many simple physical systems are most easily described by two state levels (0 and 1). For example, the two states may represent "on" and "off," a punched hole or the absence of a hole in paper tape or a card, or a "mark" and "space" in a communications transmission. In electronic systems, state levels are physically represented by voltages. A typical choice is

state 0 = 0 Vstate 1 = 5 V

Since it is unrealistic to obtain these exact voltage values, a more practical choice is a range of values, such as

state 0 = 0.0 to 0.4 V state 1 = 2.4 to 5.0 V

**Fig 7.2** illustrates this representation of states by voltage levels. The undefined region between the two binary states is also known as the *transition region* or *noise margin*.

#### **Transition Time**

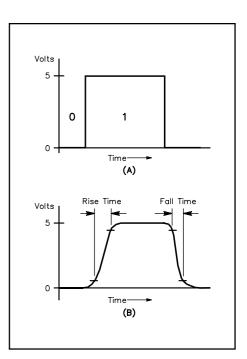

The gap in **Fig 7.2**, between binary 0 and binary 1, shows that a change in state does not occur instantly. There is a *transition time* between states. This transition time is a result of the time it takes to charge or discharge the stray capacitance in wires and other components because voltage cannot change instantaneously across a capacitor. (Stray inductance in the wires also has an effect because the current through an inductor can't change instantaneously.) The transition from a 0 to a 1 state is called the *rise time*. Similarly, the transition from a 1 to a 0 state is called the *fall time*. Note that these times need not be the same. **Fig 7.3A** shows an ideal signal, or *pulse*, with zero-time switching. Fig 7.3B shows a typical pulse, as it changes between states in a smooth curve.

Rise and fall times vary with the logic family used and the location in a circuit. Typical values of transition time are in the microsecond to nanosecond range. In a circuit, distributed inductances and capacitances in wires or PC-board traces may cause rise and fall times to increase as the pulse moves away from the source.

#### **Propagation Delay**

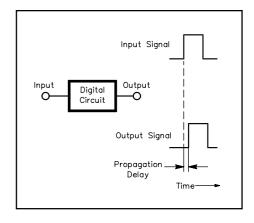

Rise and fall times only describe a relationship within a pulse. For a circuit, a pulse input into the circuit must propagate through the circuit; in other words it must pass through each component in the circuit until eventually it arrives at the circuit output. The time delay between providing an input to a circuit and to seeing a

Fig 7.2 — Representation of binary states 1 and 0 by a selected range of voltage levels.

Fig 7.3 — (A) An ideal digital pulse and (B) a typical actual pulse, showing the gradual transition between states.

response at the output is the *propagation delay*, and is illustrated by **Fig 7.4**.

For modern switching logic, typical propagation delay values are in the 1 to 15 nanosecond range. (It is useful to remember that the propagation delay along a wire or printed-circuit-board trace is about 1.0 to 1.5 ns per inch.) Propagation delay is the result of cumulative transition times as well as transistor switching delays, reactive element charging times and the time for signals to travel through wires. In complex circuits, different propagation delays through different paths can cause problems when pulses must arrive somewhere at exactly the same time. Solutions to this timing problem include adding a buffer amplifier to the circuit and synchronization of circuits. These are discussed in later sections.

Fig 7.4 — Propagation delay in a digital circuit.

### **Combinational Logic**

Having defined a way to use voltage levels to physically represent digital numbers, we can apply digital signal theory to design useful circuits. Digital circuits combine binary inputs to produce a desired binary output or combination of outputs. This simple combination of 0s and 1s can become very powerful, implementing everything from simple switches to powerful computers.

A digital circuit falls into one of two types: combinational logic or sequential logic. In a *combinational logic* circuit, the output depends only on the *present inputs*. (If we ignore propagation delay.) In contrast, in a *sequential logic* circuit, the output depends on the present inputs, the *previous sequence of inputs* and often a clock signal. John F. Wakerly, on page 147 of *Digital Design Principles and Practices*, described this difference as follows: "The rotary channel selector knob on an inexpensive TV is like a combinational circuit — its 'output' selects a channel based only on the current position of the knob ('input'). In contrast, the channel selector controlled by the up [+] and down [–] pushbuttons on a fancy TV or VCR is a sequential circuit — the channel selection depends on the past sequence of up/down pushes... as far back as when you first powered-up the device."

The next section discusses combinational logic circuits. Later, we will build sequential logic circuits from the basics established here.

#### **BOOLEAN ALGEBRA AND THE BASIC LOGICAL OPERATORS**

Combinational circuits are composed of logic gates, which perform binary operations. Logic gates manipulate binary numbers, so you need an understanding of the algebra of binary numbers to understand how logic gates operate. *Boolean algebra* is the mathematical system to describe and design binary digital circuits. It is named after George Boole, the mathematician who developed the system. Standard algebra has a set of basic operations: addition, subtraction, multiplication and division. Similarly, Boolean algebra has a set of basic operations, called *logical operations*: NOT, AND and OR.

The function of these operators can be described by either (A) a Boolean equation or (B) a truth table. A Boolean *equation* describes an operator's function by representing the inputs and the operations performed on them. An equation is of the form "B = A," while an *expression* is of the form "A." In an assignment equation, the inputs and operations appear on the right and the result, or output, is assigned to the variable on the left.

A *truth table* describes an operator's function by listing all possible inputs and the corresponding outputs. Truth tables are sometimes written with Ts and Fs (for true and false) or with their respective equivalents, 1s and 0s. In company databooks (catalogs of logic devices a company manufactures), truth tables are usually written with Hs and Ls (for high and low). In the figures, 1 will mean high and 0 will mean low. This representation is called positive logic. The meaning of different logic types and why they are useful is discussed in a later section.

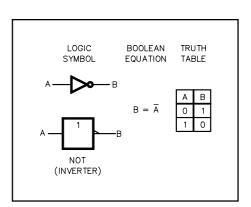

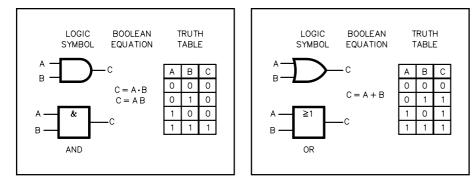

Each Boolean operator also has two circuit symbols associated with it. The traditional symbol — used by ARRL and other US publications — appears on top in each of the figures; for example, the triangle and bubble for the NOT function in **Fig 7.5**. In the traditional symbols, a small circle, or *bubble*, always represents "NOT." (This *bubble* is called a state indicator.) Appearing just below the traditional symbol is the newer ANSI/IEEE Standard symbol. This symbol is always a square box with notations inside it. In these newer symbols, a small flag represents "NOT." The new notation is an attempt to replace the detailed logic drawing of a complex function with a simpler block symbol.

Figs 7.5, 7.6 and 7.7 show the truth tables, Boolean algebra

Fig 7.5 — Inverter.

Fig 7.6 — Two-input AND gate.

Fig 7.7 — Two-input OR gate.

equations and circuit symbols for the three basic Boolean operations: NOT, AND and OR. All combinational logic functions, no matter how complex, can be described in terms of these three operators.

The NOT operation is also called *inversion*, *negation* or *complement*. The circuit that implements this function is called an *inverter* or *inverting buffer*. The most common no-

tation for NOT is a bar over a variable or expression. For example, NOT A is denoted  $\overline{A}$ . This is read as either "Not A" or as "A bar." A less common notation is to denote Not A by A', which is read as "A prime."

While the inverting buffer and the noninverting buffer covered later have only one input and output, many combinational logic elements can have multiple inputs. When a combinational logic element has two or more inputs and one output, it is called a *gate*. (The term "gate" has many different but specific technical uses. For a clarification of the many definitions of gate, see the section on Synchronicity and Control Signals, later in this chapter.) For simplicity, the figures and truth tables for multiple-input elements will show the operations for only two inputs, the minimum number.

The output of an AND function is 1 only if *all* of the inputs are 1. Therefore, if *any* of the inputs are 0, then the output is 0. The notation for an AND is either a dot (•) between the inputs, as in  $C = A \cdot B$ , or nothing between the inputs, as in C = AB. Read these equations as "C equals A AND B."

The OR gate detects if one or more inputs are 1. In other words, if *any* of the inputs are 1, then the output of the OR gate is 1. Since this includes the case where more than one input may be 1, the OR operation is also known as an INCLUSIVE OR. The OR operation detects if *at least one* input is 1. Only if all the inputs are 0, then the output is 0. The notation for an OR is a plus sign (+) between the inputs, as in C = A + B. Read this equation as "C equals A OR B."

#### **Other Common Gates**

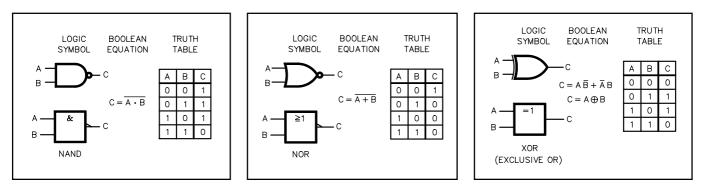

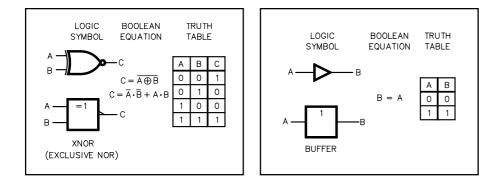

More complex logical functions are derived from combinations of the basic logical operators. These operations — NAND, NOR, XOR, XNOR and the noninverter — are illustrated in **Figs 7.8** through 7.12 respectively. As before, each is described by a truth table, Boolean algebra equation and circuit symbols. Also as before, except for the noninverter, each could have more inputs than the two illustrated.

Fig 7.8 — Two-input NAND gate.

Fig 7.9 — Two-input NOR gate. Fig 7

Fig 7.10 — Two-input XOR gate.

The NAND gate (short for NOT AND) is equivalent to an AND gate followed by a NOT gate. Thus, its output is the complement of the AND output: The output is a 0 only if all the inputs are 1. If any of the inputs is 0, then the output is a 1.

The NOR gate (short for NOT OR) is equivalent to an OR gate followed by a NOT gate. Thus, its output is the

complement of the OR output: If any of the inputs are 1, then the output is a 0. Only if all the inputs are 0, then the output is a 1.

Fig 7.12 — Noninverting buffer.

The operations so far enable a designer to determine two general cases: (1) if *all* inputs have a desired state or (2) if *at least one* input has a desired state. The XOR and XNOR gates enable a designer to determine if *one and only one* input of a desired state is present.

The XOR gate (read as EXCLUSIVE OR) has an output of 1 if one and only one of the inputs is a 1 state. The output is 0 otherwise. The symbol for XOR is  $\oplus$ . This is easy to remember if you think of the "+" OR symbol enclosed in an "O" for *only one*.

The XOR gate is also known as a "half adder," because in binary arithmetic it does everything but the "carry" operation. The following examples show the possible binary additions for a two-input XOR.

0 0 1 1

Fig 7.11 — Two-input XNOR

gate.

- $\underline{0}$   $\underline{1}$   $\underline{0}$   $\underline{1}$

- 0 1 1 0

The XNOR gate (read as EXCLUSIVE NOR) is the complement of the XOR gate. The output is 0 if one and only one of the inputs is a 1. The output is 1 either if all inputs are 0 or more than one input is 1.

#### Noninverter

A non*inverter*, also known as a *buffer*, *amplifier* or *driver*, at first glance does not seem to do anything. It simply receives an input and produces the same output. In reality, it is changing other properties of the signal in a useful fashion, such as amplifying the current level. The practical uses of a noninverter include (A) providing sufficient current to drive a number of gates, (B) interfacing between two logic families, (C) obtaining a desired pulse rise time and (D) providing a slight delay to make pulses arrive at the proper time.

#### **BOOLEAN THEOREMS**

The analysis of a circuit starts with a logic diagram and then derives a circuit description. In digital circuits, this description is in the form of a truth table or logical equation. The *synthesis*, or design, of a circuit goes in the reverse: starting with an informal description, determining an equation or truth table and then expanding the truth table to components that will implement the desired response. In both of these processes, we need to either simplify or expand a complex logical equation.

To manipulate an equation, we use mathematical *theorems*. Theorems are statements that have been proven to be true. The theorems of Boolean algebra are very similar to those of standard algebra, such as commutativity and associativity. Proofs of the Boolean algebra theorems can be found in an introductory digital design textbook.

#### **BASIC THEOREMS**

**Table 7.5** lists the theorems for a single variable and **Table 7.6** lists the theorems for two or more variables. These tables illustrate the *principle of duality* exhibited by the Boolean theorems: Each theorem has a dual in which, after swapping all ANDs with ORs and all 1s with 0s, the statement is still true.

The tables also illustrate the precedence of the Boolean operations: the order in which operations are performed when not specified by parenthesis. From highest to lowest, the precedence is NOT, AND then OR. For example, the distributive law includes the expression "A + B•C." This is equivalent to "A +  $(B \cdot C)$ ." The parenthesis around (B•C) can be left out since an AND operation has higher priority than an OR operation. Precedence for Boolean algebra is similar to the convention of standard algebra: raising to a power, then multiplication, then addition.

#### **DeMorgan's Theorem**

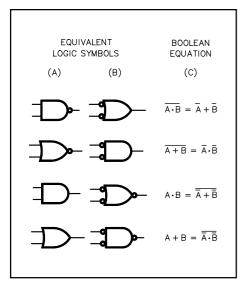

One of the most useful theorems in Boolean algebra is DeMorgan's Theorem: and its dual  $\overline{A \bullet B} = \overline{A} + \overline{B}$  $\overline{A+B} = \overline{A} \cdot \overline{B}$ . The truth table in Table 7.7 proves these statements. DeMorgan's Theorem provides a way to simplify the complement of a large expression. It also enables a designer to interchange a number of equivalent gates, as shown by **Fig 7.13**.

The equivalent gates show that the duality principle works with symbols the same as it does for Boolean equations: just swap ANDs with ORs and switch the bubbles. For example, the NAND gate — an AND gate followed by an in-

| Table 7.5                                |                                          |                        |  |  |  |  |  |  |  |

|------------------------------------------|------------------------------------------|------------------------|--|--|--|--|--|--|--|

| Boolean Algebra Single Variable Theorems |                                          |                        |  |  |  |  |  |  |  |

| Identities:                              | A • 1 = A                                | A + 0 = A              |  |  |  |  |  |  |  |

| Null elements:                           | A • 0 = 0                                | A + 1 = 1              |  |  |  |  |  |  |  |

| Idempotence:                             | $A \bullet A = A$                        | A + A = A              |  |  |  |  |  |  |  |

| Complements:                             | $\underline{A \bullet} \overline{A} = 0$ | $A + \overline{A} = 1$ |  |  |  |  |  |  |  |

| Involution:                              | $(\overline{A}) = A$                     |                        |  |  |  |  |  |  |  |

#### Table 7.6

| Boolean Algebra Multivariable Theorems |                                                                                                                                                                                       |  |  |  |  |  |  |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Commutativity:                         | $A \bullet B = B \bullet A$ $A + B = B + A$                                                                                                                                           |  |  |  |  |  |  |

| Associativity:                         | $(A \bullet B) \bullet C = A \bullet (B \bullet C)$<br>(A + B) + C = A + (B + C)                                                                                                      |  |  |  |  |  |  |

| Distributivity:                        | $(A + B) \cdot (A + C) = A + B \cdot C$<br>$A \cdot B + A \cdot C = A \cdot (B + C)$                                                                                                  |  |  |  |  |  |  |

| Covering:                              | $ A \bullet (A + B) = A A + A \bullet B = A $                                                                                                                                         |  |  |  |  |  |  |

| Combining:                             | $(A + B) \bullet (A + B) = A$<br>$A \bullet B + A \bullet \overline{B} = A$                                                                                                           |  |  |  |  |  |  |

| Consensus:                             | $A \bullet B + \overline{A} \bullet C + B \bullet C = A \bullet B + \overline{A} \bullet C$ $(A + B) \bullet (\overline{A} + C) \bullet (B + C) = (A + B) \bullet (\overline{A} + C)$ |  |  |  |  |  |  |

#### Table 7.7 DeMorgan's Theorem

| 2011              | Beinergan e meeren |     |            |       |     |       |                  |     |                               |  |  |  |

|-------------------|--------------------|-----|------------|-------|-----|-------|------------------|-----|-------------------------------|--|--|--|

| (A)<br>(B)<br>(C) | _                  |     | Ā+Ē<br>Ā•Ē | -     |     |       |                  |     |                               |  |  |  |

| (1)               | (2)                | (3) | (4)        | (5)   | (6) | (7)   | (8)              | (9) | (10)                          |  |  |  |

| Α                 | В                  | Ā   | B          | A • B | A•B | A + B | $\overline{A+B}$ | Ā∙B | $\overline{A} + \overline{B}$ |  |  |  |

| 0                 | 0                  | 1   | 1          | 0     | 1   | 0     | 1                | 1   | 1                             |  |  |  |

| 0                 | 1                  | 1   | 0          | 0     | 1   | 1     | 0                | 0   | 1                             |  |  |  |

| 1                 | 0                  | 0   | 1          | 0     | 1   | 1     | 0                | 0   | 1                             |  |  |  |

| 1                 | 1                  | 0   | 0          | 1     | 0   | 1     | 0                | 0   | 0                             |  |  |  |

(A) and (B) are statements of DeMorgan's Theorem. The truth table at (C) is proof of these statements: (A) is proven by the equivalence of columns 6 and 10 and (B) by columns 8 and 9.

Fig 7.13 — Equivalent gates from DeMorgan's Theorem: Each gate in column A is equivalent to the opposite gate in column B. The Boolean equations in column C formally state the equivalences.

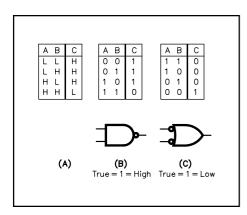

Fig 7.14 — (A) A general truth table, (B) a truth table and NAND symbol for positive logic and (C) a truth table and NOR symbol for negative logic.

verter bubble — becomes an OR gate preceded by two inverter bubbles. DeMorgan's Theorem is important because it means any logical function can be implemented using either inverters and AND gates or inverters and OR gates. Also, the ability to change placement of the bubbles using DeMorgan's Theorem is useful in dealing with mixed logic, to be discussed next.

#### **POSITIVE AND NEGATIVE LOGIC**

The truth tables shown in the figures in this chapter are drawn for positive logic. In *positive logic*, or *high true*, a higher voltage means true (logic 1) while a lower voltage means false (logic 0). This is also referred to as *active high*: a signal performs a named action or denotes a condition when it is "high" or 1. In *negative logic*, or *low true*, a lower voltage means true (1) and a higher voltage means false (0). An *active low* signal performs an action or denotes a condition when it is "low" or 0.

In both logic types, true = 1 and false = 0; but whether true means high or low differs. Company databooks are drawn for general truth tables: an "H" for high and an "L" for low. (Some tables also have an "X" for a "don't care" state.) The function of the table can differ depending on whether it is interpreted for positive logic or negative logic. **Fig 7.14** shows how a general truth table differs when interpreted for different logic types. The same truth table gives two equivalent gates: positive logic gives the function of a NAND gate while negative logic gives the function of a NOR gate.

Note that these gates correspond to the equivalent gates from DeMorgan's Theorem. A bubble on an input or output terminal indicates an active low device. The absence of bubbles indicates an active high device.

Like the bubbles, signal names can be used to indicate logic states. These names can aid the understanding of a circuit by indicating control of an action (GO, /ENABLE) or detection of a condition (READY, /ERROR). The action or condition occurs when the signal is in its active state. When a signal is in its active state, it is called *asserted*; a signal not in its active state is called *negated* or *deasserted*. A prefix can easily indicate a signal's active state: active low signals are preceded by a "/," like /READY,

while active high signals have no prefix. Standard practice is that the signal name and input pin match (have the same active level). For example, an input with a bubble (active low) may be called /READY while an input with no bubble (active high) is called READY. Output signal names should always match the device output pin.

In this chapter, positive logic is used unless indicated otherwise. Although using mixed logic can be confusing, it does have some advantages. Mixed logic combined with DeMorgan's Theorem can promote more effective use of available gates. Also, well-chosen signal names and placement of bubbles can promote more understandable logic diagrams.

### **Sequential Logic**

The previous section discussed combinational logic, whose outputs depend only on the present inputs. In contrast, in *sequential logic* circuits, the new output depends not only on the present inputs but also on the present outputs. The present outputs depended on the previous inputs and outputs and those earlier outputs depended on even earlier inputs and outputs and so on. Thus, the present outputs depend on the previous *sequence of inputs* and the system has *memory*. Having the outputs become part of the new inputs is known as *feedback*.

This section first introduces a number of terms necessary to understand sequential logic: types of synchronicity, types of control signals and ways to illustrate circuit function. Numerous sequential logic circuits are then introduced. These circuits provide an overview of the basic sequential circuits that are commercially available. Depending on your approach to learning, you may choose to either (1) read the material in the order presented, definitions then examples, or (2) start with the example circuits, which begin with the flip-flop, referring back to the definitions as needed.

#### SYNCHRONICITY AND CONTROL SIGNALS

When a combinational circuit is given a set of inputs, the outputs take on the expected values after a propagation delay during which the inputs travel through the circuit to the output. In a sequential circuit, however, the travel through the circuit is more complicated. After application of the first inputs and one propagation delay, the outputs take on the resulting state; but then the outputs start trickling back through and, after a second propagation delay, new outputs appear. The same happens after a third propagation delay. With propagation delays in the nanosecond range, this cycle around the circuit is rapidly and continually generating new outputs. A user needs to know when the outputs are valid.

There are two types of sequential circuits: synchronous circuits and asynchronous circuits, which are analyzed differently for valid outputs. In *asynchronous* operation, the outputs respond to the inputs immediately after the propagation delay. To work properly, this type of circuit must eventually reach a *stable* state: the inputs and the fed back outputs result in the new outputs staying the same. When the nonfeedback inputs are changed, the feedback cycle needs to eventually reach a new stable state.

In *synchronous* operation, the outputs change state only at specific times. These times are determined by the presence of a particular input signal: a clock, toggle, latch or enable. Synchronicity is important because it ensures proper timing: all the inputs are present where needed when the control signal causes a change of state.

Some authors vary the meanings slightly for the different control signals. The following is a brief illustration of common uses, as well as showing uses for noun, verb and adjective. *Enabling* a circuit generally means the control signal goes to its asserted level, allowing the circuit to change state. *Latch*

implies memory: (noun) a circuit that stores a bit of information or (verb) to hold at the same output state. *Gate* has many meanings, some unrelated to synchronous control: (A) a signal used to trigger the passage of other signals through a circuit (for example, "A gate circuit passes a signal only when a gating pulse is present."), (B) any logic circuit with two or more inputs and one output (used earlier in this chapter) or (C) one of the electrodes of an FET (as described in the **Analog Signals and Components** chapter). To *toggle* means a signal changes state, from 1 to 0 or vice versa. A *clock* signal is one that toggles at a regular rate.

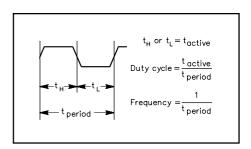

Clock control is the most common method, so it has some additional terms, illustrated by **Fig 7.15**. The *clock period* is the time between successive transitions in the same direction; the *clock*

Fig 7.15 — Clock signal terms. The duty cycle would be  $t_H / t_{PERIOD}$  for an active high signal and  $t_L / t_{PERIOD}$  for an active low signal.

*frequency* is the reciprocal of the period. A *pulse* or *clock tick* is the first edge in a clock period, or sometimes the period itself or the first half of the period. The *duty cycle* is the percentage of time that the clock signal is at its asserted level.

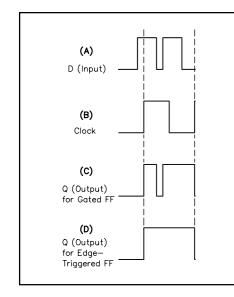

The reaction of a synchronous circuit to its control signal is *static* or *dynamic*. Static, *gated* or *level-triggered* control allows the circuit to change state whenever the control signal is at its active or asserted level. Dynamic, or *edge-triggered*, control allows the circuit to change state only when the control signal *changes* from unasserted to asserted. By convention, a control signal is active high if state changes occur when the signal is high or at the rising edge and active low in the opposite case. Thus, for positive logic, the convention is enable = 1 or enable goes from 0 to 1. This transition from 0 to 1 is called *positive edge-triggered* and is indicated by a small triangle inside the circuit box. A circuit responding to the opposite transition, from 1 to 0, is called *negative edge-triggered*, indicated by a bubble with the triangle. Whether a circuit is level-triggered or edge-triggered can affect its output, as shown by **Fig 7.16**. Input D includes a very brief pulse, called a *glitch*, which may be caused by noise. The differing results at the output illustrate how noise can cause errors.

#### **ILLUSTRATING CIRCUIT FUNCTION**

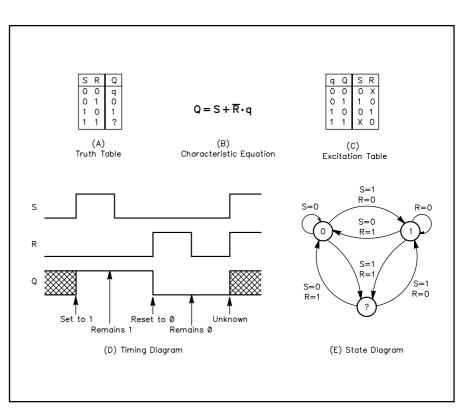

Since the action of sequential circuits is more complex, many ways have been developed to examine circuit function. **Fig 7.17** shows an example for each type of table or diagram. Each type has advantages and disadvantages.

#### **State Transition Tables**

Describing a sequential circuit with the conventional truth table would require an infinite number of

Fig 7.16 — Level-triggered vs edge-triggered for a D flip-flop: (A) input D, (B) clock input, (C) output Q for level-triggered: circuit responds whenever clock is 1. (D) output Q for edgetriggered: circuit responds only at rising edge of clock. Notice that the short negative pulse on the input D is not reproduced by the edge-triggered flip-flop.

Fig 7.17 — Sequential circuit function for a clocked S-R flip-flop: (A) state transition table or truth table, (B) characteristic equation, including its derivation from the state table, (C) excitation table, (D) partial timing diagram, (E) state diagram.

previous events as the possible inputs. Instead, the sequential logic form of the truth table is called a state transition table. A *state transition* (or excitation) *table* lists all combinations of present inputs and feedback outputs — the *current state*, represented by small q, and the resulting outputs, both feedback and nonfeedback and the *next state*, represented by capital Q. The state transition table is the most common way to describe sequential circuit function, since it lists all possibilities.

#### **Characteristic Equation**

An equivalent equation for a state transition table or excitation table can be written in terms of the *state variables*, a symbol for each input and output. Although the number of state variables can be very large for a complex system, there is always a limited number of inputs and outputs; thus, the combinations of inputs and outputs is also limited. A circuit with n binary state variables has 2<sup>n</sup> possible states. Since the possible states, 2<sup>n</sup>, are always finite, sequential circuits are also known as *finite-state machines*. Each of the sequential logic circuits in this section includes a state table to illustrate the circuit functions. As before, these tables are for positive logic, so 1s and 0s are already substituted for Highs and Lows.

#### **Excitation Table**

An *excitation table* is derived from the truth table. Its usefulness is to show, for each possible output  $Q_n$  what inputs are needed to obtain a desired output  $Q_{n+1}$ . For some outputs, one or more of the input variables may not have an effect. In this case, the input variable corresponds to a *don't care* state, represented by an "X" or dash.

#### **Timing Diagram**

When a clock is the controlling signal, a timing diagram can describe the circuit operation. A *timing diagram* draws a circuit's signals as a function of time. This form emphasizes the cause-and-effect delays between critical signals. It is especially useful in detecting errors, as will be shown in the flip-flop implementations to be presented. There are software packages available to *simulate* a circuit. The simulation produces the timing diagram for a given set of inputs, allowing the designer to examine the timing diagram for expected results.

#### State Diagram

A *state diagram* depicts output changes in terms of a flow chart. Each possible state is listed inside a circle with arrows between the circles to indicate possible next states. State diagrams are especially useful for studying a sequence of inputs and the corresponding result.

#### **FLIP-FLOPS**

Flip-flops are the basic building blocks of sequential circuits. A *flip-flop* is a device with two stable states: the *set* state (1) or the *reset* state (0). (The reset state is also called the *cleared* state.) The flip-flop can be placed in one or the other of the two states by applying the appropriate input. (Since a common use of flip-flops is to store one bit of information, some use the term *latch* interchangeably with flip-flop. A set of latches, or flip-flops holding an n-bit number is called a register.) While gates have special symbols, the schematic symbol for most components is a rectangular box with the circuit name or abbreviation, the signal names and assertion bubbles. For flip-flops, the circuit name is usually omitted since the signal names are enough to indicate a flip-flop and its type. The four basic types of flip-flops are the S-R, D, T and J-K. The first section examines the S-R flip-flop for each of the various control methods. The next section introduces each of the other basic flip-flops and their uses.

#### S-R Flip-Flop

The S-R flip-flop is one of the simplest circuits for storing a bit of information. It has two inputs,

represented by S (set) and R (reset). These inputs, naturally, cause the two possible output states: if S = 1 and R = 0, then output Q is set to 1; if S = 0 and R = 1, then output Q is reset to 0; if both inputs are 0, then the output remains unchanged; and if both inputs are 1, then the output cannot be determined. The S-R flip-flop can illustrate each of the types of control signals: unclocked (asynchronous, no control signal), clocked or gated, master-slave and edge-triggered.

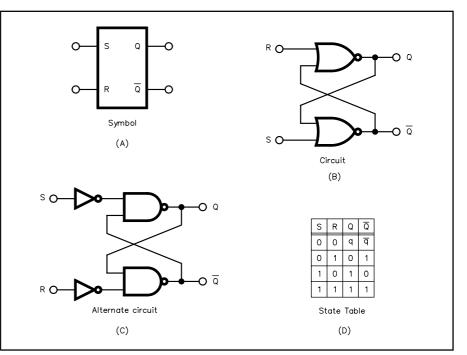

#### **Unclocked/Sequential**

The unclocked S-R flip-flop, shown in **Fig 7.18**, is an asynchronous device; its outputs change immediately to reflect changes on its inputs. The circuit consists of two NOR gates. The sequential nature of the circuit is a result of the output of each NOR gate being fed back as an input to the opposite gate. The state transition table shows the expected set/reset pattern of inputs to outputs. The table shows an unpredictable result for inputs S = 1 and R = 1. In actual circuits, the results vary and are usually either  $Q = \overline{Q} = 1$  or  $Q = \overline{Q} = 0$ . While  $Q = \overline{Q}$  is a logical impossibility, real flip-flops may present this output. The designer should avoid the R = S = 1 input and make no assumptions about the resulting output. The flip-flop is not predictable if both inputs go to 0 at exactly the same time.

Fig 7.18C shows an alternate implementation of the S-R flip-flop, with two NAND gates and two inverters. Since a NAND gate can become an inverter by having its two inputs receive the same signal, the S-R flip-flop can be implemented with four NAND gates. This alternate version is important because a 4-NAND gate chip is one of the most readily available commercial integrated circuits; thus, the 4-NAND gate S-R flip-flop can be implemented on a single IC.

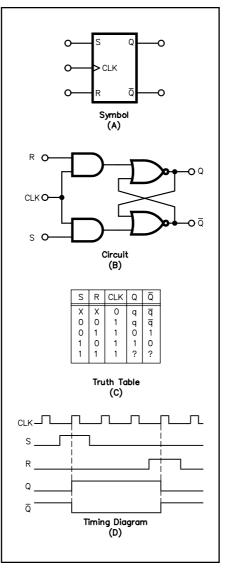

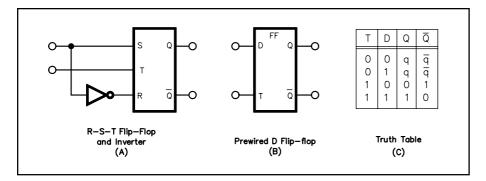

#### Gated or Level-Triggered

The gated S-R flip-flop, or gated latch, has a controlling input in addition to its S and R inputs. The inputs S and R produce the same results as those on an unclocked S-R flip-flop, but a change in output will only occur when the control input is high. A gated S-R flip-flop is illustrated in **Fig 7.19** along with a timing diagram for a clock input. This flip-flop is also called the R-S-T flip-flop, where "T," for toggle, is the clock input. Although not often used, the R-S-T flip-flop is important because it illustrates a step between the R-S flip-flop and the J-K flip-flop.

A problem with the leveltriggered flip-flop is that the Q output can change more than once while the clock is asserted. We would prefer the output to change only once per clock period for easier timing design. A second problem can occur when flip-flops are connected in series and triggered by the same clock pulse or, similarly, when a flip-flop is in series with itself, using its own output as an input. Since the series-connected flip-flop feeds back to itself, its output will be changing at about the same time as it receives new input. This can result in an erroneous output.

Fig 7.18 — Unclocked S-R Flip-Flop. (A) schematic symbol. (B) circuit diagram. (C) alternate circuit. (D) state table.

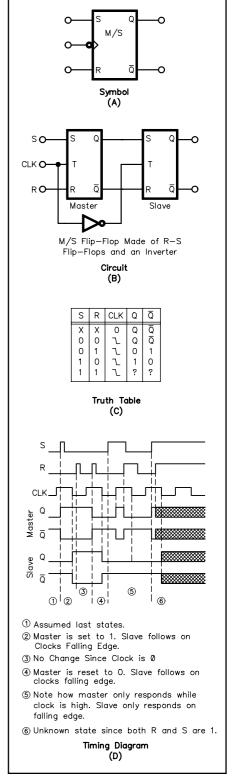

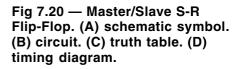

#### Master/Slave Flip-Flop

A solution to the problems of the level-triggered method is a circuit that samples and stores its inputs before changing its outputs. Such a circuit is built by placing two flip-flops in series; both flip-flops are triggered by a common clock but an inverter on the second flip-flop's clock causes it to be asserted only when the first flip-flop is not asserted. The action for a given clock pulse is as follows: The first, or master, flip-flop is active when the clock is high, sampling and storing the inputs. The second, or *slave*, flip-flop gets its input from the master and acts when the clock is low. Hence, when the clock is 1, the input is sampled; then when the clock becomes 0, the output is generated. A master/slave flip-flop is built with either two S-R flipflops, as shown by Fig 7.20, or with two J-K flip-flops. Note that a bubble appears on the schematic symbol's clock input, reminding us that the output appears when the clock is asserted low. This is conventional for TTL-style J-K flip-

Fig 7.19 — Clocked S-R Flip-Flop. (A) schematic symbol. (B) circuit. (C) truth table. (D) timing diagram.

flops, but it can be different for CMOS devices.

The master/slave method isolates output changes from input changes, eliminating the problem of series-fed circuits. It also ensures only one new output per clock period, since the slave flip-flop responds to only the single sampled input. A problem can still occur, however, because the master flip-flop can change more than once while it is asserted; thus, there is the potential for the master to sample at the wrong time. There is also the potential that either flipflop can be affected by noise.

#### **Edge-Triggered Flip-Flop**

The edge-triggered flip-flop solves the problem of noise. An example of noise is the glitch shown earlier in Fig 7.16. The different outputs for the level and edge-triggered methods in this figure show

how a glitch can cause an output error. Edge-triggering avoids the problem of noise by minimizing the time during which a circuit responds to its inputs: the chance of a glitch occurring during the nanosecond transition of a clock pulse is remote. A side benefit of edge-triggering is that only one new output is produced per clock period. Edge-triggering is denoted by a small rising-edge or falling-edge symbol such as  $\int$  or  $\downarrow$ ; sometimes an arrow is included such as  $\uparrow$  or  $\neg$ . This symbol appears in the circuit's truth table and can also appear, instead of the clock triangle, inside the schematic symbol.

#### **Other Flip-flops**

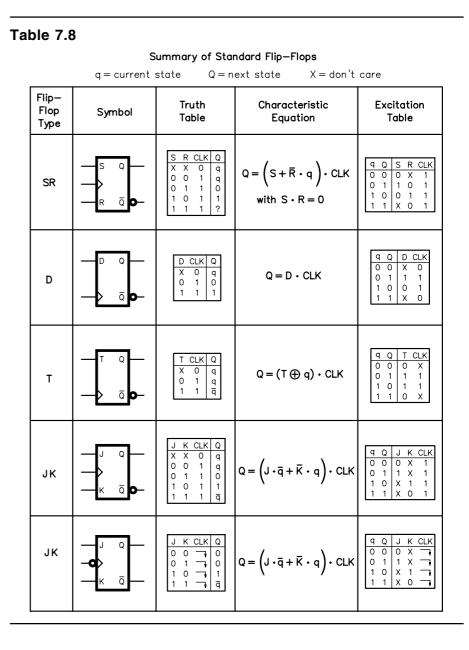

**Table 7.8** provides a summary of the four basic flip-flops: the S-R (Set-Reset), D (Data or Delay), T (Toggle) and J-K. Each is briefly explained below, including its particular applications. The internal circuitry of each of these flip-flops is similar to the components and complexity of the S-R flip-flop. Readers may be interested in trying to design their own circuit implementation for a flip-flop type and control method; however, in practical use, a commercially available integrated circuit chip would probably be used. Company databooks include the individual circuit implementation for each IC. Digital design textbooks will also show sample circuit implementations for each of the flip-flops.

#### **D** Flip-Flop

In a D (data) flip-flop, the data input is transferred to the outputs when the flip-flop is enabled: The logic level at input D is transferred to Q when the clock is positive; the Q output retains this logic level until the next positive clock pulse (see Fig 7.21). The flip-flop is also called a *delay* flip-flop because, once enabled, it passes D after a propagation delay. A D flip-flop is useful to store one bit of information. A collection of D flip-flops forms a register.

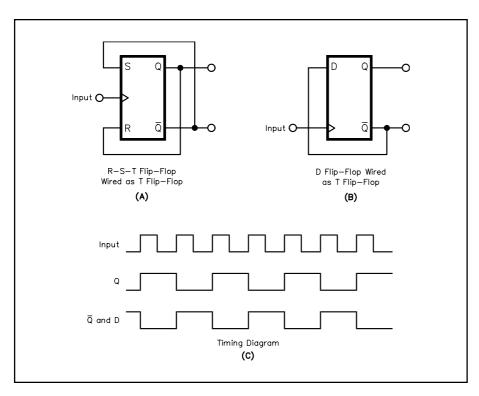

#### **Toggle Flip-Flop**

In a T flip-flop, the output *toggles* (changes state) with each positive clock pulse. The T flip-flop is also called a *complementing* flip-flop. **Fig 7.22** shows how a T flip-flop can be created from either an S-R or D flip-flop. The timing diagram in Fig 7.22 shows an important result of the T-flip-flop: the output frequency is one half of the input frequency. Thus, a T flip-flop is a

Fig 7.21 — (A) The D flip-flop. When T = 0, Q and  $\overline{Q}$  states don't change. When T = 1, the output states change to reflect the D input. (C) A truth table for the D flip-flop.

Fig 7.22 — (A) A clocked S-R-T flip-flop wired as a T flip-flop. (B) A D flip-flop wired as a T flip-flop. (C) Timing diagram. Notice that the output frequency is half the input frequency.

#### COUNTERS

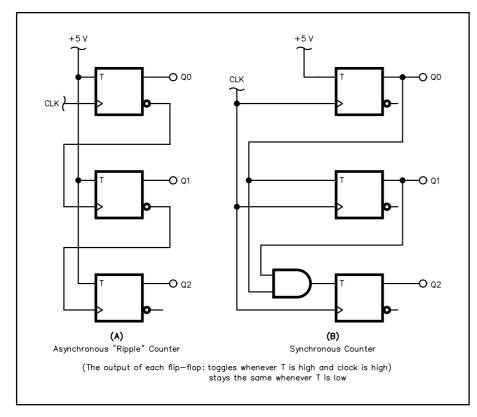

Groups of flip-flops can be combined to make counters. Toggle flip-flops are the most common for implementing a counter. Intuitively, a counter is a circuit that starts at state 0 and sequences up through states 1, 2, 3, to m, where m is the maximum number of states available. From state m, the next state will return the counter to 0. This describes the most common counter: the *n*-bit binary counter, with n outputs corresponding to  $2^n = m$  states. Such a counter can be made from n flip-flops, as shown in Fig 7.23. This figure shows implementations for each of the types of synchronicity. Both circuits pass the data count from stage to stage. In the asynchronous counter, Fig 7.23A, the clock is also passed from stage to stage and the circuit is called *ripple* or *ripple-carry*. In the synchronous counter, Fig 7.23B, each stage is controlled by a common clock signal.

2:1 (also called *modulo-2* or *radix-2*) frequency divider. Two T flip-flops connected in series form a 4:1 divider and so on.

#### J-K Flip-Flop

It's somewhat ironic that the most readily available flipflop, the J-K flip-flop, is discussed last and so briefly. The discussion is short because the J-K flip-flop acts the same as the S-R flip-flop (where J = Sand K = R) with only one difference: The S-R flip-flop had the disadvantage of invalid results for the inputs 1,1. For the J-K flip-flop, simultaneous 1,1 inputs cause Q to change state after the clock transition.

#### Summary

Only the D and J-K flip-flops are generally available as commercial integrated circuit chips. Since memory and temporary storage are so often desirable, the D flip-flop is manufactured as the simplest way to provide memory. When more functionality is needed, the J-K flip-flop is available. The J-K flip-flop can substitute for an S-R flip-flop and a T flip-flop can be created from either the D or J-K flip-flop.

Fig 7.23 — Three-bit binary counter: (A) asynchronous or ripple counter, (B) synchronous counter.

There are numerous variations on this first example of a counter. Most counters have the ability to *clear* the count to 0. Some counters can also preset to a desired count. The clear and preset control inputs are often asynchronous — they change the output state without being clocked. Counters may either count up (increment) or down (decrement). Up/down counters can be controlled to count in either direction. Counters can have sequences other than the standard numbers, for example a BCD counter.

Counters are also not restricted to changing state on every clock cycle. An n-bit counter that changes state only after m clock pulses is called a *divider* or *divide-by-m* counter. There are still  $2^n = m$  states;

however, the output after p clock pulses is now p / m. Combining different divide-by-m counters can result in almost any desired count. For example, a base 12 counter can be made from a divide-by-2 and a divide-by-6 counter; a base 10 (decade) counter consists of a divide-by-2 and a BCD divide-by-5 counter.

The outputs of these counters are binary. To produce output in decimal form, the output of a counter would be provided to a binary-to-decimal decoder chip and/or an LED display.

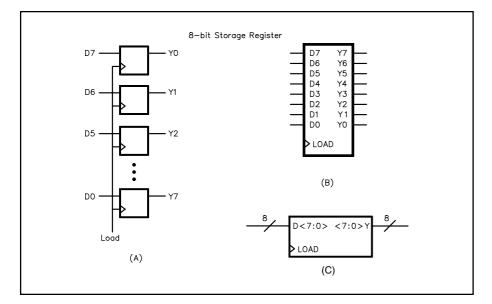

#### REGISTERS

Groups of flip-flops can be combined to make registers, usually implemented with D flip-flops. A *register* stores n bits of information, delivering that information in response to a clock pulse. Registers usually have asynchronous *set* to 1 and *clear* to 0 capabilities.

#### **Storage Register**

A storage register simply stores temporary information, for example incoming information or intermediate results. The size is related to the basic size of information handled by a computer: 8 flip-flops for an 8-bit or *byte register* or 16 bits for a *word register*. Fig 7.24 shows a typical circuit and schematic symbols for an 8-bit storage register. In (C), although the bits are passed on 8 separate lines (from 8 flipflops), a slash and number, "/8," is used to simplify the symbol. Storage registers are important to computer architecture; this topic is discussed in depth later in the chapter.

#### **Shift Register**

Shift registers also store information and provide it in response to a clock signal, but they handle their information differently: When a clock pulse occurs, instead of each flip-flop passing its result to the

Fig 7.24 — An eight-bit storage register: (A) circuit, (B) and (C) schematic symbols.

output, the flip-flops pass their data to each other, up and down the row. For example, in up mode, each flip-flop receives the output of the preceding flipflop. A data bit starting in flipflop D0 in a left shifter would move to D1, then D2 and so on until it is shifted out of the register. If a 0 was input to the least significant bit, D0, on each clock pulse then, when the last data bit has been shifted out, the register contains all 0s.

Shift registers can be left shifters, right shifters or controlled to shift in either direction. The most general form, a *universal shift register*, has two control

inputs for four states: Hold, Shift right, Shift left and Load. Most also have asynchronous inputs for preset, clear and parallel load. The primary use of shift registers is to convert parallel information to serial or vice versa. This is useful in interfacing between devices, and is discussed in detail in the Digital Interfacing section.

Additional uses for a shift register are to (1) delay or synchronize data, (2) multiply or divide a number by a factor  $2^n$  or (3) provide random data. Data can be delayed simply by taking advantage of the Hold feature of the register control inputs. Multiplication and division with shift registers is best explained by example: Suppose a 4-bit shift register currently has the value 1000 = 8. A right shift results in the new parallel output 0100 = 4 = 8 / 2. A second right shift results in 0010 = 2 = (8 / 2) / 2. Together the 2 right shifts performed a division by  $2^2$ . In general, shifting right n times is equivalent to dividing by  $2^n$ . Similarly, shifting left multiplies by  $2^n$ . This can be useful to compiler writers to make a computer program run faster. Random data is provided via a ring counter. A *ring counter* is a shift register with its output fed back to its input. At each clock pulse, the register is shifted up or down and some of the flip-flops feedback to other flip-flops, generating a random binary number. Shift registers with several feedback paths can be used as a *pseudorandom number generator*, where the sequence of bits output by the generator meets one or more mathematical criteria for randomness.

#### **MULTIVIBRATORS**

A multivibrator is widely used as a switch and comes in three basic forms: bistable, monostable and astable. It is broadly defined as a closed-loop, regenerative circuit that alternates between two stable or quasi-stable states. The flip-flop is a *bistable multivibrator*: both of its two states are stable; it can be triggered from one stable state to the other by an external signal. To create *quasi-stable* or *unstable* states, energy-storing devices (capacitors) are added in the feedback loops of the multivibrator; the instability is a result of the exponential decay of the stored energy. A *monostable multivibrator* is the result of adding one energy-storing element into a feedback loop. An *astable multivibrator* is the result of adding two energy-storing elements, one in each feedback loop.

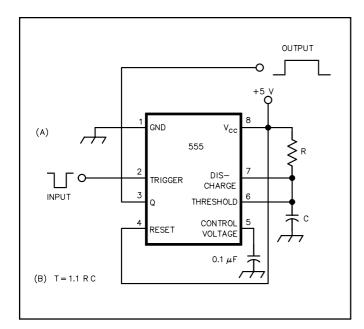

#### Monostable Multivibrator

A *monostable* or *one-shot* multivibrator has one energy-storing element in its feedback paths, resulting in one stable and one quasi-stable state. It can be switched, or *triggered*, to its quasi-stable state; then returns to the stable state after a time delay. Thus, the one-shot multivibrator puts out a pulse of some duration, T. (Note that T is not the period, but the duration of the quasi-stable state.) Triggering during the stable state results in the pulse, as expected. Triggering during the unstable state has two possibilities: A *nonretriggerable* multivibrator is not affected. A *retriggerable* multivibrator will start counting its pulse duration from the most recent trigger pulse. Both types of one-shots are common.

Fig 7.25 shows a 555 timer IC connected as a one-shot multivibrator. The one-shot is activated by a negative-going pulse between the trigger input and ground. The trigger pulse causes the output (Q) to go positive and capacitor C to charge through resistor R. When the voltage across C reaches two-thirds of  $V_{CC}$ , the capacitor is quickly discharged to ground and the output returns to 0. The output remains at logic 1 for a time determined by T = 1.1 RC, where R is the resistance in ohms and C is the capacitance in farads.

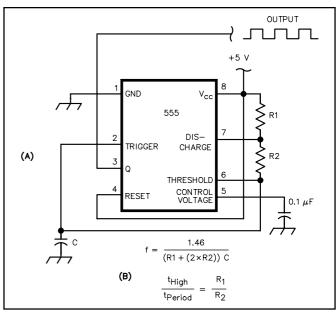

#### **Astable Multivibrator**

An *astable* or *free-running* multivibrator has two energy-storing elements in its feedback paths, resulting in two quasi-stable states. It continuously switches between these two states without external excitation. Thus, the astable multivibrator puts out a sequence of pulses. By properly selecting circuit components, these pulses can be of a desired frequency and width.

**Fig 7.26** shows a 555 timer IC connected as an astable multivibrator. The capacitor C charges to twothirds  $V_{CC}$  through R1 and R2 and discharges to one-third  $V_{CC}$  through R2. The ratio R1 : R2 sets the asserted high duty cycle of the pulse: t<sub>HIGH</sub> / t<sub>PERIOD</sub>. The output frequency is determined by:

f = 1.46 / (R1 + 2 R2) C

where:

R1 and R2 are in ohms, C in farads and f in hertz.

Fig 7.25 - (A) A 555 timer connected as a monostable multivibrator. (B) The equation to calculate values for R (in ohms) and C (in farads), where T is the pulse duration (in seconds).

Fig 7.26 — (A) A 555 timer connected as an astable multivibrator. (B) The equations to calculate values for R1, R2 (in ohms) and C (in farads), where f is the clock frequency (in Hertz).

It may be difficult to produce a 50% duty cycle, due to manufacturing tolerance for the resistors R1 and R2. One way to ensure a 50% duty cycle is to run the astable multivibrator at 2f and then divide by 2 with a toggle flip-flop.

#### Applications

An astable multivibrator is useful in generating clock pulses. When triggered by a clock pulse, the oneshot multivibrator acts to lengthen or "stretch" the pulse, which is useful to delay digital events. Either of these pulse signals, when input to the bistable multivibrator (flip-flop), can be the control of a sequential circuit. The three types of multivibrators can ensure synchronicity, so that a sequential circuit will execute correctly.

#### SUMMARY

Digital logic plays an increasingly important role in Amateur Radio. Most of this logic is binary and can be described and designed using Boolean algebra. Using the NOT, AND and OR gates of combinational logic, designers can build sequential logic circuits that have memory and feedback. The simplest sequential logic circuit is called a flip-flop. By using control inputs, a flip-flop can latch a data value, retaining one bit of information and acting as memory. Combinations of flip-flops can form useful circuits such as counters, storage registers and shift registers. The primary method of controlling sequential circuits is via a clock pulse, which can be created with a multivibrator.

### **Digital Integrated Circuits**

Integrated circuits (ICs) are the cornerstone of digital logic devices. Modern technology has enabled electronics to become miniature in size and less expensive. Today's complex digital equipment would be impossible with vacuum tubes or even with discrete transistors.

An IC is a miniature electronic module of components and conductors manufactured as a single unit. All you see is a ceramic or black plastic package and the silver-colored pins sticking out. Inside the package is a piece of material, usually silicon, created (fabricated) in such a way that it conducts an electric current to perform logic functions, such as a gate, flip-flop or decoder.

As each generation of ICs surpassed the previous one, they became classified according to the number of gates on a single chip. These classifications are roughly defined as:

Small-scale integration (SSI): 10 or fewer gates on a chip.

Medium-scale integration (MSI): 10-100 gates.

Large-scale integration (LSI): 100-1000 gates.

Very-large-scale integration (VLSI): 1000 or more gates.

This chapter will primarily deal with SSI ICs, the basic digital building blocks. Microprocessors, memory chips and programmable logic devices are discussed later in the Computer Hardware section.

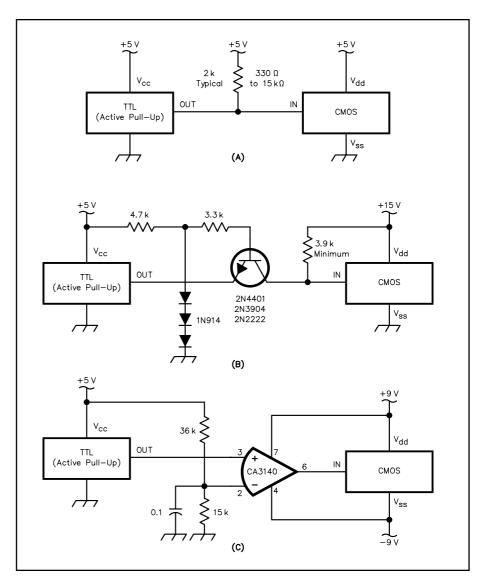

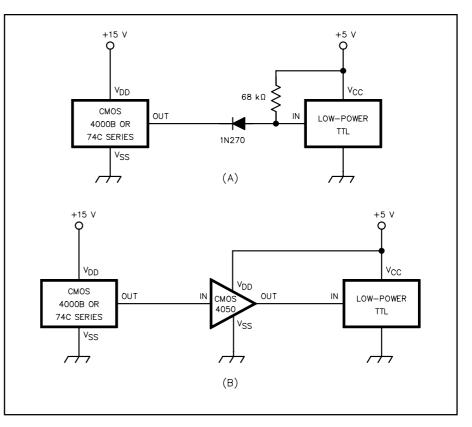

The previous section discussed the design of a digital circuit. To build that circuit, the designer must choose between IC chips available in various logic families. Each family and subfamily has its own desirable characteristics. This section reviews the primary IC logic families of interest to radio amateurs. The designer may also be challenged to interface between different logic families or between a logic device and peripheral device. The former is discussed at the end of this section; the latter with Computer Hardware, later in the chapter.

#### **COMPARING LOGIC FAMILIES**

When selecting devices for a circuit, a designer is faced with choosing between many families and subfamilies of logic ICs. Which subfamily is right for the application at hand is among several desirable characteristics: logic speed, power consumption, fan-out, noise immunity and cost.

#### Speed

Logic device families operate at widely varying clock speeds. Standard transistor-transistor logic (TTL) devices can only operate up to a few MHz while some emitter-coupled logic (ECL) ICs can operate at several GHz. Gate propagation delay determines the maximum clock speed at which an IC can operate; the clock period must be long enough for all signals within the IC to propagate to their destinations. ICs with capacitively coupled inputs have minimum, as well as maximum, clock rates. While the initial reaction may be to use the fastest available ICs, the designer must usually choose between a trade-off of high speed and low power consumption.

#### **Power Consumption**

In some applications, power consumption by logic gates is a critical design consideration. This power consumption can be divided into two parts: Dynamic power is the power consumed when a gate changes state. Static power is the power consumed when a gate is holding a state, either high or low. Each of these has different power requirements. Calculating the total required power can be a complex task when several gates and diverse functions are involved. Nominal power requirements, however, can be used to compare logic subfamilies.

#### Fan-out

Gate impedance is another parameter to consider. To deliver high current without dropping consid-

erable voltage, an ideal gate would have low output impedance. To draw minimal current, an ideal gate would have infinite input impedance. Such a gate does not exist. The designer must compromise on input and output impedances.

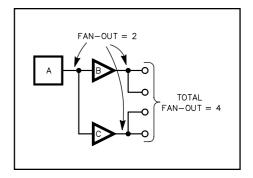

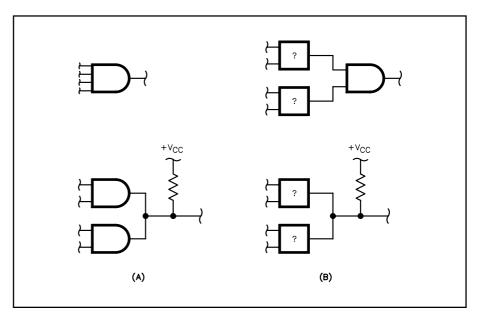

A gate output can supply only a limited amount of current. Therefore, a single output can only drive a limited number of inputs. The measure of driving ability is called fan-out, expressed as the number of inputs (of the same subfamily) that can be driven by a single output. If a logic family that is otherwise desirable does not have sufficient fan-out, consider using noninverting buffers to increase fan-out, as shown by **Fig 7.27**.

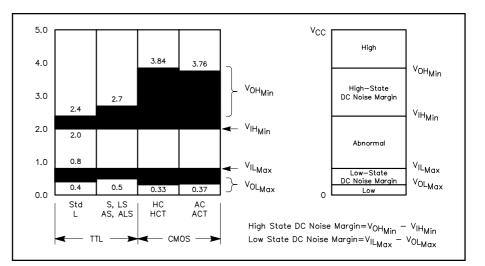

#### **Noise Immunity**

The noise margin was illustrated in Fig 7.2. The choice of voltage levels for the binary states determines the noise margin. If the gap is too small, a spurious signal can too easily produce the

Fig 7.27 — Nonverting buffers used to increase fan-out: Gate A (fan-out = 2) is connected to two buffers, B and C, each with a fanout of 2. Result is a total fan-out of 4.

wrong state. Too large a gap, however, produces longer, slower transitions and thus decreased switching speeds.

Circuit impedance also plays a part in noise immunity, particularly if the noise is from external sources such as radio transmitters. At low impedances, more energy is needed to change a given voltage level than at higher impedances.

#### **Other Considerations**

The parameters above are the basic considerations to influence the selection of a logic family for a specific application. These considerations have complex interactions that come into play in demanding low-current, high-speed or high-complexity circuits. Numerous other parameters can also be examined. These are provided in the electrical specification of a device. These are given on a data sheet and usually include four sections: (1) absolute maximum ratings specify worst-case conditions, including safe storage temperatures, (2) recommended operating conditions specify power-supply, input voltage, dc output loading and temperatures for normal operation, (3) electrical characteristics specify other dc voltages and currents observed at the inputs and outputs and (4) switching characteristics specify propagation delays for "typical" operation.

The list of parameters can seem overwhelming to the novice; but with experience, the important information will be more easily spotted. If you are designing a circuit, always consult the data sheet for specific information on the device you are considering, because these parameters vary not only between the logic families but also vary between the manufacturers and with changing technologies. Each manufacturer has data books available listing their devices and the corresponding data sheets.

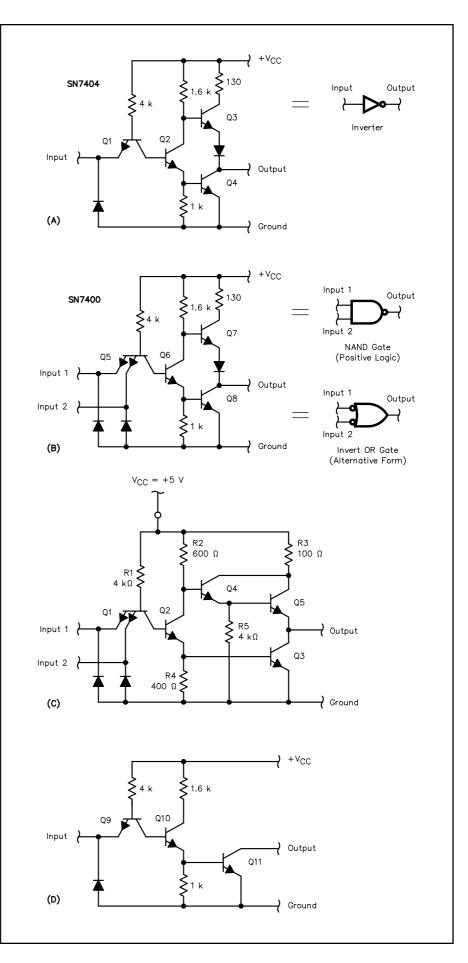

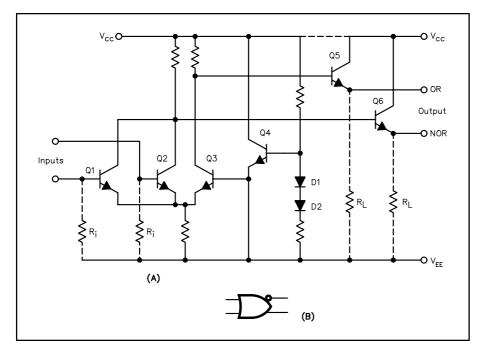

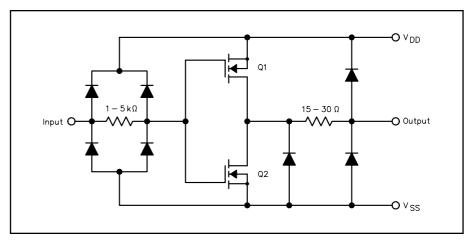

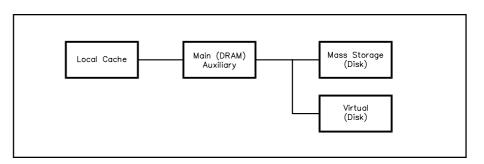

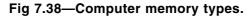

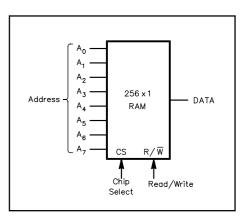

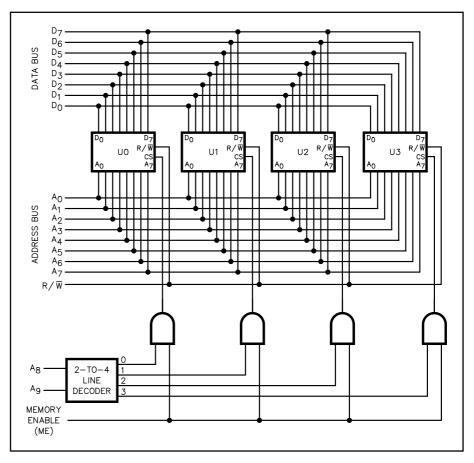

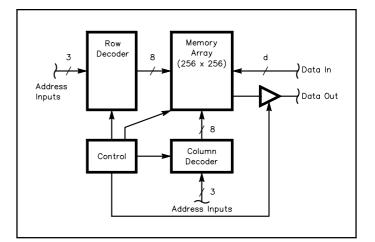

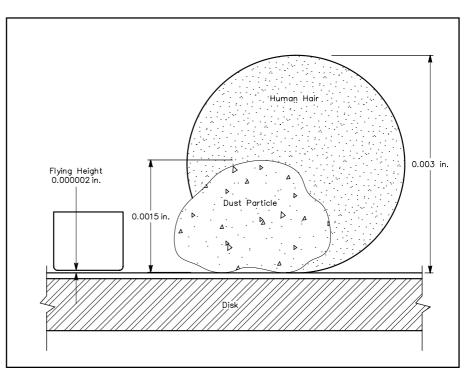

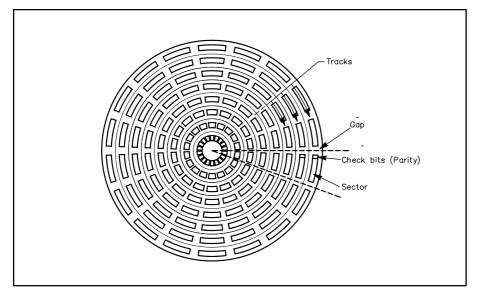

#### **BIPOLAR LOGIC FAMILIES**