# Chapter 16

# DSP and Software Radio Design

Digital signal processing (DSP) is one of the great technological innovations of the last hundred years. It has found a permanent place not only in radio, but also in the exploration for oil and other fossil fuels, high-definition television (HDTV),

compact-disc (CD) recording and many other facets of our lives. Its popularity stems from certain advantages: DSP filters do not need tuning and may be exactly duplicated from unit to unit; temperature variations are virtually non-existent; and DSP represents the ultimate in flexibility, since general-purpose DSP hardware can be programmed to perform many different functions, often eliminating other hardware. This chapter was written by Doug Smith, KF6DX.

### **DSP FUNDAMENTALS**

In this chapter, you will see that DSP is about rapidly measuring analog signals, recording the measurements as a series of numbers, processing those numbers, then converting the new sequence back to analog signals. How we process the numbers depends on which of many possible functions we are performing. We will take a look at some of those functions and explore how real DSP systems are implemented in software and hardware.

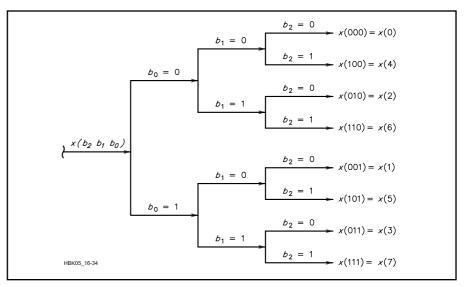

#### Sampling

The process of generating a sequence of numbers that represent periodic measurements of a continuous analog waveform is called *sampling*. Each number in the sequence is a single measurement of the instantaneous amplitude of the waveform at a sampling time. When we make the measurements continually at regular intervals, the result is a sequence of numbers representing the amplitude of the signal at evenly spaced times.

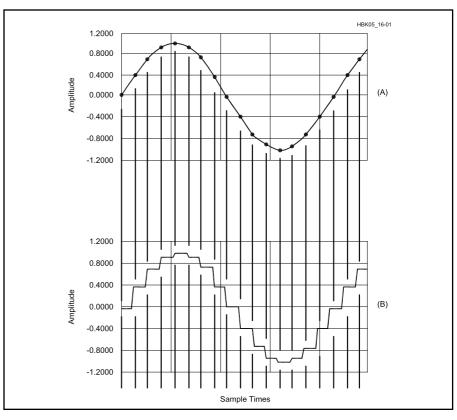

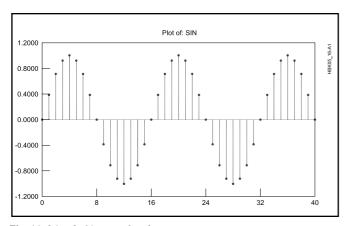

This process is illustrated in **Fig 16.1**. Note that the frequency of the sine wave being sampled is much less than the *sampling frequency*, f<sub>s</sub>. In other words, we are taking many samples during each cycle of

Fig 16.1—Sine wave of frequency much less than the sampling frequency (A). The sampled sine wave (B).

the sine wave. The sampled waveform does not contain information about what the analog signal did between samples, but it still roughly resembles the sine wave. Were we to feed the analog sine wave into a spectrum analyzer, we would see a single spike at the sine wave's frequency. Pretty obviously, the spectrum of the sampled waveform is not the same, since it is a stepwise representation.

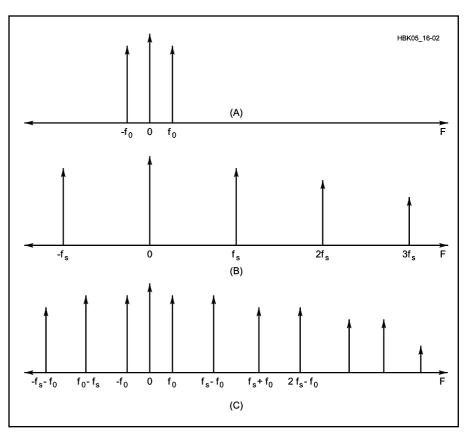

The sampled signal's spectrum can be predicted and interpreted in the following way. The analog sine wave's spectrum is shown in **Fig 16.2A**, above the spectrum of the sampling function in Fig 16.2B. The sampled signal is just the *product* of the two signals; its spectrum is the *convolution* of the two input spectra, as shown in Fig 16.2C. The sampling process is equivalent to a mixing process: They each perform a multiplication of the two input signals.

Note that the sampled spectrum repeats at intervals of  $f_s$ . These repetitions are called *aliases* and are as real as the fundamental in the sampled signal. Each contains all the information necessary to fully describe the original signal. In general, we are only interested in the fundamental, but let's see what happens when the sampling frequency is *less than* that of the analog input.

### Sine Wave, Alias Sine Wave: Harmonic Sampling

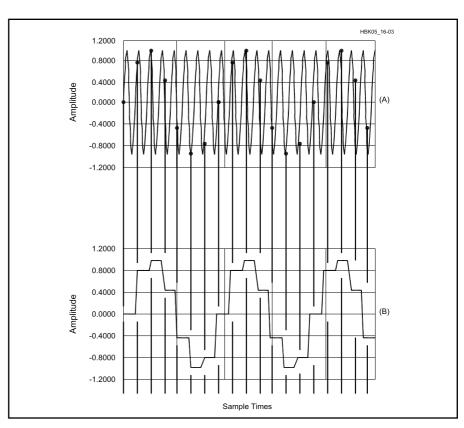

Take the case wherein the sampling frequency is less than that of the analog sine wave. See **Fig 16.3**. The sampled output no longer matches the input waveform. Notice that the sampled signal retains the shape of a sine wave at a frequency lower than that of the input. Ordinarily, this would not be a happy situation.

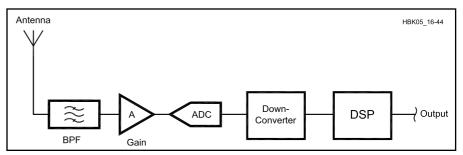

A downward frequency translation is useful, though, in the design of IF-DSP receivers. In addition, lower sampling frequencies are good because they allow more time between samples for signal processing algorithms to do their work; that is, lower sampling rates ease the processing burden. Caution is required, though: An input signal near twice the sampling frequency would produce the same output as that of Fig 16.3. To use this technique, then, we must first limit the bandwidth (BW) of the input: A band-pass filter (BPF) is called for. This is known as harmonic sampling. The BPF is referred to as an anti-aliasing filter.

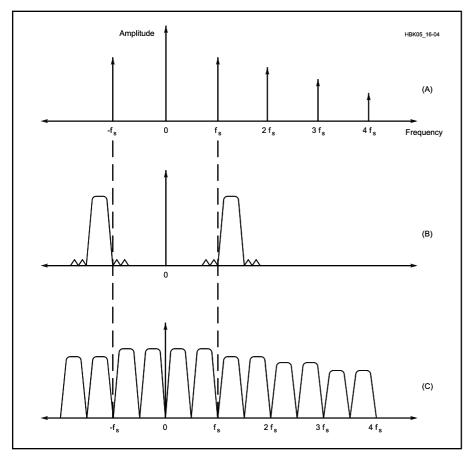

Input signals must fall between the fundamental (or some harmonic) of the sampling frequency and the point half way to the next higher harmonic. A frequency translation will take place, but no information about the shape of the input signal will be lost. A spectral representation of harmonic sampling is

Fig 16.2—Spectrum of an analog sine wave (A). The spectrum of a sampling function (B). The spectrum of the sampled sine wave (C).

Fig 16.3—Sine wave of frequency greater than the sampling frequency (A). Harmonically sampled sine wave (B).

Fig 16.4—Spectrum of a sampling function (A). Spectrum of a band of real signals (B). Spectrum of a harmonically sampled band of real signals (C).

shown in **Fig 16.4**. It reveals the basis for the often-misquoted *Nyquist sampling theorem*: The sampling frequency must be at least twice the input BW to avoid aliasing. Such aliasing would destroy information; once incurred, nothing can remedy it.

### **Data Converters and Quantization Noise**

The device used to perform sampling is called an *analog-to-digital converter* (ADC). For each sample, an ADC produces a binary number that is directly proportional to the input voltage. The number of bits in its binary output limits the number of discrete voltage levels that can be represented. An 8-bit ADC, for example, can only give one of 256 values. This means the amplitude reported is not the exact amplitude of the input, but only the closest value of those available. The difference is called the *quantization error*.

The amplitude reported by the ADC can, therefore, be thought of as the sum of two signals: the desired input and the quantization error. In a perfect ADC, the error cannot exceed  $\pm ^{1}/_{2}$  of the value of the least-significant bit of the converter—this is the error signal's peak-to-peak ampli-

tude. Assuming the desired input is changing and covers a large range of quantization levels, the error is just as likely to be negative as positive, and just as likely to be small as large. Hence, the error signal is pseudo-random and appears as *quantization noise*.

This noise is spread uniformly over the entire input BW of  $f_s/2$ . Taking this and the maximum signal the ADC can handle into account, the maximum signal-to-quantization-noise ratio produced by the ADC is:

$$SNR_{max} \approx 6.02b + 1.76 \, dB \tag{1}$$

where b is the number of bits used by the converter.

For a simple 16-bit ADC, the SNR cannot exceed about 98 dB. The reason we wrote that the quantization noise was pseudo-random and not truly random is the following: If there were a harmonic relationship between the input signal and the sampling frequency, the noise might tend to concentrate itself at discrete frequencies.

### **Aperture Jitter**

In addition to quantization noise, noise

is introduced in ADCs by slight variations in the exact times of sampling. Phase noise in the ADC's clock source, as well as other inaccuracies in the sampling mechanisms. produce undesired phase modulation of the sampled signal. Again, assuming it is uncorrelated with the input signal, this aperture jitter noise will be distributed across the entire input BW. Its amplitude is proportional to the squares of both the desired signal's frequency and the RMS time jitter in the sampling rate, and inversely proportional to the sampling rate itself. With contemporary crystal-derived clock sources, aperture jitter is usually not a significant factor until the sampling frequencies reach VHF; even at those frequencies, the effect may be small compared with quantization noise.

### Over-Sampling and Sigma-Delta ADCs

The nature of the above-mentioned noise sources is such that if we could increase the sampling frequency by some factor N, then digitally filter the output back down to a lower rate, we could improve the SNR by almost the factor N. This is because the noise would be spread over a larger BW; much of the high-frequency noise would be eliminated by the digital filter. This technique is called *over-sampling*.

So-called *sigma-delta* converters use this method to achieve the best possible dynamic range. They employ one-bit quantizers at very high speed and digital decimation filters (described later) to reduce the sampling frequency, thus improving SNR. They represent the state of the art in ADC technology. Other factors, such as the noise figure of analog stages inside an ADC, tend to limit the SNR of real converters to within a few dB of that calculated by Eq 1.

#### Non-Linearity in ADCs

The quantization steps of a real converter are not perfectly spaced; conversion results are contaminated by the inaccuracy. In general, two types of non-linearity are characterized by manufacturers: differential non-linearity (DNL) and integral non-linearity (INL).

DNL is the measure of the output nonuniformity from one input step to the next. It is expressed as the maximum error in the output between adjacent input steps as measured over the entire input range of the device. The worst errors usually occur near the middle of the scale. Since we are talking about the accuracy of the smallest steps the converter can resolve, noisy low-order distortion products caused by this effect limit dynamic range. Current technology uses correction systems to compensate for temperature variations that would otherwise further degrade performance.

An ADC is considered *monotonic* if a steady increase in the input signal always results in an increase in the output. Device manufacturers hold DNL to ±0.5 bits or better so that monotonicity is maintained.

INL is a measure of an ADC's large-signal handling capability. To measure it, we first inject a signal of amplitude A and measure the output; when we inject a signal of amplitude 100A, we expect the output to grow in exact proportion. INL represents the maximum error in the output between *any two* input levels. Another way to think about this is to plot the input against the output and see how straight the line is. INL produces harmonic distortion and IMD; values for typical converters are ±1 or 2 bits over the entire range.

### Spurious-Free Dynamic Range and Dithering

Spurious-free dynamic range (SFDR) is defined as the ratio of the largest signal the converter can accurately handle to the largest source of noise and distortion caused by effects mentioned above. Quite often, undesired components may appear in unexpected parts of the input spectrum; spurious responses may be found without apparent explanation. It turns out there are explanations, of course, but we will defer that discussion. Suffice it to write here that manufacturers test for SFDR and usually specify it on their data sheets, especially for high-speed devices.

Sometimes noise and distortion effects conspire to add at discrete frequencies. It is found that the addition of random noise at the clock input helps dissipate these spurious responses. This technique is known as *dithering*. It may seem strange, but artificial noise—usually several bits in amplitude and high enough in frequency to be eliminated by the decimation filter—actually reduces quantization noise and improves performance rather than degrading it.

### **Digital-to-Analog Converters: Additional Distortion Sources**

Digital-to-analog converters (DACs) perform the conversion of binary numbers back into analog voltages—the reverse operation of ADCs. They suffer from all the inadequacies described earlier, as well as a few of their own. The first unique distortion of DACs is one of frequency response: zero-order sample-and-hold distortion.

Typical converters are sample-and-hold devices: They continue to output the last sampled value throughout the sample period. This effect acts as a low-pass filter having a frequency response:

$$H_{r} = \frac{\sin\left(\frac{\pi f}{f_{s}}\right)}{\left(\frac{\pi f}{f_{c}}\right)} \tag{2}$$

Note the classical  $(\sin x)/x$  form. The high-frequency roll-off is quite undesirable in many circumstances. For example, if the output frequency is one quarter the sampling frequency, an attenuation of about 1 dB will occur. Correction can be made for this, but an increase in sampling frequency reduces the attenuation. Interpolation of the sampled output signal (described later) is called for in many cases.

### **Settling Time and Glitch Energy**

When the output of a DAC changes from one voltage to another, it obviously cannot do so instantaneously; a finite time is required for the voltage to reach its new value. This is known as the *settling time*. It is usually defined as the time required to settle to within some number of voltage-equivalent bits of the final value.

Glitch energy or glitch area is defined as the product of the voltage error during the settling time and the settling time itself. While volt-seconds are not units of energy, it is assumed the DAC is driving some kind of load; thus, these units can be translated into units of energy (watt-seconds), performing work on that load. The settling mechanism is an important factor in the production of spurious outputs in DACs. Manufacturers usually specify the glitch energy for their high-speed devices. It is an especially important number for direct-digital-synthesis (DDS) applications.

Note also that DACs produce aliases, again repeating at intervals of  $f_s$ . These must usually be removed using an analog LPF. Occasionally, a BPF may be used, and one of the aliases taken as the desired output. This can be a clever way of getting an upward frequency translation under certain conditions.

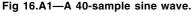

### Reducing the Sampling Frequency: Decimation

As we have seen, sampling at high rates is beneficial because it eases the design of the analog filters we must use to avoid aliasing. It also reduces quantization noise and aperture jitter. We have also noted that lower sampling rates help reduce the computational burden in DSP systems. In addition, we will discover that when it is time to digitally filter some signals, making the filter's BW a large fraction of the sampling frequency makes it easier to build sharp-skirted filters—exactly what DSP is famous for.

Reduction of the sampling frequency is

usually called *decimation*. Decimation is normally done by integer factors (although it does not have to be) and is equivalent to resampling an already-sampled signal at a lower rate. The resampled signal has a family of aliases, repeating at intervals of the lower sampling frequency; we have to reduce the BW to less than half this lower sampling frequency to avoid the aliasing that would destroy information.

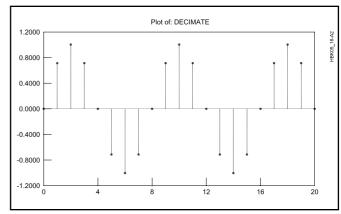

The process of decimation is simple: Just throw away the unwanted samples. To decimate by two, for example, only every other sample is retained. A decimation filter, operating at the higher sampling rate, f<sub>s</sub>, reduces signal BW to less than f<sub>e</sub>/4 prior to discarding the samples to avoid aliasing. But why spend time computing filter outputs that we are only going to discard? We may compute only those we intend to keep. This is exactly the same as running the decimation filter at the lower rate. This method is typical of those used by DSP designers to save time and effort. See the chapter Appendix for a software project (Project A) that demonstrates decimation using Alkin's PC-DSP program. This program is included with the book listed in the **Bibliography**.

### Increasing the Sampling Frequency: Interpolation

We learned that when it is time to convert back to analog, an artificial increase in sampling rate may be advantageous. It will push aliases higher in frequency where they are easier to remove by analog filtering, and it will relieve some of the sample-and-hold distortion. So, even having decimated the data at some earlier stage in our designs, we may later employ the process of *interpolation*.

Decimation was performed by deleting samples. Interpolation is performed by inserting them. The inserted samples have a value of zero and are placed between the existing samples. While this increases the sampling frequency, the information in the original samples is not destroyed; however, new information is added in the form of aliases, and an *interpolation filter* is usually required. This filter, most often a low-pass, operates at the higher sampling frequency, f<sub>s</sub>, and eliminates components in the interpolated data above half the original sampling frequency.

The way numbers are represented in DSPs is a major consideration. Let's take a look at this before moving on to filtering algorithms.

### Representation of Numbers: Floating-Point vs Fixed-Point

One of the things that makes generalpurpose computers so useful is their ability to perform *floating-point* calculations. In this form of numeric representation, numbers are stored in two pieces: a fractional part, or *mantissa*, and an exponent. The mantissa is assumed to be a binary number representing an absolute value less than unity, and the exponent, a binary integer. This approach allows the computer to handle a large range of numbers, from very small to very large. Some DSP chips support floating-point calculations,

but it is not as great an advantage in signal processing as it is in general-purpose computing because the range of values we are dealing with in DSP is limited anyway. For this reason, *fixed-point* processors are common in DSP.

A fixed-point processor treats numbers as just the mantissa and does away with the exponent. The radix point—the separation between the integer and fractional parts of a number—is usually assumed to reside to the

left of the most-significant bit. This is convenient, since the product of two fractions less than unity is always another fraction less than unity. The *sum* of two fractions, though, may be greater than unity: *overflow* would be the result. Overflow is a constant concern for fixed-point DSP programmers and leads to considerations for *scaling* of data, as discussed further below, which may limit system dynamic range to less than the data converters' capabilities.

### **DSP ALGORITHMS FOR RADIO**

### **Digital Filters**

The ability to construct high-performance filters is probably the most important rationale for using DSP in radio transceivers. An expensive crystal or mechanical filter having a single BW can be replaced by a set of superior digital filters, offering as many BWs as the associated on-board memory can support.

As shape-factor requirements get more stringent, filters get more complex. As a filter gets more complex—with additional inductors and capacitors in the analog case, or additional delay elements in the digital case—the sensitivity of the filter's response to errors in the element values becomes more severe. Thus, for analog filters, precise values of resistance, inductance and capacitance must be maintained if the filter is to operate as designed. Establishing those values is difficult; holding them within tolerances over temperature variations and aging is more so. DSP filters, on the other hand, are unchanging. The "component" values are numbers stored in a computer that are not susceptible to temperature

changes or aging. Filters that would be impractical or impossible in the analog realm are easily implemented by DSP algorithms.

We can build digital filters having linear phase responses, which is very difficult in the analog world. This is an advantage mainly for digital communication modes such as FSK and PSK. Also, filters may be combined numerically to yield composite responses without the need for adding hardware. This is useful for passband tuning or graphic-equalizer applications.

DSP filters are usually characterized by their *impulse responses*. The impulse response of a digital filter is the output of the filter when the input is a one-sample, unity-amplitude impulse. Impulse response is directly related to frequency response by a *Fourier transform*, about which we will learn more later. Suffice it to write for now that digital filters may be broadly divided into two classes: finite impulse response (FIR) and infinite impulse response (IIR). The presence or ab-

sence of feedback separates the two.

#### **FIR Filters**

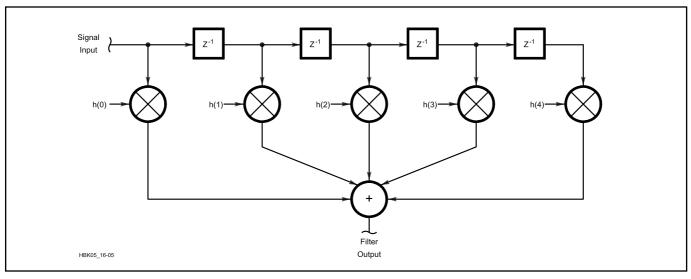

Take a look at the block diagram of the FIR filter shown in **Fig 16.5**. The string of boxes labeled z<sup>-1</sup> is simply a delay line, with each box representing a one-sample delay. Programmers will note that with one input sample in each position, this is just a buffer of length five. Each buffer location may be referred to as a tap in the delay line. The datum at each tap, x(n), is multiplied by one of the filter coefficients, h(n). All the products are summed at each sample time to produce the filter output. At the next sample time, samples are shifted down the delay line by one position and the multiply-and-accumulate (MAC) operation is performed again. Coefficients remain in place and do not shift. The mathematical expression describing this repetitive MAC operation is also called a convolution sum:

$$y(k) = \sum_{n=0}^{L-1} h(n) x(k-n)$$

(3)

Fig 16.5—Block diagram of an FIR filter for L = 5.

where x(k-n) represents the input data in the buffer.

Since the output depends only on past input values, the filter is said to be a causal process. Since no feedback is employed, it is unconditionally stable.

In an FIR filter, the set of coefficients. h(n), is identical to the impulse response of the filter. The trick, then, is to find the impulse response that gives us the frequency response we want. Almost any frequency response can be generated if we use enough taps. In general, low shape factors (steeper roll-offs) require more taps. Most filter-design methods begin with an estimate of the number of taps needed. Rabiner and Gold indicate the estimate may be taken as:

$$L = 1 - \frac{10 \log \left(\delta_1 \delta_2\right) - 15}{14 \left(\frac{f_T}{f_s}\right)} \tag{4}$$

where  $\delta_1$  is the passband ripple,  $\delta_2$  is the stopband attenuation, f<sub>T</sub> is the transition BW (the bandwidth between the edge of the passband and the edge of the stopband (ie, the filter skirt), f<sub>o</sub> is the sampling frequency, and L, the number of taps, is called the length of the filter. This equation assumes that enough bits of resolution are used to achieve the required accuracy. In practice, filters of over 100 taps are used to realize shape factors of less than 1.15:1.

Normally, an FIR filter's impulse response has a symmetry about center; that is, h(0) = h(L-1), h(1) = h(L-2), and so forth. It turns out this is sufficient to ensure a linear phase response and flat groupdelay characteristics. The total delay through an FIR filter of length L is:

$$t = \frac{L}{2f_s} \tag{5}$$

As noted, this delay is independent of frequency. Remember that longer filters demand more processing than shorter filters.

When personal computers are used to design FIR filters, coefficients are usually represented in floating-point format to the full accuracy of the computer-often with 12 or more decimal digits in the mantissa. Embedded, fixed-point DSP implementations ordinarily achieve only 16-bit accuracy. The truncation of coefficients and data to this accuracy affects the frequency response and ultimate attenuation of filters, and may be the factor that determines dynamic range. Also notice that when we multiply a 16-bit coefficient by a 16-bit datum, the product is a 32-bit number. We are then adding several 32-bit numbers in the final accumulator of an FIR filter. The result may grow by several more bits to 35 or so by the time we are done. At some stage, the result may overflow the accumulator, especially in FIR filters with small transition BWs (sharp skirts). The worst-case output can grow as large as the sum of the absolute value of all the coefficients:

$$y_{\text{max}} = \pm \sum_{n=0}^{L-1} |h(n)|$$

(6)

We might have to scale the data, the coefficients, or both by the reciprocal of this number to avoid overflow.

The filter output at each sample time is usually rounded back down to the bit-resolution of the DAC; say, to 16 bits. The rounding operation introduces a small error in the result. This rounding error is directly analogous to quantization noise; it is computed in almost exactly the same way. A trade-off exists between the possibility of overflow, which is catastrophic, and loss of accuracy because of rounding. It is interesting to note that truncation of filter coefficients affects the frequency response of the filter but not the amount of noise in the output. On the other hand, truncation and rounding of data do not affect the frequency response but add quantization noise to the output.

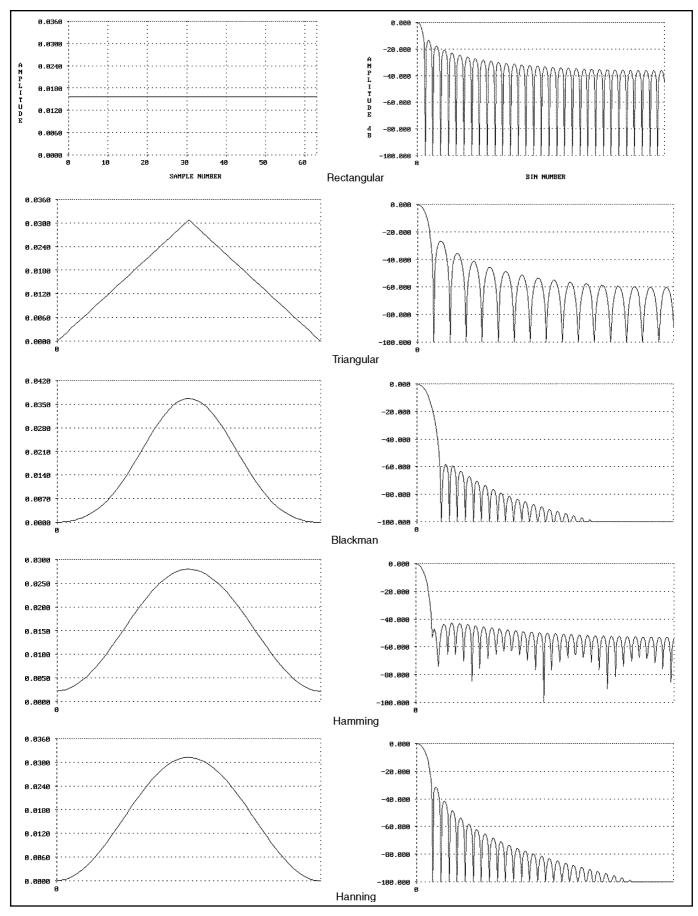

One FIR filter-design approach takes advantage of the fact that a filter's frequency response is the Fourier transform of its impulse response. Thus, we may start with a sampled version of the frequency response and apply an inverse Fourier transform to obtain the impulse response. All filter-design software is capable of using this method. Better designs may be obtained in many cases by using an algorithm developed by Parks and McClellan. This approach produces an equi-ripple design in which all of the passband ripples are the same amplitude, as are all the stopband ripples. Another popular algorithm is the *least-squares* method. Its claim to fame is that it minimizes the error in the desired frequency response.

Since finding coefficient sets for a given filter design is so computationally intensive, it is a good job for a computer program. DSP filter-design programs are readily available at low cost. Refer to the DSP System Software section toward the end of this chapter for further discussion of filter design and the **Bibliography** for a list of software design tools. The article by Kossor has a practical circuit example of a commutating BPF that employs principles of DSP. Also see Project B in the chapter Appendix for examples of FIR filter designs.

#### **IIR Filters**

While FIR filters have a lot going for them, they tend to require a large number of taps and a proportional amount of processing power. As opposed to that, an IIR (infinite impulse response) filter can provide sharp transition BWs with relatively few calculations. What it will not provide, in general, is a linear phase response. In circumstances where the computational burden is of more concern than the phase response, IIR filters may be desirable.

Unlike FIR filters, IIR filters employ feedback: That is what makes their impulse responses infinite. For this reason, IIR filters are usually designed by converting traditional analog filter designs, such as Chebyshev and elliptical types. See the **RF** and **AF** Filters chapter of this book for a description of those designs. The transfer function of an analog Chebyshev low-pass filter can be written as the ratio of a constant to an nth-order polynomial:

$$H_S = \frac{K}{a_0 s^n + a_1 s^{n-1} + a_2 s^{n-2} + \dots + a_n s^0}$$

(7)

Tables in the literature, such as in Zverev, list the values of the coefficients, a<sub>n</sub>, related to the cutoff frequency; these are used to derive actual component values for the filter. The low-pass design can be transformed to band-pass or band-stop responses. Two popular methods exist for deriving the digital transfer function from the analog: These are known as the impulse-invariant and bilinear transform methods.

The impulse-invariant method assures that the digital filter will have an impulse response equivalent to its analog counterpart, and thus the same phase response. Problems arise, though, if the bands of interest are near half the sampling frequency; the digital filter's response can develop serious errors in this case. Because of this problem, the impulse-invariant method is not as good as the bilinear transform method. As indicated by Sabin and Schoenike, the bilinear transform method makes a convenient substitution for s in Eq 7 above. The filter output comes

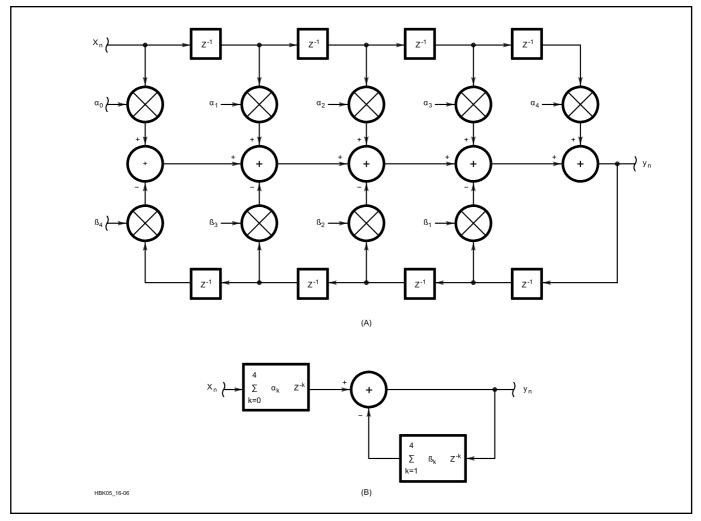

$$y(k) = \sum_{n=0}^{L-1} \alpha(n) x(k-n) - \sum_{n=1}^{L-1} \beta(n) y(k-n)$$

(8)

This filter has L zeros and L-1 poles. The block diagram of such a filter for L =5 is shown in Fig 16.6. Feedback is evident in the diagram: The paths involving coefficients \( \beta \) loop back and are added to

Fig 16.6—Block diagram of an IIR filter for L = 5.

Fig 16.7—Block diagram of a cascade-form IIR filter.

the signal path.

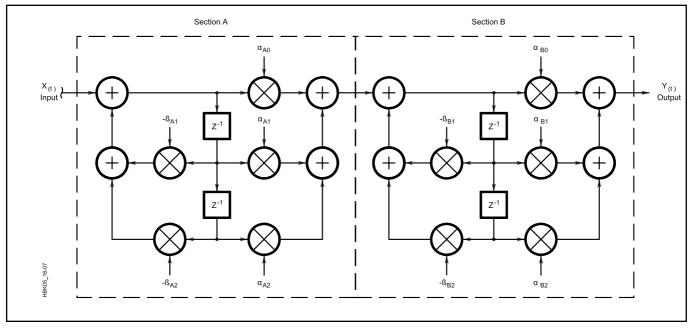

The direct form of Eq 8 may be factored into 2-pole sections and implemented in cascaded form. The output of each section serves as the input to the next. See Fig 16.7. This configuration requires a few more multiplications than the direct form, but suffers less from instability problems that may plague IIR filters. Since feedback is being used, IIR filters are not necessarily unconditionally stable. They also tend to be prone to limit cycles, low-level oscillations that arise near the lower end of the dynamic range. For these and other reasons, data and coefficient storage should be cleared or set to zero before processing begins.

### A Simple Digital Notch Filter

Along with common LPFs, HPFs and BPFs, radio designers are interested in one other type of filter, the *notch*. While most filter-design software can generate notch filters using FIR methods discussed above, Widrow and Stearns have described an unusual type in which the number of taps is minimized. In fact, they were able to prove that only two taps are needed for each frequency to be notched. This is great, since it reduces computation to almost nil. We will

take a look at it here and touch briefly on some of the theory of *adaptive signal processing*, treated in depth later.

The situation is this: We want to copy a broadband signal, such as an SSB phone signal, and suddenly a dreadful carrier appears in the passband. Our notch filter will remove it and we will have complete control over the notch width, as well as a notch depth limited only by the bit resolution of our system. Dr Widrow found that one can build a filtering system that minimizes repetitive signal energy by altering the filter coefficients "on the fly" using a certain algorithm. Known as the leastmean-squares (LMS) method, it describes a way to adjust filter coefficients over time to remove undesired, steady tones in the input. A complex reference signal is used at the exact frequency of the offending tone. The algorithm then forms a BPF centered at the tone frequency whose output is subtracted from the input to create the notch. The block diagram of a two-tap system is shown in **Fig 16.8**.

The broadband input is called x(t). The reference input consists of two signals, cos  $(\omega_0 t)$  and sin  $(\omega_0 t)$ . These signals feed multipliers having coefficients h(1) and

$\begin{array}{c} \text{Notch} \\ \text{Output} \\ \text{e(t)} \\ \text{BPF} \\ \text{Output} \\ \text{y(t)} \\ \\ \text{Cos}(\omega_0 t + \varphi) \\ \\ \text{d(1)} \\ \\ \text{h(1)} \\ \\ \text{h(2)} \\ \\ \text{HBK05\_16-08} \\ \\ \end{array}$

Fig 16.8—Block diagram of a two-tap, adaptive notch filter.

h(2), which in turn feed an accumulator just as in a normal FIR filter. This is the BPF output; it is subtracted from the input to form the notch output, e(t). Note that the BPF output is also available at no additional overhead. While the initial values of the coefficients are unimportant to the steady state, the procedure for updating them with the LMS algorithm is:

$$h_{t+1}(1) = h_t(1) + 2\mu e(t)x_t(1)$$

$$h_{t+1}(2) = h_t(2) + 2\mu e(t)x_t(2)$$

(9)

where  $0 < \mu < 1$ . Analysis shows that as the reference inputs are sinusoidal, the system is linear and time-invariant for output e(t), although the coefficient values do not necessarily approach any fixed value. The 3-dB BW of the notch is:

$$BW = \frac{2\mu A^2}{t_s} \text{ rad/s}$$

(10)

The Q of the filter may be readily computed. Thus, we have control over the BW by varying the factor  $\mu$  and the amplitude of the reference signal. The depth of the null is, in general, superior to that of a fixed filter because the algorithm tracks the correct phase relationship for ideal cancellation, even if the reference frequency is changing slowly with the offending tone. Each additional tone to be notched demands two additional taps in the filter. Noise in the input may cause us to have to add more taps to maintain sufficient accuracy. Additional detail of adaptive signal processing will be found below and in material shown in the Bibliography.

#### **Lattice and Other Structures**

While many filter-design software packages do not have the capability to work with them, lattice structures and other types of digital filters have seen use, especially in adaptive signal processing. Crystal and mechanical lattice filters are common elements of many transceivers. A digital lattice or ladder filter is a lot like its analog brother. The design of digital lattice filters is similar as well. Digital lattice filters may be either FIR or IIR. Also note that from the IIR cascade form above, we can derive a parallel form that may be computationally beneficial in some cases. The design of this kind of filter is a very complicated session in partial fraction expansion. Widrow and Stearns provide more information on these and other exotic concepts.

### **ANALYTIC SIGNALS AND MODULATION**

DSP implementations of transceiver functions, such as modulation and demodulation, compel designers to examine the mathematics behind them. Computers are good at crunching numbers, but they do exactly what they are told! If we expect a DSP system to generate an SSB signal, for example, we had better know which calculations to perform and which to avoid.

### **Mathematics of Complex Signals**

Because DSP makes it easy to build frequency-independent phase shifters—a fantasy in the analog world—the phasing or "I/O" method has dominated other modulation techniques. Complex signals are not generally well understood and quite often form a stumbling block to those wishing to grasp DSP concepts. The idea of negative frequency is especially troublesome. The key to understanding these concepts lies in the theory of complex numbers. A real signal, such as a cosine wave, is normally thought of as a positive frequency. It can be transmitted and detected normally; however, we shall see that such a signal actually consists of positive and negative frequencies when examined in the complex domain.

A real cosine wave embodies the relation:

$$x(t) = \cos(wt) \tag{11}$$

where  $\omega = 2\pi f$  and t is time. In the complex domain, the cosine wave is really the sum of two complex signals:

$$x(t) = \frac{1}{2} \left\{ \begin{bmatrix} \cos(\omega t) + j\sin(\omega t) \end{bmatrix} + \\ \begin{bmatrix} \cos(\omega t) - j\sin(\omega t) \end{bmatrix} \right\}$$

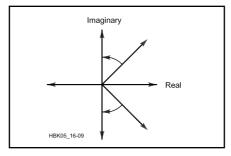

posite directions. See Fig 16.9.

This signal has both positive and negative frequency components. The real parts add and the imaginary parts cancel to make the equation true. In the complex plane, where the real part is one axis and the imaginary part the other, this signal can be represented as two vectors rotating in op-

(12)

While this depiction is beautiful and elegant to the mathematician, what does it really mean to you and me? Well, it means that signals represented in complex form can have a one-sided spectrum—that is, only a positive or a negative frequency component. This is useful as we mix our signals upward to their final frequency positions in a modulator.

As our first example, let's select the task of taking a real input signal, such as the

audio from a microphone, and converting it to an SSB signal that can be transmitted. We obviously have to translate the audio signal upward in frequency and preserve its spectral content within the band we want the transmitted signal to occupy. If we wish to produce an upper-sideband (USB) signal, we want the carrier and lower sideband to be suppressed as much as possible. Were we able to translate the spectrum of our cosine wave—with its symmetrical positive- and negative-frequency components—upward in frequency far enough, we would have two

Fig 16.9—Vector representation of a real cosine wave.

Fig 16.10—Hilbert transformer producing an analytic signal.

positive frequencies separated by twice the original signal's frequency. For a real signal, this is exactly what happens when it is applied to an analog mixer: Both sum and difference frequencies are generated. See the **Receivers, Transmitters and Transverters** chapter for more detail of the operation of mixers as multipliers.

To move our sampled audio signal upward in frequency, we must multiply it by (mix it with) a local oscillator. The local-oscillator function can be implemented in DSP software using direct digital synthesis (DDS) techniques. In this case, though, the local oscillator must be complex; that is, it must have two outputs with a 90° phase relationship between them. This is the same as saying there must be both a sine and a cosine output from it. This will enable us to mix signals having a one-sided spectrum.

When we implement a complex mixer in DSP, we are multiplying complex numbers by complex numbers. Note that the calculations for the real and imaginary parts are carried out separately; each part is treated as if it were a single, real multiplication. Two complex numbers a + j b and c + j d, when multiplied, produce:

$$(a + j b)(c + j d) = (ac - bd) + j (ad + bc)$$

(13)

Four real multiplications and two real additions are required.

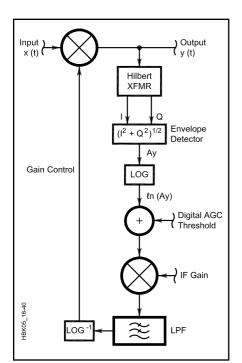

### Hilbert Transformers and an SSB Modulator

If we want to create a signal having a one-sided spectrum from a real input signal, such as from the microphone, we need to shift all the frequency components in

Fig 16.11—Block diagram of a half-complex mixer.

the sampled signal by  $90^{\circ}$ . Fortunately, in DSP, we have a way to do that: the *Hilbert transformer*. Recall that an FIR filter with a symmetrical impulse response exhibits a constant, frequency-independent delay. It turns out a filter with an *anti-symmetrical* impulse response—that is, with h(0) = -h(L-1), h(1) = -h(L-2), and so forth—produces a linear phase response, too, but with a phase response exactly  $90^{\circ}$  different from the symmetrical-impulse-response filter. This is exactly the type of filter we need to generate the components of an *analytic signal*.

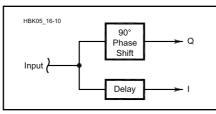

Fig 16.10 shows a system using a

Hilbert transformer to create an analytic signal from the microphone audio. Since the Hilbert transformer includes not only a  $90^{\circ}$  phase shift, but also a fixed delay of L/2 sample periods, we need an L/2 delay in the leg that does not contain a phase shift. The delay through the two paths is then equal and the only difference between the two signals produced is the  $90^{\circ}$  phase shift. The non-phase-shifted signal is called I, the phase-shifted signal is called Q. Together, these signals form our analytic signal I + j Q. Now let's see what it looks like when we multiply this signal by a complex local oscillator. In this case, we

are performing the multiplication:

$$\begin{aligned} & \left[\cos(\omega t) + j\sin(\omega t)\right] \left[I(t) + jQ(t)\right] = \\ & \left[I(t)\cos(\omega t) - Q(t)\sin(\omega t)\right] + \\ & j\left[I(t)\sin(\omega t) + Q(t)\cos(\omega t)\right] \end{aligned} \tag{14}$$

This is the equation for a USB signal. We are only interested in the real part of the result, since we only have one real channel on which to transmit. For this reason, the system is really a half-complex mixer.

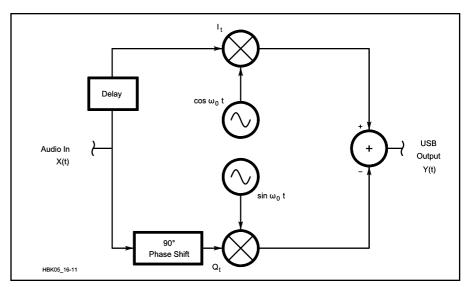

A block diagram of such a mixer is shown in **Fig 16.11**. This is, in fact, the phasing

Fig 16.12—Block diagram of a digital SSB modulator.

Fig 16.13—Block diagram of a digital ISB modulator.

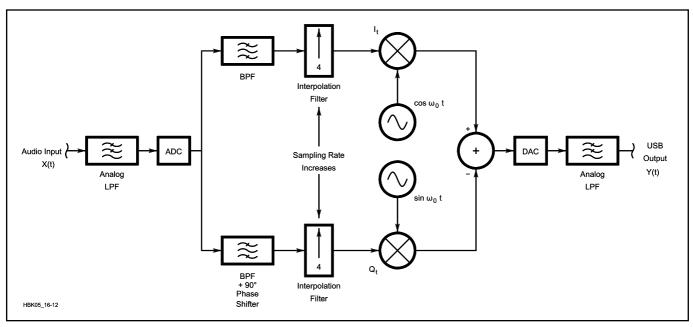

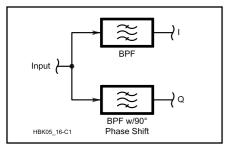

method. Output signals are translated upward by the frequency of the local oscillator,  $\omega_0$  radians per second, or  $\omega_0/2\pi$  hertz. Most transmitter designs will translate signals to an IF significantly higher in frequency than audio, so it is wise to include an increase in the sampling rate prior to mixing. An interpolation filter is naturally needed. It is particularly convenient to choose an interpolation factor of 4, because the cosine LO produces values of 1, 0, -1and 0 during a full cycle; the sine LO produces values of 0, 1, 0 and -1. No actual multiplications need take place, saving time and accuracy. The Hilbert transformer can operate at the lower, original sampling rate, but we would like to include bandpass filtering to limit the spectrum to about 3 kHz BW. In fact, we can build a pair of DSP filters that provide the BPF response and the 90° phase relationship, as described below. Our SSB modulator then matches that shown in Fig 16.12.

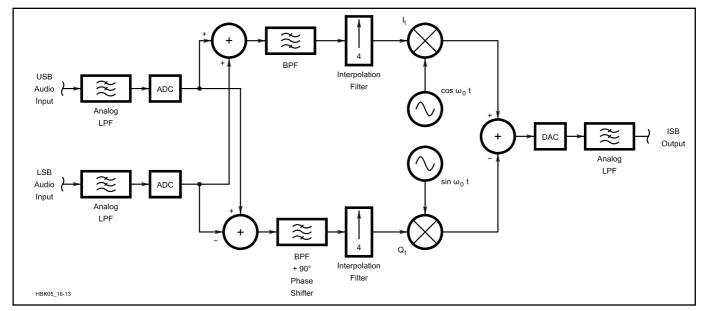

Before discussing how to generate analytic filter pairs, it is worth noting a few properties of SSB signals created in this way. First, were we to add the I and Q signals instead of subtract them in the summation block of Fig 16.11, we would have an LSB signal instead of USB. It is not too hard to see that we could easily both add and subtract to produce a DSB, suppressed-carrier signal. We can even pre-add and subtract *two* audio signals to produce an independent-sideband (ISB) signal, as shown in **Fig 16.13**. More than two channels can be combined in this way. Second, since the amplitude of the carrier,  $\cos(\omega_0 t) \pm j \sin(\omega_0 t)$ ,

is constant, the amplitude of an SSB signal can be specified as some function of the modulating signal. If we think of the analytic audio signal as a vector in the complex plane, its length is equal to the signal's instantaneous amplitude:

$$A(t) = \left[I^{2}(t) + Q^{2}t(1)\right]^{1/2}$$

(15)

Finally, the phase of the signal is the instantaneous angle of this rotating vector:

$$\phi(t) = \arctan\left[\frac{Q(t)}{I(t)}\right]$$

(16)

Now we can rewrite the real part of Eq 14 as:

$$y(t) = A(t)\cos\left\{\left[\omega + \frac{d\phi(t)}{dt}\right]t\right\}$$

(17)

$\frac{d\phi(t)}{dt}$  is the rate of change of phase (the frequency) of the baseband signal (the audio). Eq 17 shows that a USB signal is just an upward frequency translation of the baseband signal by some RF of angular frequency  $\omega$ . We may also write:

$$[I(t) + j Q(t)] = A(t) \{\cos[\phi(t)] + j \sin[\phi(t)]\}$$

(18)

which shows that while the envelope, A(t), of an SSB signal is identical to that of the baseband signal producing it, A(t) is not the same as the baseband signal's waveform,

represented by x(t) in Figs 16.11 and 16.12. An SSB signal preserves the amplitude and phase information of the baseband signal and occupies identical bandwidth.

### **Analytic Filter-Pair Synthesis**

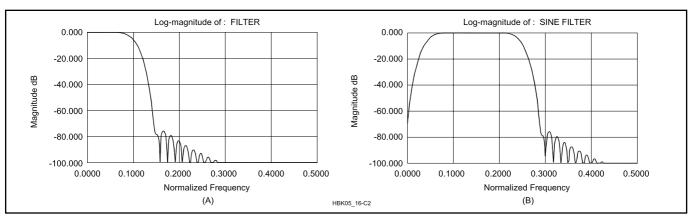

We have seen how complex mixing translates signals in frequency with a one-sided spectrum. We will use this fact to our advantage in creating an analytic filter pair. Each filter will have the same frequency response as the other. They will differ only in their phase responses.

We begin by designing a low-pass filter having the desired transition-band characteristic,  $H(\omega)$ ; we obtain its impulse response, h(t). Multiplying the impulse response by a complex sinusoid of angular frequency  $\omega_0$  results in two sets of coefficients—one for the real part, and one for the imaginary part:

$$h_{I}(t) = h(t)\cos(\omega_{0}t)$$

$$h_{O}(t) = h(t)\sin(\omega_{0}t)$$

(19)

The frequency response of either one of these filters is given by:

$$H_{\omega} = \frac{H_{(\omega - \omega_0)} + H_{(\omega + \omega_0)}}{2} \tag{20}$$

which is a BPF centered at  $\omega_0$ . The I filter has a phase response differing 90° at every frequency from the Q filter. The frequency translation theorem works just as well on the responses of filters as it does on real signals. To perform this transformation of the L co-

Fig 16.14—Block diagram of a digital SSB demodulator.

Fig 16.15—Block diagram of a digital AM demodulator.

efficients of the prototype LPF, we calculate new coefficients according to:

For  $0 \le k \le L - 1$ ,

$$\begin{aligned} h_{I}(k) &= h(k)\cos\left[\omega_{0}\left(k - \frac{L}{2} + \frac{1}{2}\right)t_{s}\right] \\ h_{Q}(k) &= h(k)\sin\left[\omega_{0}\left(k - \frac{L}{2} + \frac{1}{2}\right)t_{s}\right] \end{aligned} \tag{21}$$

where  $t_s$  is the sampling period. When the low-frequency transition band is placed near zero frequency, as we would like for SSB, the BW of each BPF is approximately twice that of the prototype LPF. A very interesting thing sometimes happens when the number of taps is odd: The odd-numbered coefficients are zero. This allows reduction in computation by a factor of two. Refer to Project C in the **Appendix** for a practical example of how analytic filter pairs are generated.

We can alter the exciter's frequency response by convolving the impulse response of our analytic filter pair with that of a filter having the desired characteristic. New coefficients are calculated using the same convolution sum as in Eq 3. Graphic or parametric equalizers may be implemented in this way.

### **Demodulation: SSB**

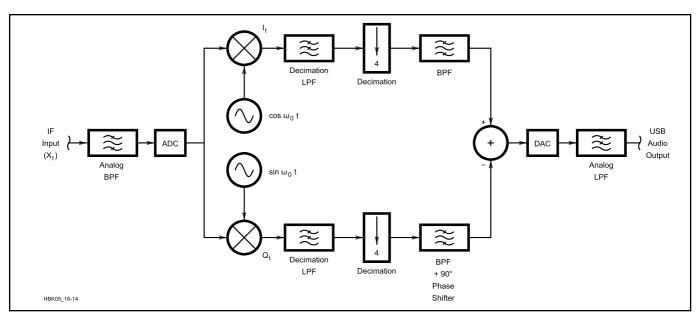

As in digital exciters, phasing methods prevail in receivers; the process is almost exactly the reverse of the modulator's. Fig 16.14 presents the block diagram of a digital SSB receiver. After the IF signal is

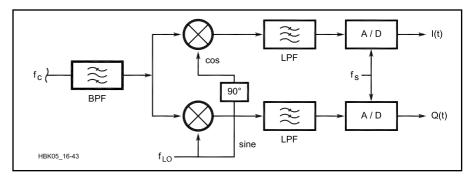

digitized, we wish to reduce the sampling rate and the filtered BW as soon as possible. This is because we need as much time as possible between input samples for the intense filtering and other computations we must perform. As noted above, reduced sampling rates also ease the design of the digital filters that provide the final selectivity. We therefore include a decimation filter and decimate by a factor of 4. Again, the LO signals take on only values of 1, 0, -1 and 0, eliminating multiplications. Digitized signals are translated to baseband using the complex mixing algorithms outlined above. Since the input signal, x(t), is real, only two multiplications are necessary:

$$I(t) = x(t)\cos(\omega t)$$

$$Q(t) = x(t)\sin(\omega t)$$

(22)

Now we have an analytic signal as before; the frequency of the BFO,  $\omega_0$  rad/s, is chosen to beat the carrier frequency to zero hertz. An analytic filter pair precedes the summation in which we select the sideband we want. The equations work precisely in reverse: That is why they are Hilbert transforms.

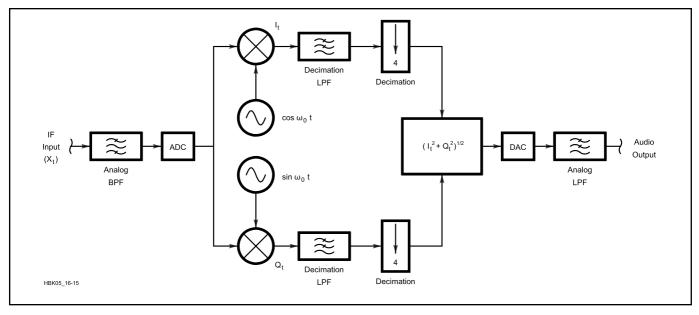

#### **AM Demodulation**

One's first inclination is to demodulate an AM signal by rectifying it. A better way is to use the I and Q signals we have already developed using Eq 15. Now we are stuck with computing square roots. Lucky for us, a fellow named Isaac Newton figured out a slick way almost 400 years ago. In the 17<sup>th</sup> century, these calculations were

Fig 16.16—Flow chart of a fast square-root algorithm.

quite a burden—everything had to be done by hand. Because this is such a common problem in computing, a lot of additional effort has gone into finding faster algorithms since that time. A very fast lookup-table method is also presented here that may be more attractive where enough memory is available.

An I/Q AM demodulator dodges problems associated with rectification methods. It also can use the decimation filters for final selectivity, obviating much of the computations found in the SSB demodulator. Fig 16.15 shows the circuit. Newton's method for square roots goes like this: Take a crude guess at the square root of the number in question. Divide the number by the crude guess. Add the crude guess to this ratio and divide it all by 2. Use this result as the new crude guess and repeat the process until the desired accuracy is obtained:

$$let GUESS_{new} = \left(\frac{\frac{Number}{GUESS_{old}} + GUESS_{old}}{2}\right)$$

$$let GUESS_{old} = GUESS_{new}$$

REPEAT (23)

In practice, the accuracy of the result reaches the limit of 16-bit representations in five or six iterations when the first guess is good. It is about half an order of magnitude slower than the following look-up table method, but is still among the best where memory is at a premium. Project D in the **Appendix** describes a *QuickBasic 4.5* example of Newton's method.

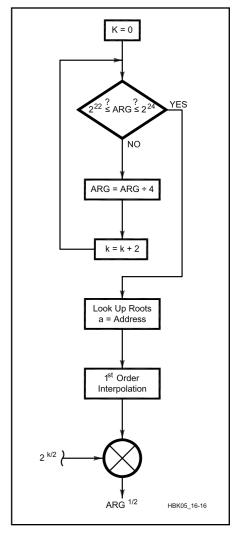

A very fast look-up-table method for computing integer square roots has been discovered. It employs a short (256-entry) table and first-order interpolation between table entries. First-order interpolation is described in detail in the DDS section below. To preserve accuracy, the algorithm also uses the process of argument normalization. The algorithm serves as our fifth software project in DSP in the **Appendix**.

The argument of this function—the number of which we must find the square root—is a 32-bit integer. The result is a 16-bit integer. Refer to **Fig 16.16**, a flow chart of the process. In the first step, the argument is normalized to within the range  $2^{22}$ - $2^{24}$ . Arguments greater than  $2^{24}$  are divided by an even integral power of two,  $2^k$ , where:

$$k = \Im[\log_2(\arg) - 23] \tag{24}$$

The script I indicates the integer part, and k—which takes on values of 0, 2, 4 or 6—is saved for later processing. Now the normalized argument is split into integer

Fig 16.17—Block diagram of a synchronous, exalted-carrier demodulator.

and fractional parts, with the radix point residing to the left of bit 15:

$$a = \Im\left(\frac{\arg}{2^{k+8}}\right)$$

$$b = \mathcal{F}\left(\frac{\arg}{2^{k+8}}\right)$$

(25)

where a is the integer part and b is the fractional part. In other words, a comprises bits 16-23 of the normalized argument, and b is bits 0-15, as shown in the flow chart. Next, we use a as the address into the look-up table, fetching a 16-bit value,  $x_a$ . This value is the nearest table entry lower than the actual root. Fractional part b is used to interpolate between this value and the next higher table entry,  $x_{a+1}$ :

root =

$$b(x_{a+1} - x_a) + x_a$$

(26)

This is the square root of the normalized argument.

Finally, this result must be multiplied by the square root of 2k, which is of course  $2^{k/2}$ . The result is then "de-normalized" and ready for use. Restricting k to an even integer (as we did) makes this a simple bit-shifting operation, as in the normalization process above. The 16-bit result produced by this algorithm is accurate to within several least-significant bits over the entire range of 32-bit arguments. It is quite a bit faster than the 5 or 6 iterations of Newton's method required for the same accuracy; this is because it avoids the divisions that Newton's method employs. Most DSPs take 3 or 4 times the processing time for a fractional division as they take for multiplication or look-up table indexing. Project E in the Appendix describes an assembly-

Fig 16.18—Block diagram of a digital quadrature detector.

language implementation of this square-root algorithm.

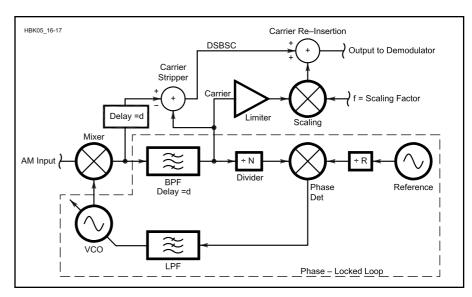

Additional threshold extension and distortion-avoidance procedures may be employed in an AM demodulator. Of particular interest is the synchronous, exalted-carrier demodulator. Synchronous, in this case, means that the demodulator's frequency standard is phase-locked to the received carrier. This forces the phases of modulation components into their correct relationships and therefore minimizes phase distortion. A small advantage in SNR performance of up to 3 dB is also gained. DSP makes it relatively easy to build a narrow BPF, centered on the carrier, that strips the modulation prior to application to the PLL used to achieve lock. The exalted-carrier technique is a way of avoiding distortion caused by selective fading of the carrier. Ordinarily, when the received carrier's amplitude drops, the signal becomes over-modulated, even though it was not transmitted that way. Distortion can be severe. Exalted carrier strips the carrier from the signal using the narrow BPF and it is used to drive the PLL. A copy of the limited carrier is then added back to the carrier-stripped signal, in its original phase prior to demodulation at an amplitude that avoids over-modulation. See Fig 16.17 for a block diagram of this type of demodulator. Refer to the chapter on **Modes and Modulation Sources** for more discussion of AM waveforms, and to the chapter on **Mixers, Modulators and Demodulators** for an implementation of this scheme.

#### FM and PM Demodulation

Traditional FM and PM demodulators, such as discriminators (filters) and PLLs may be implemented in DSP. But again, the I/Q method carries distinct advantages as it exploits mathematical relationships. We already defined the phase of an analytic signal in Eq 16 and so we can build a PM demodulator directly by finding arctangents. Possibilities include look-up tables and Taylor series. For an FM demodulator, we would then differentiate the string of phase samples using the technique of *first differencing*. We simply take the difference between adjacent samples by subtracting them:

$$f(t) = \phi(t) - \phi(t - 1) \tag{27}$$

and this is the FM demodulator's output. One common analog technique that stands out among DSP implementations is the quadrature detector. It is certainly simple and convenient to generate delays and multipliers, such as are required. The input signal is multiplied by a time-delayed copy of itself to produce a voltage proportional to its phase excursions away from the center frequency. This voltage is also proportional to the amount of delay inserted. See Fig 16.18. When the delay is an odd integral multiple of one quarter the input period, the output is zero. Longer delays produce greater output-voltage sensitivities; that is, dV/d\psi increases.

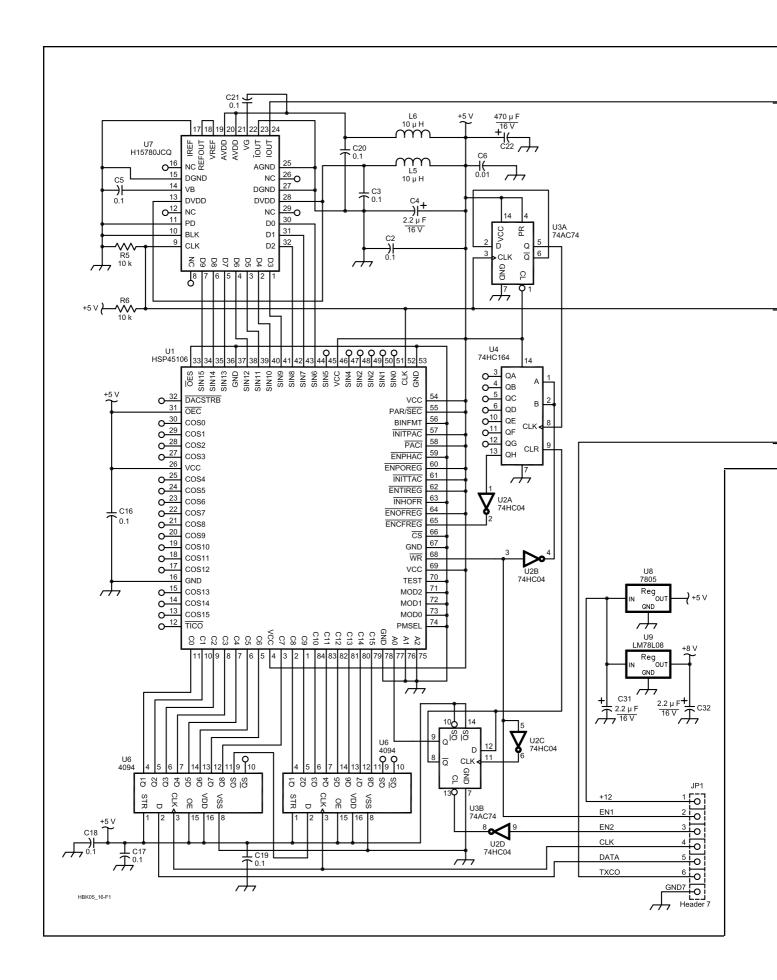

### Digital BFO Generation: Direct Digital Synthesis

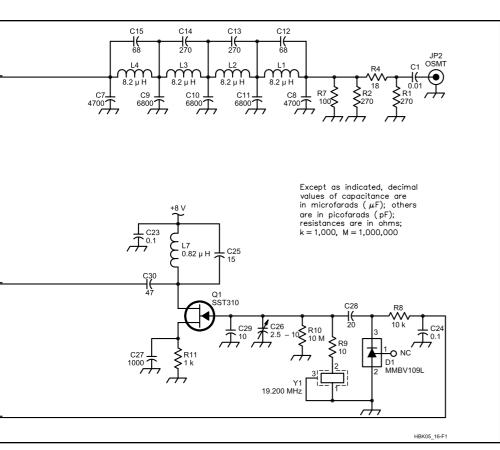

Synthesizers have come a long way since first becoming popular in HF transceivers of the 1970s. Availability of components then lagged well behind the development of theory. Now, hardware capabilities have nearly caught up-which is the case for DSP in general—and are driving the very rapid advancement of equipment we are now experiencing. Paralleling breakthroughs in the microprocessor and dataacquisition fields, progress in direct digital synthesis (DDS) has enabled performance levels only dreamed of a decade ago. Virtually all new designs may profit from this technology. Below, we will cover quite a few issues having impact on transceiver performance: phase noise, spectral purity, frequency stability, lock times and tuning resolution. A DDS circuit using dedicated

Fig 16.19—DDS block diagram.

Fig 16.20—Block diagram of a DDS/PLL hybrid synthesizer.

hardware is described; discussion of BFO and LO generation in software follows.

Synthesizer performance affects receiver dynamic range. Phase-noise and spectral-purity issues are in play. Phase noise is the unwanted phase modulation of transceiver frequency-control elements by circuit noise. It appears at and near the transmitter's output frequency and may cause interference to stations on adjacent frequencies. In addition, it may cause interference in one's own receiver—even if the signals received are phase-noise free—through the process of reciprocal mixing. See the Oscillators and Synthesizers chapter for a discussion of this effect. The spectral purity of a synthesizer may also affect receiver dynamic range by introducing spurious responses where spurs exist on the synthesizer's output. This may be true especially for the first LO in a receiver across the entire range of frequencies present. It is extremely important that this LO be clean.

Radio amateurs are free to operate anywhere within large frequency bands, so it might seem that frequency accuracy is not very critical. Prevalent narrow-band communication modes require it, though, and operators have come to expect excellent stability from their rigs. It is reasonable to expect ±20-Hz stability over a range of -10 to +50° C. Digital compensation tech-

niques currently achieve this. We wish to attain a tuning speed that does not impose limitations on typical use. "Cross-band" or split-frequency operation ought to be considered. For a frequency step of ±600 kHz, an upper limit of 25 ms on the lock time of a synthesizer is a reasonable goal. Lock time is defined as the time required to settle within the stability limits we already set. The smallest frequency steps should be such that they do not impede performance. 10 Hz used to be good enough, but now certain digital modes benefit from finer tuning. In addition, the digital notch filter described before is so sharp that it occasionally needs to be within 1 Hz!

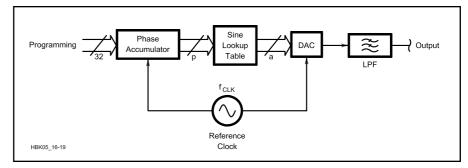

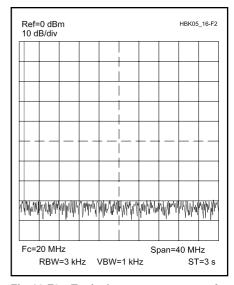

A DDS system generates digital samples of a sine wave and converts them to an analog signal using a DAC. See Fig 16.19. In a DDS chip, a phase accumulator is incremented at each clock time; the phase information is used to look up a sine-wave amplitude from a table. This value is passed to the DAC, which outputs a step-wise sine wave. As we saw before, the spectrum of this sine wave is seasoned with aliases and contains other minor pollutants. Since the phase is represented by a binary number with a fixed number of bits, p, errors develop because the number is truncated to that number of bits. Truncation generates PM spurs in the DDS output. This occurs prior to the DAC. Further errors are related to the output resolution of the look-up table. Table values representing the amplitudes are truncated to some number of bits, a. This mechanism produces AM spurs in the output. According to Cercas *et al*, the largest PM spurs have amplitude:

$$P_{\text{spur}} = -(6.02p - 5.17) \, \text{dBc}$$

(28)

and maximum AM spurs can rise to:

$$P_{\text{SDUT}} = -(6.02a + 1.75) \, \text{dBc} \tag{29}$$

Phase noise at the output is that of the DDS clock source times the ratio of the output frequency to the clock frequency, as limited by divider noise. Spurious levels also tend to grow as the DDS output frequency approaches the Nyquist limit. Strange spurs at the output are usually related to IMD and harmonics of the desired signal and their aliases. Remember that frequencies exceeding half the sampling frequency "fold back" into the signal spectrum at a position determined by their frequency, modulo f<sub>s</sub>/2. High-order harmonics are liable to find their way into one's band of interest. Traps at the DAC output have been known to suppress these responses. See Project F in the Appendix for the schematic of a DDS project.

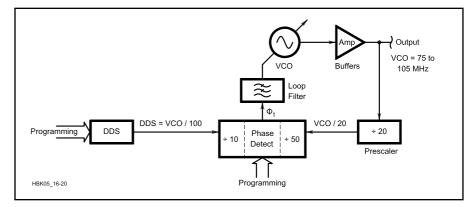

In the analog signal we generate, the DAC introduces more AM spurs, harmonics and IMD because of its inherent nonlinearity, as discussed above. Spurs are also likely at the clock frequency, its harmonics and sub-harmonics. A higherorder LPF will take care of these, but we must see what we can do about the others. It turns out we may eliminate all the AM spurs by squaring the DDS output. We can do nothing about the remaining PM spurs. Cranking through Eq 28 will show that they can be made very low: -113 dBc for a 20-bit-address sine look-up table and 32-bit phase accumulator. This parameter is critical in case we want to use the DDS as the reference to a high-frequency PLL circuit. The PLL will multiply the phase noise and PM spurs by the ratio of the PLL output frequency to the PLL reference frequency within the PLL loop BW. Outside the loop BW, the VCO itself is responsible for establishing spectral purity. So while dividing the DDS to the PLL reference frequency lowers phase noise and PM spurs, the PLL multiplies them back upward. A trade-off exists between spur levels and reference frequency, hence lock time.

A PLL reference frequency near 100 kHz has been found to be sufficient for the desired lock times, with an output-to-reference ratio of 1000. Such a loop should achieve very fast lock times, as it can be

expected to lock within 500 cycles of the reference input. The DDS tuning time is at least three orders of magnitude faster than this. In the example, the VCO output is near 100 MHz. DDS energy is injected at the reference input to the PLL chip, squaring it and dividing it by 10; the DDS runs near 1000 kHz. The block diagram of a PLL using a DDS as its reference is shown in **Fig 16.20**. Spurs and phase noise inside a loop BW of, say, 1 kHz are amplified by the PLL by the factor:

$$N = 20 \log \left( \frac{f_{VCO}}{f_{REF}} \right) = 40 \text{ dB}$$

(30)

Of course, we tune the hybrid synthesizer by programming the DDS; the PLL programming is fixed. Let's say we want 1-Hz tuning resolution at the VCO output. As the DDS frequency is 1/100 of the output, we must tune the DDS in  $10 \ millihertz$  steps! Tuning resolution in a DDS circuit is determined by the phase accumulator's bit resolution, p, and the DDS clock's frequency,  $f_{clk}$ :

$$df_{DDS} = \frac{f_{clk}}{2^p}$$

(31)

A clock frequency around 10 MHz and p = 32 easily satisfy our conditions, producing a step size of 2.3 millihertz. As noted above, making the DDS output frequency a small fraction of the clock frequency makes it easier to get a clean output. A range of about half an octave eases the design of the LPF or BPF used at the DDS output to limit spurs, aliases and clock feed-through.

The phase-accumulator/look-up-table approach is equally useful in generating numeric BFOs in software. One of the first things to emerge when considering this scheme is the potentially large size of the look-up table. To maintain the full dynamic range of a DSP system requires

BFO phase and amplitude performance, as limited by Eqs 28 and 29, at least as good as the rest of the system. In 16-bit systems, we are shooting for about 90-100 dB of dynamic range. A table with 2<sup>16</sup> = 65,536 entries is not much of a problem for DDS chip manufacturers to include onboard, but it may tax available memory space in embedded systems.

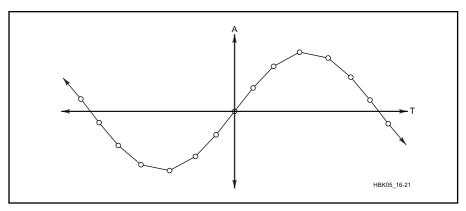

Fortunately, a couple of ways around the problem have been uncovered. The first involves the process of *interpolation*, very much like the artificial increase of sampling frequencies we examined above. In this method, we restrict the number of table entries to some arbitrary number,  $M \ll 2^{16}$ , while keeping the bit-resolution of the entries themselves, a, high enough to satisfy the limits of Eq 29 for the spur levels we can tolerate. Take the case where  $M = 2^8 = 256$  and a = 16. The phase accumulator, incremented at each sample time by an amount df that is directly proportional to the output frequency, forms the address into the look-up table. Let this address have bit-resolution p = 16. According to Eq 28, PM spurs will not exceed -91 dBc. Since there are only 256 table entries, we may use the most-significant byte (MSB) of the address to find the table entries that straddle the correct output value. We then use the least-significant byte (LSB) as an unsigned fraction to find out how far between the two table entries we must go to reach the correct output value. If, in order of increasing address in the table, our two adjacent table entries are d<sub>1</sub> and d<sub>2</sub>, we may perform a first-order interpolation between the entries using:

$$d_{int} = d_1 \left( \frac{256 - LSB}{256} \right) + d_2 \left( \frac{LSB}{256} \right)$$

(32)

This results in a linear, piece-wise representation of the data, as shown in **Fig 16.21**. The worst-case amplitude

Fig 16.21—Linear piece-wise representation of data resulting from first-order interpolation.

errors caused by this straight-line approximation place total harmonic distortion (THD) at the output at around 0.03% or -70 dBc. Much of this harmonic distortion is concentrated near half the sampling frequency, though, and may not be of much concern in actual systems. Doubling M would reduce THD to around

0.01%. Second and higher-order interpolation algorithms are available that outperform the first-order approximations by a long way.

In systems where an even smaller lookup table must be used, computation of sines and cosines using Taylor series might be attractive. THD is less than 0.008% when using four or five terms from the polynomials:

$$\sin(x) = x - \frac{1}{3!}x^3 + \frac{1}{5!}x^5 - \frac{1}{7!}x^7 \dots$$

(33)

and

$$\cos(x) = 1 - \frac{1}{2!}x^2 + \frac{1}{4!}x^4 - \frac{1}{6!}x^6 + \frac{1}{8!}x^8 \dots$$

(34)

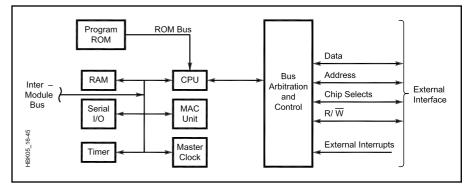

### DIGITAL SPEECH PROCESSING

Virtually all modern transmitters employ fast-attack, slow-decay RF compression: It is called automatic level control (ALC). Because transmitters are usually peak-power limited, some form of gain control is necessary to prevent overdrive of the final RF power amplifier.

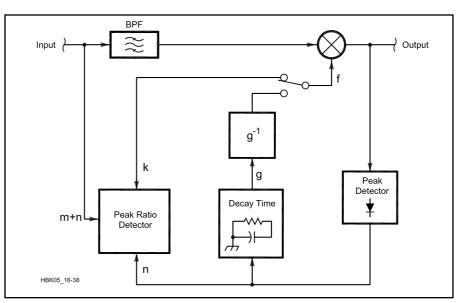

### **RF Compression**

A typical ALC system detects the transmitter's envelope with a rectifier and filter, applying this control signal to some gain-controlled stage or stages in the exciter. An increasing level from the envelope-detector results in decreasing gain such that the peak envelope power (PEP) is regulated. ALC is a servo loop employing negative feedback, usually developed only on voice peaks. As the decay time of the detector is decreased, some amplification of parts of speech falling between peaks is achieved. Enhancement cannot exceed the total gain reduction occurring at the voice peaks and usually falls in the range of 3-6 dB. The increase in the transmitter's average output power (talk power) may be quite a bit less than this depending on the characteristics of the voice, especially the peak-to-average ratio. In a digital exciter, we may eliminate the need for an analog gain-controlled stage by employing a numeric gain control factor in software and simply regulating the modulator's output level.

Human voices have peak-to-average ratios as high as 15 dB. This does not utilize a peak-limited transmitter very well in SSB mode: At the 100-W PEP level, the average output power might be as little as 3 W! RF compression raises the average output power and tends to further improve intelligibility by bringing out subtle parts of speech. In a digital I/Q modulator, we have a distinct advantage in designing an RF compressor: The RF envelope can be calculated before the modulation is performed. Once the microphone audio has been sampled and converted to an analytic signal, Eq 15 may be used to compute the envelope. To avoid the time-consuming square-root calculation, we may use an approximation:

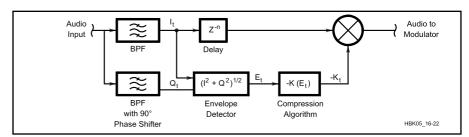

Fig 16.22—Digital RF compressor block diagram.

$$\begin{cases} For: |I| > |Q|, (I^2 + Q^2)^{1/2} \approx |I| + 0.4|Q| \\ For: |Q| > |I|, (I^2 + Q^2)^{1/2} \approx |Q| + 0.4|I| \end{cases} (35)$$

The envelope signal is used to compress the range of baseband levels prior to modulation so that the peak-to-average ratio is reduced. A block diagram of this system is shown in Fig 16.22. The net effect of the system can be shown to be identical to that of a direct RF compressor. This naturally involves distortion, since the transmitter is no longer linear; however, the distortion produced enhances the syllabic and formant energy in speech without introducing the "mushy" sound caused by heavy audio compression or clipping. As the attack and decay times of an RF compressor are made faster, it approaches the performance of an RF clipper, known to be the most effective form of processing. Because the baseband audio is processed prior to filtering and modulation, occupied BW does not increase much; loworder IMD products will be created, though, that fall within the desired transmit BW. These products ultimately limit the effectiveness of the compressor. This technique may also be applied to receivers.

### Audio Compression: Building an AM Transmitter

It has long been a problem to hold the carrier and modulation levels constant in AM transmitters covering several octaves of frequency, such as at HF. Because a baseband signal may not have symmetrical positive and negative amplitudes about its average value, a suitable analog ALC system would be incredibly complex.

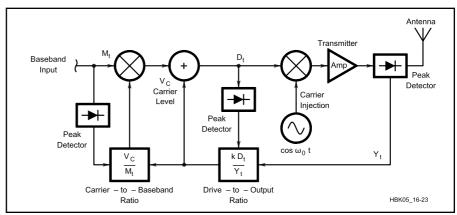

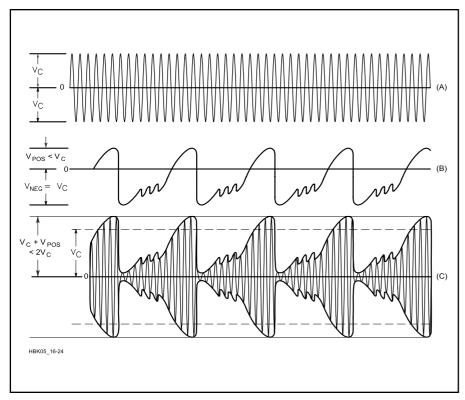

In DSP, we may prevent *carrier shift* using adaptive techniques; we prevent over-modulation using an audio compressor. (Refer to Fig 16.23.) First, the ratio of drive level to output level, d(t)/y(t), is easily computed by a DSP when the transmit-

Fig 16.23—AM ALC block diagram.

Fig 16.24—AM carrier (A). Baseband input with asymmetrical amplitudes (B). AM modulator output (C).

ter is on. From this, we can calculate what drive level is required to reach exactly 25% of the peak-power setting. We want the carrier to have this amplitude, regardless of modulation (or lack of it). Second, the baseband signal applied to the modulator must have a maximum peak level equal to the carrier's drive level established above. When the carrier and compressed baseband levels are added, the result is a 100%-modulated AM signal.

Fig 16.24 shows this situation, using a baseband signal whose negative excursions are greater than its positive excursions about the average value. Now two servomechanisms are operating in our AM ALC: One continually computes the drive-to-output ratio and sets the carrier level; the other compresses the peak baseband signal to that same peak level. Since the baseband peak detector has to find either the highest negative or highest positive peak, asymmetrical audio inputs may produce an unexpected result: Either the upward or downward modulation may reach 100% before the other can do so. If the downward modulation limits baseband amplitude first, the upward modulation would not cause the transmitter to reach its set PEP level without introducing a carrier shift.

### INTERFERENCE-REDUCTION TECHNIQUES

We touched on the idea of a manually tuned adaptive notch filter using the LMS (least-mean-squares) algorithm. These principles are explored in more detail here, especially as they apply to interference- and noise-reduction systems. The nature of information-bearing signals is that they are in some way coherent; that is, they have some features that distinguish them from noise. For example, voice signals have attributes related to the pitch, syllabic content and impulse response of a person's voice.

### **Adaptive Filtering**

We will find it possible to build an adaptive filter that accentuates those repetitive components and suppresses the non-repetitive (noise). Much research has been done about detection of a sinusoidal signal buried in noise. Adaptive filtering methods are based on the exploitation of the statistical properties of the sampled input signal, specifically, *autocorrelation*. Simply put, autocorrelation refers to how recent samples

Fig 16.25—An adaptive modeling system.

Fig 16.26—An adaptive modeling system, which requires a person at the filter controls.

of a waveform resemble past input samples. We will discuss an *adaptive predictor*, which actually makes a reasonable guess at what the next sample will be based on past samples. This leads directly to an adaptive noise-reduction system.

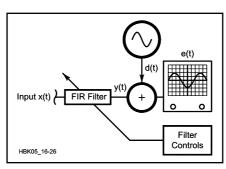

#### An Adaptive Interference Canceler

Imagine we have some sampled input signal, x(t), that we want to adaptively filter to enhance its repetitive content. In the case of a CW signal, all that is required is a BPF centered on the desired frequency. We know that this signal takes the form of a sine wave and that its amplitude will change markedly. Its frequency may not be absolutely constant, either, but we will assume it is fixed for now. We set up an FIR filter structure and an error-measurement system to compare a reference sine wave, d(t), with the output of the filter. y(t). See Fig 16.25. Sine wave d(t) is the same frequency we expect the CW tone to be. The difference output, e(t), is known

as the error signal.

Now imagine some person is watching the error signal and has their hands on the controls that change the filter coefficients. (See Fig 16.26.) Minimizing the error signal by tweaking the coefficients forces the filter to converge to a BPF centered at the frequency of d(t). The speed and accuracy of that convergence is going to depend on how well the person analyzes and reacts to the error data. If it is difficult to tell that a sine wave is present, then adjusting the filter will also be difficult. Further, if the sampling rate is high enough, a person will not be able to keep up; they can check the error only so often or can generate longterm averages of the error.

Using the typical processes of the human mind, the person will soon discover that if they turn the controls the wrong way, the error increases. This information is used to reverse the direction of adjustment. The person then turns the controls the other way. It soon emerges that the person is on a performance surface, with an "uphill" and a "downhill," and they know the goal is to go only downhill. So they thrash about with the controls, sometimes making mistakes, but ultimately making headway overall down the hill. At some point, the error gets rather small: They know they are near the "bottom of the bowl." Once at the bottom, it is uphill no matter which way they go. The goal of minimizing the error e(t) has been achieved. They continue gently flailing about with the controls, but always staying near the bottom. This situation is analogous to aligning an analog BPF with an adjustment tool.

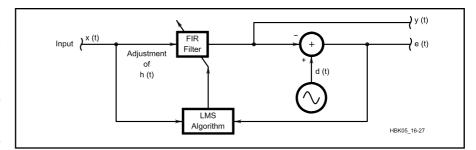

After doing this whole thing several times, the person finds that certain rules help speed up the process. First, there is a relationship between the magnitude of the error and the amount they must tweak the controls. If the total error is large, a lot of tweaking must be done; if small, then it is better to make small adjustments to stay near the bottom of the performance surface. Second, there is a correlation between the error, e(t); the input samples, x(t); and the coefficient set, h(t) they need to adjust. Derivation of algorithms providing for steepest descent down the hill is a long and tedious exercise in linear algebra. Let's just say the person goes to school, becomes an expert in matrix mathematics and discovers that one of the fastest and most accurate ways down the hill is to adjust coefficients at sample time t according to:

$$h_{t+1}(k) = h_t(k) + 2\mu e(t)x(t)$$

(36)

This is the LMS algorithm. It was developed by Widrow and Hoff in the late 1950s.

Replacing the person with the LMS algorithm, as shown in **Fig 16.27**, we have our

Fig 16.27— An adaptive interference canceler.

Fig 16.28—An adaptive predictor.

manually tuned adaptive interference canceler. Note that both the desired output, v(t), and the undesired, e(t), are available. This is nice in case we want to take only the broadband component and reject the tone. An obvious application of such tone rejection would be as a *notch filter*, and conversely, reception of a desired tone (signal) while rejecting the broadband (noise) is also possible; that is, noise reduction! Performance issues of interest include the adjustment error near the bottom of the performance surface and the speed of adaptation. One of the first things we notice about the LMS algorithm is that each of these factors is directly proportional to u. We select its value, which ranges from 0 to 1, to set the desired properties. A trade-off exists between speed and misadjustment. Large values of  $\mu$  result in fast convergence, but large misadjustment in the steady state. Total misadjustment is also proportional to the number of filter taps, L, and this may place a limitation on the complexity of the filter that may be used. The total delay through the filter also grows with its length; it may become unacceptably large under certain conditions. As in Eq 10, the BW of the adaptive BPF is:

$$BW = \frac{2\mu A^2}{t_s} \text{ rad/s}$$

(37)

Small values of  $\mu$  result in narrower filters that take longer to adapt. Attempts may be made to adjust  $\mu$  on the fly by using a value that changes in proportion to the error, e(t). A large value is selected initially for rapid convergence, then it is decreased to

minimize the long-term misadjustment. This works fine so long as the characteristics of the input signal are not rapidly changing.

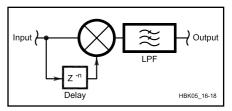

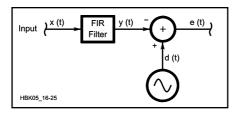

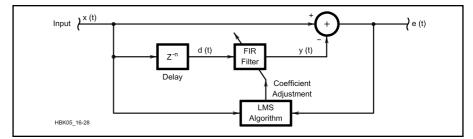

## An Adaptive Interference Canceler Without An External Reference: An Adaptive Predictor

In the above example, we knew pretty much what to expect at the output: a sine wave of known frequency. What happens when we do not know much about the nature of the input signal, except that it contains coherent components? Quite a few circumstances like this arise in practice. It might seem at first that adaptive processing could not be applied; however, if a delay, zn is inserted in the primary input, x(k), to create the reference input, d(k), periodic signals may be detected and thereby enhanced (or eliminated). See Fig 16.28. This delay forms an autocorrelation offset, representing the time difference used to compare past input samples with present samples. The amount of delay must be chosen so that the desired components in the input signal correlate with themselves, and the undesired components do not. This is an adaptive predictor: Predictable components are enhanced, while the unpredictable parts are removed. Experiments show that for any given value of m, the filter converges quickest when the delay, z-n, is set between one half and one times the filter's total delay.

We may predict this circuit's noise-reduction performance using the ratio of the pre-

filtered BW to that of the converged filter:

$$\Delta SNR = 10 \log \left( \frac{BW_{input}}{BW_{filter}} \right)$$

$$= 10 \log \left( \frac{BW_{input}}{2\mu A^2 f_s} \right)$$

(38)

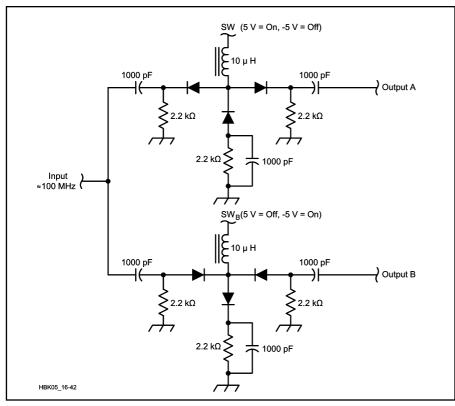

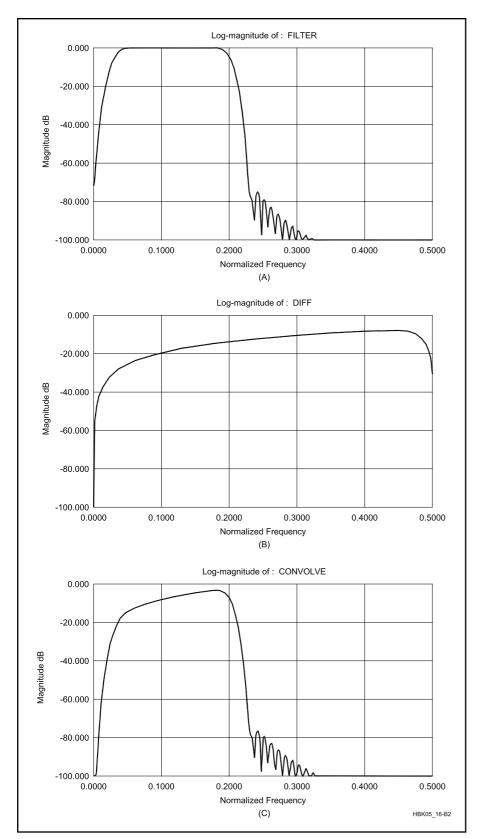

As an example, for  $\mu = 0.005$ , A = 1,  $BW_{input} = 3 \text{ kHz}$  and  $f_s = 15 \text{ kHz}$ , the SNR improvement is about 13 dB. When adaptive filters with many taps are used, multiple tones may be either enhanced or notched. Under most conditions, the undesired components are large compared to the desired; enhancement of signals is needed most when the input SNR is low. This situation may not give us enough thrashing about to find our way down the performance surface to convergence. Adding artificial noise to satisfy this condition is tempting, but it turns out we can alter the algorithm slightly to improve our lot without actually adding such noise. These additional terms in the algorithm are known as leakage terms.