### Contents

- 4.1 Digital vs Analog

- 4.2 Number Systems

- 4.2.1 Binary

- 4.2.2 Hexadecimal

- 4.2.3 Binary Coded Decimal (BCD)

- 4.2.4 Conversion Techniques

- 4.3 Physical Representation of Binary States

- 4.3.1 State Levels

- 4.3.2 Transition Time

- 4.3.3 Propagation Delay

- 4.4 Combinational Logic

- 4.4.1 Boolean Algebra and the Basic Logical Operators

- 4.4.2 Common Gates

- 4.4.3 Additional Gates

- 4.4.4 Boolean Theorems

- 4.5 Sequential Logic

- 4.5.1 Synchronicity and Control Signals

- 4.5.2 Flip-Flops

- 4.5.3 Groups of Flip-Flops

- 4.5.4 Multivibrators

- 4.6 Digital Integrated Circuits

- 4.6.1 Comparing Logic Families

- 4.6.2 Bipolar Logic Families

- 4.6.3 Metal Oxide Semiconductor (MOS) Logic Families

- 4.6.4 Interfacing Logic Families

- 4.6.5 Real-World Interfacing

- 4.7 Microcontrollers

- 4.7.1 An Overview of Microcontrollers

- 4.7.2 Selecting a Microcontroller

- 4.7.3 The Development Process

- 4.7.4 Learning More About Microcontrollers

- 4.8 Personal Computer Interfacing

- 4.8.1 Parallel vs Serial Signaling

- 4.8.2 Data Rate

- 4.8.3 Error Detection

- 4.8.4 Standard Interface Buses

- 4.9 Glossary of Digital Electronics Terms

- 4.10 References and Bibliography

# **Digital Basics**

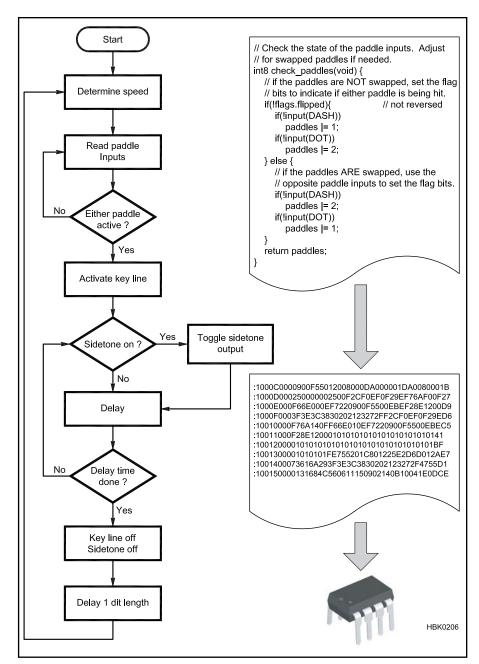

Radio amateurs have been involved with digital technology since the first spark transmitters, a form of pulse-coded transmission, were connected to an "aerial." Modern digital technology use by radio amateurs probably arrived first in CW keyers, where hams learned about flip-flops and gates to replace their semi-automatic mechanical "bug" keys.

Amateur use of digital technology echoed public use of these new abilities, starting with using the first home computers for calculations and later digital communications terminals. Today's Amateur Radio digital applications range from simple shack accessories like keyers and timers, to computer based digital modes such as PSK31 and Hellschreiber, to computer networking using TCP/IP over AX.25, computer controlled rigs, digital signal processing and software defined radios.

This chapter was written by Dale Botkin, NØXAS, building on material in previous editions by Christine Montgomery, KGØGN and Paul Danzer, N1II. It presents digital theory fundamentals and some applications of that theory in Amateur Radio. The fundamentals introduce digital mathematics, including number systems, logic devices and simple digital circuits. Next, the implementation of these simple circuits is explored in integrated circuits, their families and interfacing. Finally, some Amateur Radio applications are discussed involving digital logic, embedded microcontrollers and interfacing to personal computers.

### 4.1 Digital vs Analog

An analog signal can represent an infinitely variable indication of voltage, current, frequency, the position of a dial, or some other condition or value. As an example, using a potentiometer as a volume control will give you infinitely variable control over the volume of a signal. In theory, there is no limit to the difference in volume that can be produced. Though the control may be marked from 1 to 10, the actual value would have to be represented by a real number somewhere between 0 and 10. There are an infinite number of settings in between.

In its simplest form, a digital signal simply indicates the *on* or *off* state of some value or input signal. For example, the straight key you may use to key your CW transmitter (or the PTT switch of your voice transmitter) produces an on or off binary signal. In one state the transmitter produces an output signal of some sort; in the other state it does not. Another example is a simple light switch. The light is either on, or it's off. We represent these two states using 0 for off and 1 for on.

Digital electronics gets more interesting when we combine several or many simple on/off digital states to perform more complex tasks. For example, a relatively simple digital circuit can connect the antenna to either the transmitter or the receiver depending on a PTT or other keying signal. It can turn a preamp on or off depending on the state of the transmitter, mute the speaker while transmitting, and even select an antenna based on the selected frequency band. No special digital integrated circuits (chips) are needed to do any of these tasks; we can simply use bipolar transistors or MOSFETs, driven to saturation, as on/off switches. Simple circuits like this can often even be implemented with relays or diodes. The important fact is that the system is digital. There is no "almost transmitting" or "PTT switch partially pressed" state — it's either on, or it's off.

A very useful aspect of digital electronics is our ability to construct simple circuits that can

maintain their on/off state indefinitely, until some event causes them to change. These flip-flop circuits can be used in various combinations to form registers that store information for later use or counters that count events and can be read or reset when needed. All of these circuits can be combined in ever larger groups until we finally arrive at the modern microprocessor. A microprocessor can accept input signals from many sources, follow a stored program to perform complex data storage and mathematical calculations, and produce output that we can use to do things that would be far more difficult with analog circuits.

So let's revisit our volume control example from the earlier paragraph. Let's assume we have a volume control, but it is used as an input to a digital system that will produce output at the desired level. This is

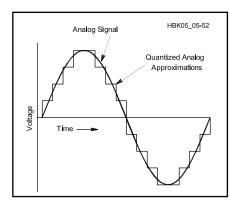

Fig 4.1 — An analog signal and its analog approximation. Note that the analog waveform has continuously varying voltage while the approximated waveform is composed of discrete steps.

quite common in modern equipment, whether it is amateur or consumer gear. Since the control is now digital, we know we can't have an infinite number of values. However, a simple on/off volume control would not be very useful. Using digital electronics, we can break the range between "off" and "fully on" into as many discrete steps as we need. With enough steps, we can give the user of the equipment an approximation of the origi-

nal analog control while keeping the actual control digital.

By using coding, as discussed in the following pages, the two binary values (off and on, or 0 and 1) can represent any number of real values. **Fig 4.1** illustrates the contrast of an analog signal (in this case a sine wave) and its digital approximation. Four positive and four negative values are shown as an approximation to the sine wave, but any number of coded

value steps can be used as an approximation. The more values are used to approximate the wave, the closer you can come to the actual wave form.

While the focus in this chapter will be on digital theory, many circuits and systems involve *both* digital and analog components. Often, a designer may choose between using digital technology, analog technology or a combination.

### 4.2 Number Systems

If you have been around computer hobbyists, some of whom are also hams, you may have seen a T-shirt or bumper sticker that reads, "There are 10 kinds of people in the world: those who understand binary, and those who don't." If this has puzzled you in the past, after reading this chapter you will be able to laugh with the rest of us.

In order to understand digital electronics, you must first understand the binary numbering system. Any number system has two distinct characteristics: a set of symbols (digits or numerals) and a base or radix. A number is a collection of these digits, where the leftmost digit is the most significant digit (MSD) and the right-most digit is the least significant digit (LSD). The value of this number is a weighted sum of its digits. The weights are determined by the system's base and the digit's position relative to the decimal point.

While these definitions may seem strange with all the technical terms, they will be more

familiar when seen in a decimal system example. See **Table 4.1**. This is the "traditional" number system with which we are all familiar. In the *base-10* or decimal numbering system we use every day, the digits used are 0 through 9. The weights are powers of ten:  $10^0$  or 1 for the right-most column,  $10^1$  or 10 for the next column,  $10^2$  or 100 for the next and so on. Thus the number 548 represents five hundreds, four tens and eight ones. In this case, 5 is the MSD, and 8 is the LSD. Once you understand this concept, it can be applied to numbering systems using bases other than 10 such as base-2, base-8, or even base-16.

#### **4.2.1 Binary**

Binary is a base-2 number system and therefore limited to two symbols:  $\{0, 1\}$ . The weight factors are now powers of 2, like  $2^0, 2^1$  and  $2^2$ . For example, the decimal number, 163

and its equivalent binary number, 10100011, are shown in **Table 4.2**.

The digits of a binary number are now bits (short for binary digit). The MSD is the most significant bit (MSB) and the LSD is the least significant bit (LSB). Four bits make a nibble (which you will occasionally see spelled nybble) and two nibbles, or eight bits, make a byte. The length of a word is dependent upon the hardware; it generally can consist of two or four or more bytes, but occasionally will be some other number of bits. These groupings are useful when converting to hexadecimal notation, which is explained later. It is important to remember that while everyone agrees on the meaning of a bit, a nibble (regardless of spelling) and a byte, the meaning of word can vary.

Counting in binary follows the same pattern we would use for decimal or any other number system. Consider the three digit binary number XXX. First fill up the right-hand column.

Binary Decimal Number Equivalent 0000 0 0001 1

The column has been filled, and much quicker than with decimal, since there are only two values instead of 10. But just as we would with a decimal number, we now reset the right-hand column to 0, increase the next column by 1, and continue.

### Table 4.1 Decimal Numbers

Example: 548

Table 4.2

Decimal and Binary Number Equivalents

```

128

0

0

+0

decimal

1(128)

0(64)

1(32)

0(16)

0(8)

+0(4)

+1(1)

0(26)

1(25)

0(2^{3})

+1(20)

0(24)

1(2^{7})

+0(2^2)

n

0

0

10100011

0

1

binary

MSB

LSB

Nibble

Nibble

Byte = 8 digits

```

**0010** 2 **0011** 3

Now the first two columns are full, so reset both back to 0 and increase the next column by 1 and continue:

#### 4.2.2 Hexadecimal

The *hexadecimal*, or hex, *base-16* number system is widely used in computer systems for its ease in conversion to and from binary numbers and the fact that it is somewhat more human-friendly than long strings of 1s and 0s. A base-16 number requires 16 symbols. Since our normal mathematical number, as set up in the decimal system, has only 10 digits (0 through 9), a set of additional new symbols is required. Hex uses both numbers and characters in its set of sixteen symbols: {0, 1, 2, 3, 4, 5,6, 7, 8, 9, A, B, C, D, E, F}. Here, the letters A to F have the decimal equivalents of 10 to 15 respectively: A=10, B=11, C=12, D=13, E=14 and F=15. Again, the weights are powers of the base, such as  $16^0$ ,  $16^1$  and  $16^2$ .

The four-bit binary listing in the previous paragraph shows that the individual 16 hex digits can be represented by a four-bit binary number. Since a byte is equal to eight binary digits, two hex digits provide a byte — the equivalent of 8 binary digits. Conversion from binary to hex is therefore simplified. Take a binary number, divide it into groups of four binary digits starting from the right, and convert each of the four binary digits to an individual value.

Conversion from hex to binary is equally convenient; simply replace each hex digit with its four-bit binary equivalent. As an example, the decimal number 163 is shown in Table 4.2 as binary 10100011. Divide the binary number in groups of four, so 1010 is equivalent to decimal 10 or "A" hex, and 0011 is equivalent to decimal 3, thus decimal number 163 is equivalent to hex A3.

# 4.2.3 Binary Coded Decimal (BCD)

The binary number system representation is the most appropriate form for fast internal computations since there is a direct mathematical relationship for every bit in the number. To interface with a human user — who usually wants to see inputs and outputs in terms of decimal numbers — other codes are more useful. The *Binary Coded Decimal*

(BCD) system is a simple method for converting binary values to and from decimal for inputs and outputs for user-oriented digital systems. Back in the days when the most common method of presenting output to a user was via seven-segment LED displays, BCD was widely used. Since we now mostly use powerful microprocessors that can easily present information in decimal form, BCD is not nearly as common as it once was. You may, however, run into BCD when using or repairing older digital gear. It is also used in some chips intended for use in digital voltmeters.

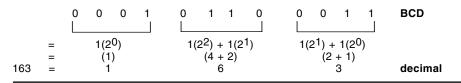

In the BCD system, each decimal digit is expressed as a corresponding 4-bit binary number. In other words, the decimal digits 0 to 9 are encoded as the bit strings 0000 to 1001. To make the number easier to read, a space is left between each 4-bit group. For example, the decimal number 163 is equivalent to the BCD number 0001 0110 0011, as shown in **Table 4.3**.

The important difference between BCD and the previous number systems is that, starting with decimal 10, BCD loses the standard mathematical relationship of a weighted sum. BCD is simply a cut-off hexadecimal. Instead of using the 4-bit code strings 1010 to 1111 for decimal 10 to 15, BCD uses 0001 0000 to 0001 0101. This is one of the reasons that we have moved away from BCD.

#### 4.2.4 Conversion Techniques

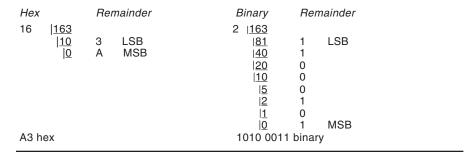

An easy way to convert a number from decimal to another number system is to do repeated division, recording the remainders in a tower just to the right. The converted number, then, is the remainders, reading up the tower. This technique is illustrated in **Table 4.4** for hexadecimal and binary conversions of the decimal number 163.

For example, to convert decimal 163 to hex, repeated divisions by 16 are performed. The first division gives 163/16 = 10 remainder 3. The remainder 3 is written in a column to the right. The second division gives 10/16 = 0 remainder 10. Since 10 decimal = A hex, A is written in the remainder column to the right. This division gave a divisor of 0 so the process is complete. Reading up the remainders column, the result is A3. The most common mistake in this technique is to forget that the Most Significant Digit ends up at the bottom.

Another technique that should be briefly mentioned can be even easier: use a calculator with a binary and/or hex mode option. Many inexpensive and readily available calculators intended for scientific and programming use will convert between number systems quite easily. In addition, calculator programs are available for all types of personal computers regardless of the operating system used.

One warning for this technique: this chapter doesn't discuss negative binary numbers. If your calculator does not give you the answer you expected, it may have interpreted the number as negative. This would happen when the number's binary form has a 1 in its MSB, such as the highest (leftmost) bit for the binary mode's default size. To avoid learning about negative binary numbers the hard way, always use a leading 0 when you enter a number in binary or hex into your calculator.

Table 4.3

Binary Coded Decimal Number Conversion

Table 4.4 Number System Conversions

### 4.3 Physical Representation of Binary States

#### 4.3.1 State Levels

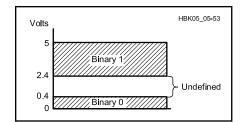

Most digital systems use the binary number system because many simple physical systems are most easily described by two state levels (0 and 1). For example, the two states may represent "on" and "off" or a "mark" and "space" in a communications transmission. In electronic systems, state levels are physically represented by voltages. A typical choice is state  $0=0~\rm V$

state 1 = 5 V

Since it is unrealistic to obtain these exact voltage values, a more practical choice is a range of values, such as

state 0 = 0.0 to 0.4 V state 1 = 2.4 to 5.0 V

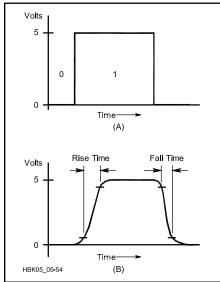

**Fig 4.2** illustrates this representation of states by voltage levels. The undefined region between the two binary states is also known as the *transition region* or *noise margin*.

#### 4.3.2 Transition Time

The gap in Fig 4.2, between binary 0 and binary 1, shows that a change in state does not occur instantly. There is a transition time between states. This transition time is a result of the time it takes to charge or discharge the stray capacitance in wires and other components because voltage cannot change instantaneously across a capacitor. (Stray inductance in the wires also has an effect because the current through an inductor can't change instantaneously.) The transition from a 0 to a 1 state is called the *rise time*, and is usually specified as the time for the pulse to rise from 10% of its final value to 90% of its final value. Similarly, the transition from a 1 to a 0 state is called the *fall time*, with a similar 10% to 90% definition. Note that these times need not be the same. Fig 4.3A shows an ideal signal, or pulse, with zero-time switching. Fig 4.3B shows a typical pulse, as it changes between states in a smooth curve.

Rise and fall times vary with the logic family used and the location in a circuit. Typical values of transition time are in the microsecond to nanosecond range. In a circuit, distributed inductances and capacitances in wires or

Fig 4.2 — Representation of binary states 1 and 0 by a selected range of voltage levels

PC-board traces may cause rise and fall times to increase as the pulse moves away from the source. One reason rise and fall times may be of interest to the radio designer is because of the possibility of generating RF noise in a digital circuit.

#### 4.3.3 Propagation Delay

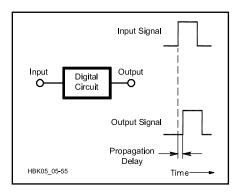

Rise and fall times only describe a relationship within a pulse. For a circuit, a pulse input into the circuit must propagate through the circuit; in other words it must pass through each component in the circuit until eventually it arrives at the circuit output. The time delay between providing an input to a circuit and seeing a response at the output is the *propaga*tion delay and is illustrated by **Fig 4.4**.

For modern switching logic, typical propagation delay values are in the 1 to 15 nanosecond range. (It is useful to remember that the propagation delay along a wire or printed-circuit-board trace is about 1.0 to 1.5 ns per inch.) Propagation delay is the result of cumulative transition times as well as transistor switching delays, reactive element charging times and the time for signals to travel through wires. In complex circuits, different propagation delays through different paths can cause problems when pulses must arrive somewhere at exactly the same time.

The effect of these delays on digital devices can be seen by looking at the speed of the digital pulses. Most digital devices and all PCs

Fig 4.3 — (A) An ideal digital pulse and (B) a typical actual pulse, showing the gradual transition between states.

Fig 4.4 — Propagation delay in a digital circuit.

use *clock pulses*. If two pulses are supposed to arrive at a logic circuit at the same time, or very close to the same time, the path length for the two signals cannot be any different than two to three inches. This can be a very significant design problem for high-speed logic designs.

# 4.4 Combinational Logic

Having defined a way to use voltage levels to physically represent digital numbers, we can apply digital signal theory to design useful circuits. Digital circuits combine binary inputs to produce a desired binary output or combination of outputs. This simple combination of 0s and 1s can become very powerful, implementing everything from simple switches to powerful computers.

A digital circuit falls into one of two types: combinational logic or sequential logic. In a *combinational logic* circuit, the output depends only on the *present inputs* (if we ignore propagation delay). In contrast, in a *sequential logic* circuit, the output depends on the present inputs, the *previous sequence of inputs* and often a clock signal. Later sections of this chapter will examine some circuits

built using the basics established here.

# 4.4.1 Boolean Algebra and the Basic Logical Operators

Combinational circuits are composed of logic gates, which perform binary operations. Logic gates manipulate binary numbers, so you need an understanding of the algebra of

binary numbers to understand how logic gates operate. *Boolean algebra* is the mathematical system used to describe and design binary digital circuits. It is named after George Boole, the mathematician who developed the system. Standard algebra has a set of basic operations: addition, subtraction, multiplication and division. Similarly, Boolean algebra has a set of basic operations; called *logical operations*: NOT, AND and OR.

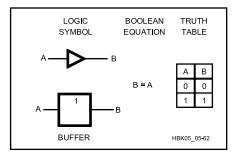

The function of these operators can be described by either a Boolean equation or a truth table. A Boolean *equation* describes an operator's function by representing the inputs and the operations performed on them. An equation is of the form "B = A," while an *expression* is of the form "A." In an assignment equation, the inputs and operations appear on the right and the result, or output, is assigned to the variable on the left.

A *truth table* describes an operator's function by listing all possible inputs and the corresponding outputs. Truth tables are sometimes written with Ts and Fs (for true and false) or with their respective equivalents, 1s and 0s. In company databooks (catalogs of logic devices a company manufactures), truth tables are usually written with Hs and Ls (for high and low). In the figures, 1 will mean high and 0 will mean low. This representation is called positive logic. The meaning of different logic types and why they are useful is discussed in a later section.

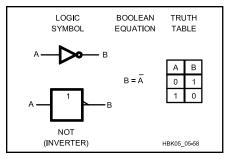

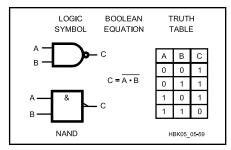

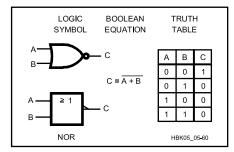

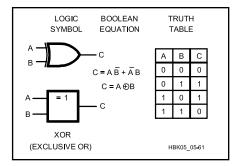

Each Boolean operator also has two circuit symbols associated with it. The traditional symbol—used by ARRL and other US publications—appears on top in each of the figures; for example, the triangle and bubble for the NOT function in Fig 4.7. In the traditional symbols, a small circle, or *bubble*, always represents "NOT." (This *bubble* is called a state indicator.)

Appearing just below the traditional symbol is the newer ANSI/IEEE Standard symbol. This symbol is always a square box with notations inside it. In these newer symbols, a small triangular flag represents "NOT." The new notation is an attempt to replace the detailed logic drawing of a complex function with a simpler block symbol. Adoption of the newer symbols has been spotty, and you are therefore still more likely to see the traditional symbols for basic logic functions than the ANSI/IEEE symbols.

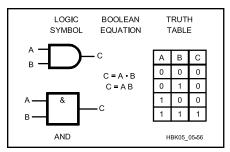

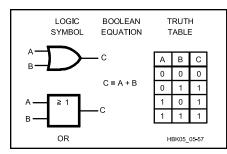

#### 4.4.2 Common Gates

Figs 4.5, 4.6 and 4.7 show the truth tables, Boolean algebra equations and circuit symbols for the three basic Boolean operations: AND, OR and NOT, respectively. All combinational logic functions, no matter how complex, can be described in terms of these three operators. Each truth table can be converted into words. The truth table for the two-input AND gate can be expressed as "the output

Fig 4.5 — Two-input AND gate.

Fig 4.6 — Two-input OR gate.

Fig 4.7 — Inverter.

C is a 1 only when the inputs are both 1s." This can be seen by examining the output column C — it remains at a 0 and becomes a 1 only when the input column A and the input column B are both 1s — the last line of the table.

The NOT operation is also called *inversion*, *negation* or *complement*. The circuit that implements this function is called an *inverter* or *inverting buffer*. The most common notation for NOT is a bar over a variable or expression. For example, NOT A is denoted  $\overline{A}$ . This is read as either "Not A" or as "A bar." A less common notation is to denote Not A by A', which is read as "A prime." You will also see various other notations in schematic diagrams and component data sheets, such as a leading exclamation point or has symbol — !A or #A indicating "Not A."

While the inverting buffer and the noninverting buffer covered later have only one input and output, many combinational logic elements can have multiple inputs. When a combinational logic element has two or more inputs and one output, it is called a *gate*. (The

term "gate" has a number of different but specific technical uses. For a clarification of the many definitions of gate, see the section on **Synchronicity and Control Signals**, later in this chapter.) For simplicity, the figures and truth tables for multiple-input elements will show the operations for only two inputs, the minimum number. Remember, though, that it is quite common to have gates with more than two inputs. A three-, four-, or eight-input gate works in the exact same manner as a two-input gate.

The output of an AND function is 1 only if *all* of the inputs are 1. Therefore, if *any* of the inputs are 0, then the output is 0. The notation for an AND is either a dot ( $\bullet$ ) between the inputs, as in C = A $\bullet$ B, or nothing between the inputs, as in C = AB. Read these equations as "C equals A AND B."

The OR gate detects if one or more inputs are 1. In other words, if any of the inputs are 1, then the output of the OR gate is 1. Since this includes the case where more than one input may be 1, the OR operation is also known as an INCLUSIVE OR. The OR operation detects if at least one input is 1. Only if all the inputs are 0, then the output is 0. The notation for an OR is a plus sign (+) between the inputs, as in C = A + B. Read this equation as "C equals A OR B."

#### **4.4.3 Additional Gates**

More complex logical functions are derived from combinations of the basic logical operators. These operations — NAND, NOR, XOR and the noninverter or buffer — are illustrated in **Figs 4.8** through **4.11**, respectively. As before, each is described by a truth table, Boolean algebra equation and circuit symbols. Also as before, except for the noninverter, each could have more inputs than the two illustrated.

The NAND gate (short for NOT AND) is equivalent to an AND gate followed by a NOT gate. Thus, its output is the complement of the AND output: The output is a 0 only if all the inputs are 1. If any of the inputs is 0, then the output is a 1.

The NOR gate (short for NOT OR) is equivalent to an OR gate followed by a NOT gate. Thus, its output is the complement of the OR output: If any of the inputs are 1, then the output is a 0. Only if all the inputs are 0, then the output is a 1.

The operations so far enable a designer to determine two general cases: (1) if *all* inputs have a desired state or (2) if *at least one* input has a desired state. The XOR and XNOR gates enable a designer to determine if *one and only one* input of a desired state is present.

The XOR gate (read as EXCLUSIVE OR) is a combination of an OR and a NAND gate. It has an output of 1 if one and only one of the inputs is a 1 state. The output is 0 otherwise. The symbol for XOR is  $\oplus$ . This is easy to

Fig 4.8 — Two-input NAND gate.

Fig 4.9 — Two-input NOR gate.

Fig 4.10 — Two-input XOR gate.

Fig 4.11 — Noninverting buffer.

remember if you think of the "+" OR symbol enclosed in an "O" for *only one*.

The XOR gate is also known as a "half adder," because in binary arithmetic it does everything but the "carry" operation. The following examples show the possible binary additions for a two-input XOR.

| A   | 0 | 0        | 1 | 1        |

|-----|---|----------|---|----------|

| В   | 0 | <u>1</u> | 0 | <u>1</u> |

| Sum | 0 | 1        | 1 | 0        |

The XNOR gate (read as EXCLUSIVE NOR) is the complement of the XOR gate. The output is 0 if one and only one of the inputs is a 1. The output is 1 either if all inputs are 0 or more than one input is 1.

#### **NONINVERTERS (BUFFERS)**

A noninverter, also known as a buffer, amplifier or driver, at first glance does not seem to do anything. It simply receives an input and produces the same output. In reality, it is changing other properties of the signal in a useful fashion, such as amplifying the current level. While not useful for logical operations, applications of a noninverter include providing sufficient current to drive a number of gates or some other circuit such as a relay; interfacing between two logic families; obtaining a desired pulse rise time; and providing a slight delay to make pulses arrive at the proper time.

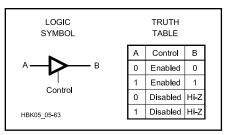

#### TRI-STATE GATES

Under normal circumstances, a logic element can drive or feed several other logic elements. A typical AND gate might be able to drive or feed 10 other gates. This is known as *fan-out*. However, with certain exceptions only one gate output can be connected to a single wire. If you have two possible driving sources to feed one particular wire, some logic network that probably includes a number OR gates must be used.

In many applications, including computers, data is routed internally on a set of wires called *buses*. The data on the bus can come from many circuits or drivers, and many other devices may be *listening* on the bus. To eliminate the need for the network of OR gates to drive each bus wire, a set of gates known as *tri-state* gates are used.

The symbol and truth table for a tri-state gate are shown in **Fig 4.12**. A tri-state gate can be any of the common gates previously described, but with one additional control lead. When this lead is enabled (it can be designed to allow either a 0 or a 1 to enable it) the gate operates normally, according to the truth table for that type of gate. However, when the gate is not enabled, the output goes to a high impedance, and so far as the output wire is concerned, the gate does not exist.

Each device that has to send data down a bus wire is connected to the bus wire through a tri-state gate. However, as long as only one device, through its tri-state gate, is enabled, it is as though all the other connected tri-state gates do not exist.

#### 4.4.4 Boolean Theorems

The analysis of a circuit starts with a logic diagram and then derives a circuit description. In digital circuits, this description is in the form of a truth table or logical equation. The

Fig 4.12 — Tri-State gate.

synthesis, or design, of a circuit goes in the reverse: starting with an informal description, determining an equation or truth table and then expanding the truth table to components that will implement the desired response. In both of these processes, we need to either simplify or expand a complex logical equation.

To manipulate an equation, we use mathematical *theorems*. Theorems are statements that have been proven to be true. The theorems of Boolean algebra are very similar to those of standard algebra, such as commutivity and associativity. Proofs of the Boolean algebra theorems can be found in an introductory digital design textbook.

#### **BASIC THEOREMS**

**Table 4.5** lists the theorems for a single variable and **Table 4.6** lists the theorems for two or more variables. These tables illustrate the *principle of duality* exhibited by the Boolean theorems: Each theorem has a dual in which, after swapping all ANDs with ORs and all 1s with 0s, the statement is still true.

The tables also illustrate the *precedence* of the Boolean operations: the order in which operations are performed when not specified by parenthesis. From highest to lowest, the precedence is NOT, AND then OR. For example, the distributive law includes the expression "A + B•C." This is equivalent to

Fig 4.13 — Equivalent gates from DeMorgan's Theorem: Each gate in column A is equivalent to the opposite gate in column B. The Boolean equations in column C formally state the equivalences.

"A + (B•C)." The parenthesis around (B•C) can be left out since an AND operation has higher priority than an OR operation. Precedence for Boolean algebra is similar to the convention of standard algebra: raising to a power, then multiplication, then addition.

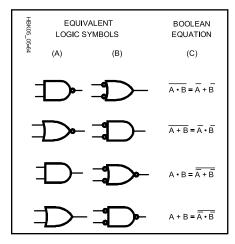

#### **DeMORGAN'S THEOREM**

One of the most useful theorems in Boolean algebra is DeMorgan's Theorem:

$$\overline{A \cdot B} = \overline{A} + \overline{B}$$

and its dual

$$\overline{A + B} = \overline{A} \cdot \overline{B}$$

# Table 4.5 Boolean Algebra Single Variable Theorems

Identities:  $A \cdot 1 = A$  A + 0 = ANull elements:  $A \cdot 0 = 0$  A + 1 = 1Idempotence:  $A \cdot A = A$  A + A = AComplements:  $A \cdot \overline{A} = 0$   $A + \overline{A} = 1$ Involution:  $\overline{(A)} = A$

The truth table in **Table 4.7** proves these statements. DeMorgan's Theorem provides a way to simplify the complement of a large expression. It also enables a designer to interchange a number of equivalent gates, as shown by **Fig 4.13**.

The equivalent gates show that the duality principle works with symbols the same as it does for Boolean equations: just swap ANDs with ORs and switch the bubbles. For example, the NAND gate — an AND gate followed by an inverter bubble — becomes an OR gate preceded by two inverter bubbles. DeMorgan's Theorem is important because it means any logical function can be implemented using either inverters and AND gates or inverters and OR gates. Also, the ability to change placement of the bubbles using DeMorgan's Theorem is useful in dealing with mixed logic, to be discussed next.

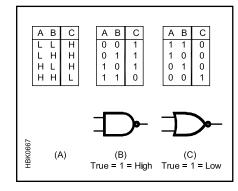

#### **POSITIVE AND NEGATIVE LOGIC**

The truth tables shown in the figures in this chapter are drawn for positive logic. In *positive logic*, or *high true*, a higher voltage means true (logic 1) while a lower voltage means false (logic 0). This is also referred to as *active high*:

a signal performs a named action or denotes a condition when it is "high" or 1. In *negative logic*, or *low true*, a lower voltage means true (1) and a higher voltage means false (0). An *active low* signal performs an action or denotes a condition when it is "low" or 0.

In both logic types, true = 1 and false = 0; but whether true means high or low differs. Company databooks are drawn for general truth tables: an H for high and an L for low. (Some tables also have an X for a "don't care" state.) The function of the table can differ depending on whether it is interpreted for positive logic or negative logic.

Device data sheets often show positive logic convention, or positive logic is assumed. However, a signal into an IC is represented with a bar above it, indicating that the "enable" on that wire is active low — it does not mean negative logic (0 V = a logical 1) is used! Similarly a bubble on the input of a logic element also usually means active low. These can be sources of confusion.

**Fig 4.14** shows how a general truth table differs when interpreted for different logic types. The same truth table gives two equivalent gates: positive logic gives the function of a NAND gate while negative logic gives the function of a NOR gate.

Note that these gates correspond to the

# Table 4.6 Boolean Algebra Multivariable Theorems

Commutativity:  $A \cdot B = B \cdot A$ A + B = B + A

Associativity:  $(A \cdot B) \cdot C = A \cdot (B \cdot C)$

(A + B) + C = A + (B + C)

Distributivity:  $(A + B) \cdot (A + C) = A + B \cdot C$

$A \bullet B + A \bullet C = A \bullet (B + C)$

Covering:  $A \cdot (A + B) = A$

$A + A \cdot B = A$

Combining:  $(A + B) \cdot (A + \overline{B}) = A$

$A \bullet B + A \bullet B = A$

Consensus:  $A \cdot B + \overline{A} \cdot C + B \cdot C = A \cdot B + \overline{A} \cdot C$

$(A + B) \cdot (\overline{A} + C) \cdot (B + C) = (A + B) \cdot (\overline{A} + C)$

$A + \overline{A}B = A + B$

Fig 4.14 — (A) A general truth table, (B) a truth table and NAND symbol for positive logic and (C) a truth table and NOR symbol for negative logic.

#### Table 4.7 DeMorgan's Theorem

(A) and (B) are statements of DeMorgan's Theorem. The truth table at (C) is proof of these statements: (A) is proven by the equivalence of columns 6 and 10 and (B) by columns 8 and 9.

equivalent gates from DeMorgan's Theorem. A bubble on an input or output terminal indicates an active low device. The absence of bubbles indicates an active high device.

Like the bubbles, signal names can be used to indicate logic states. These names can aid the understanding of a circuit by indicating control of an action (GO,/ENABLE) or detection of a condition (READY, /ERROR). The action or condition occurs when the signal is in its active state. When a signal is in its active state, it is called *asserted*; a signal not in its

active state is called negated or deasserted.

A prefix can easily indicate a signal's active state. Active low signals are preceded by a symbol such as /, |, ! or # (for example /READY or !READY). Active low signals are also denoted by an overscore, such as CL. Active high signals have no prefix or overscore. As an example, see the truth table for a flip-flop later in this chapter. Standard practice is that the signal name and input pin match (have the same active level). For example, an input with a bubble (active low)

may be called /READY, while an input with no bubble (active high) is called READY. Output signal names should always match the device output pin.

In this chapter, positive logic is used unless indicated otherwise. Although using mixed logic can be confusing, it does have some advantages. Mixed logic combined with DeMorgan's Theorem can promote more effective use of available gates. Also, well-chosen signal names and placement of bubbles can promote more understandable logic diagrams.

### 4.5 Sequential Logic

The previous section discussed combinational logic, whose outputs depend only on the present inputs. In contrast, in *sequential logic* circuits, the new output depends not only on the present inputs but also on the present outputs. The present outputs depended on the previous inputs and outputs and those earlier outputs depended on even earlier inputs and outputs and so on. Thus, the present outputs depend on the previous *sequence of inputs* and the system has *memory*. Having the outputs become part of the new inputs is known as *feedback*.

# 4.5.1 Synchronicity and Control Signals

When a combinational circuit is given a set of inputs, the outputs take on the expected values after a propagation delay during which the inputs travel through the circuit to the output. In a sequential circuit, however, the travel through the circuit is more complicated. After application of the first inputs and one propagation delay, the outputs take on the resulting state; but then the outputs start trickling back through and, after a second propagation delay, new outputs appear. The same happens after a third propagation delay. With propagation delays in the nanosecond range, this cycle around the circuit is rapidly and continually generating new outputs. A user needs to know when the outputs are valid.

There are two types of sequential circuits: synchronous circuits and asynchronous circuits, which are analyzed differently for valid outputs. In *asynchronous* operation, the outputs respond to the inputs immediately after the propagation delay. To work properly, this type of circuit must eventually reach a *stable* state: the inputs and the fed back outputs result in the new outputs staying the same. When the nonfeedback inputs are changed, the feedback cycle needs to eventually reach a new stable state. Generally, the output of this type of logic is not valid until the last input has changed,

and enough time has elapsed for all propagation delays to have occurred.

In *synchronous* operation, the outputs change state only at specific times. These times are determined by the presence of a particular input signal: a clock, toggle, latch or enable. Synchronicity is important because it ensures proper timing: all the inputs are present where needed when the control signal causes a change of state.

#### **CONTROL SIGNALS**

Some authors vary the meanings slightly for the different control signals. The following is a brief illustration of common uses, as well as showing uses for noun, verb and adjective. Enabling a circuit generally means the control signal goes to its asserted level, allowing the circuit to change state. *Latch* implies memory: a latch circuit can store a bit of information. A latch signal can cause a circuit to keep its present state indefinitely. Gate can have several meanings, some unrelated to synchronous control. For example, a gate can be a signal used to trigger the passage of other signals through a circuit. A gate can also be a logic circuit with two or more inputs and one output, as used earlier in this chapter. Of course, "gate" can also be one of the electrodes of an FET as described in another chapter. To toggle means a signal changes state, from 1 to 0 or

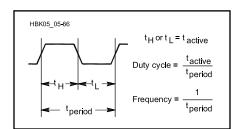

Fig 4.15 — Clock signal terms. The duty cycle would be  $t_{\rm H}$  /  $t_{\rm PERIOD}$  for an active high signal and  $t_{\rm L}$  /  $t_{\rm PERIOD}$  for an active low signal.

vice versa. A *clock* signal is one that toggles at a regular rate.

Clock control is the most common method of synchronizing logic circuits, so it has some additional terms as illustrated by **Fig 4.15**. The *clock period* is the time between successive transitions in the same direction; the *clock frequency* is the reciprocal of the period. A *pulse* or *clock tick* is the first edge in a clock period, or sometimes the period itself or the first half of the period. The *duty cycle* is the percentage of time that the clock signal is at its asserted level. A common application of the use of clock pulses is to limit the input to a logic circuit such that the circuit is only enabled on one clock phase; that is the inputs occur before the clock changes to a logic 1.

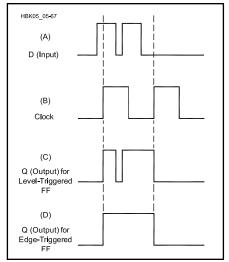

Fig 4.16 — Level-triggered vs edgetriggered for a D flip-flop: (A) input D, (B) clock input, (C) output Q for leveltriggered: circuit responds whenever clock is 1. (D) output Q for edge-triggered: circuit responds only at rising edge of clock. Notice that the short negative pulse on the input D is not reproduced by the edge-triggered flip-flop.

The outputs are sampled only after this point; perhaps when the clock next changes back to a logic 0.

The reaction of a synchronous circuit to its control signal is static or dynamic. Static, gated or level-triggered control allows the circuit to change state whenever the control signal is at its active or asserted level. Dynamic, or edge-triggered, control allows the circuit to change state only when the control signal changes from unasserted to asserted. By convention, a control signal is active high if state changes occur when the signal is high or at the rising edge and active low in the opposite case. Thus, for positive logic, the convention is enable = 1 or enable goes from 0 to 1. This transition from 0 to 1 is called positive edge-triggered and is indicated by a small triangle inside the circuit box. A circuit responding to the opposite transition, from 1 to 0, is called negative edge-triggered, indicated by a bubble with the triangle.

Whether a circuit is level-triggered or edgetriggered can affect its output, as shown by Fig 4.16. Input D includes a very brief pulse, called a *glitch*, which may be caused by noise. The differing results at the output illustrate how noise can cause errors. We have both edge and level triggered circuits available so that we can meet the requirements of our particular design.

#### 4.5.2 Flip-Flops

Flip-flops are the basic building blocks of sequential circuits. A flip-flop is a device with two stable states: the set state (1) and the reset or cleared state (0). The flip-flop can be placed in one or the other of the two states by applying the appropriate input. Since a common use of flip-flops is to store one bit of information, some use the term latch interchangeably with flip-flop. A set of latches, or flip-flops holding an n-bit number is called a register. While gates have special symbols, the schematic symbol for most sequential logic components is a rectangular box with the circuit name or abbreviation, the signal names and assertion bubbles. For flip-flops, the circuit name is usually omitted since the signal names are enough to indicate a flip-flop and its type. The four basic types of flip-flops are the S-R, D, T and J-K. The most common flip-flops available to Amateurs today are the J-K and D- flip-flops; the others can be synthesized if needed by utilizing these two varieties.

#### TRIGGERING A FLIP-FLOP

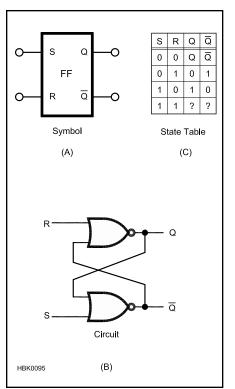

Although the S-R (Set-reset) flip flop is no longer generally available or used, it does provide insight in basic flip-flop operations and triggering. It is also not uncommon to build S-R flip-flops out of gates for jobs such as switch contact debouncing. In **Fig 4.17** the

Fig 4.17 — Unclocked S-R Flip-Flop. (A) schematic symbol. (B) circuit diagram. (C) state table or truth table.

symbol for an S-R flip flop and its truth table are accompanied by a logic implementation, using NAND gates. As the truth table shows, this basic implementation requires a positive or logic 1 input on the set input to put the flip-flop in the Q or set state. Remove the input, and the flip flop stays in the Q state, which is what is expected of a flip-flop. Not until the S input receives a logic 1 input does the flip- flop change state and go to the reset or Q=0 state.

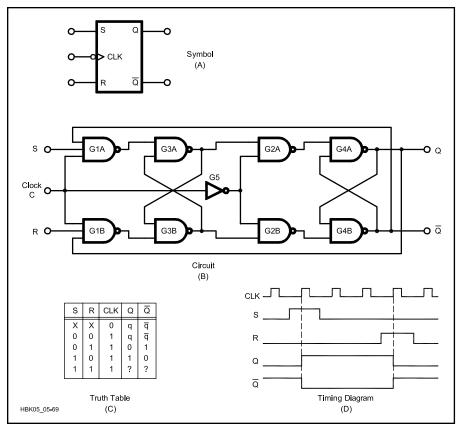

Note that the input can be a short pulse or a level; as long as it is there for some minimum duration (established by the propagation delay of the gates used), the flip-flop will respond. By contrast the clocked S-R flip-flop in **Fig 4.18** requires both a positive level to be present at either the S or R inputs and a positive clock pulse. The clock pulse is ANDed with the S or R input to trigger the flip-flop. In this case the flip-flop shown is implemented with a set of NOR gates.

A final triggering method is edge triggering. Here, instead of using the clock pulse as shown in the timing diagram of Fig 4.18, just the edge of the clock pulse is used. The edge-triggered flip-flop helps solves a problem with noise. Edge-triggering minimizes the time during which a circuit responds to its inputs: the chance of a glitch occurring during

Fig 4.18 — Master-Slave Flip-Flop. (A) logic symbol. (B) NAND gate implementation. (C) truth table. (D) timing diagram.

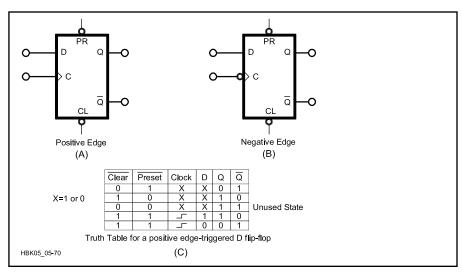

Fig 4.19 — (A & B) The D flip-flop. (C) A truth table for the positive edge-triggered D flip-flop.

Fig 4.20 — (A) JK flip-flop. (B) JK flip-flop truth table.

the nanosecond transition of a clock pulse is remote. A side benefit of edge-triggering is that only one new output is produced per clock period. Edge-triggering is denoted by a small rising-edge or falling-edge symbol in the clock column of the flip-flop's truth table. It can also appear, instead of the clock triangle, inside the schematic symbol.

#### **MASTER/SLAVE FLIP-FLOP**

One major problem with the simple flipflop shown up to now is the question of when is there a valid output. Suppose a flip-flop receives input that causes it to change state; at the same time the output of this flip-flop is being sampled to control some other logic element. There is a real risk here that the output will be sampled just as it is changing and thus the validity of the output is questionable.

A solution to this problem is a circuit that samples and stores its inputs before changing its outputs. Such a circuit is built by placing two flip-flops in series; both flip-flops are triggered by a common clock but an inverter on the second flip-flop's clock input causes it to be asserted only when the first flip-flop is not asserted. The action for a given clock pulse is as follows: The first, or master, flip-flop can

change only when the clock is high, sampling and storing the inputs. The second, or slave, flip-flop gets its input from the master and changes when the clock is low. Hence, when the clock is 1, the input is sampled; then when the clock becomes 0, the output is generated. Note that a bubble may appear on the schematic symbol's clock input, reminding us that the output appears when the clock is asserted low. This is conventional for TTL-style J-K flip-flops, but it can be different for CMOS devices.

The master/slave method isolates output changes from input changes, eliminating the problem of series-fed circuits. It also ensures only one new output per clock period, since the slave flip-flop responds to only the single sampled input. A problem can still occur, however, because the master flip-flop can change more than once while it is asserted; thus, there is the potential for the master to sample at the wrong time. There is also the potential that either flip-flop can be affected by noise.

A master-slave, S-R clocked input flip-flop synthesized from NAND gates, Fig 4.18B, is accompanied by its logic symbol, Fig 4.18A. From the logic symbols you can tell that the

output changes on a negative-going clock edge.

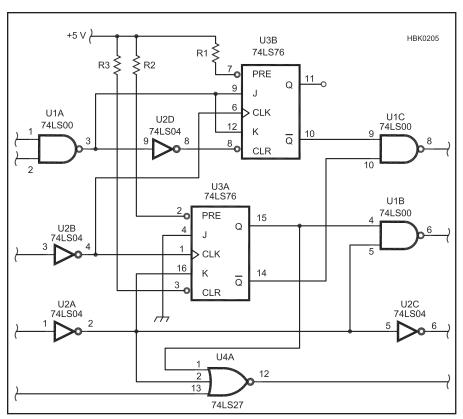

G3A and G3B form the master set-rest flip-flop, and G4A and G4B the slave flip flop. The input signals S and R are controlled by the positive going edge of the clock through gates G1A and G1B. G2A and G2B control the inputs into the slave flip-flop; these inputs are the outputs of the master flip-flop. Note G5 inverts the clock; thus while the positive-going edge places new data into the master flip-flop, the other edge of the clock transfers the output of the master into the slave on the following negative clock edge.

#### D FLIP-FLOP

In a D (data) flip-flop, the *data* input is transferred to the outputs when the flip-flop is enabled. The logic level at input D is transferred to Q when the clock is positive; the Q output retains this logic level until the next positive clock pulse (see **Fig 4.19**). The truth table summarizes this operation. If D = 1 the next clock pulse makes Q = 1. If D = 0, the next clock pulse makes Q = 0. A D flip-flop is useful to store one bit of information. A collection of D flip-flops forms a register.

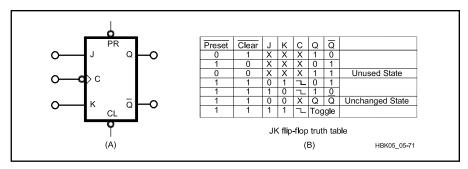

#### J-K FLIP-FLOP

The J-K flip-flop, shown schematically in Fig 4.20A, has five inputs. The unit shown uses both positive active inputs (the J and K inputs) and negative active inputs (note the bubbles on the C or clock, PR or preset and CL or clear inputs). With these inputs almost any other type of flip-flop may be synthesized.

The truth table of Fig 4.20B provides an explanation. Lines (rows) 1 and 2 show the preset and clear inputs and their use. These are active low, meaning that when one (and only one) of them goes to a logic 0, the flip-flop responds, just as if it was a S-R or set-reset flip-flop. Make PR a logic 0, and leave CL a logic 1, and the flip-flop goes into the Q = 1 state (line 1). Do the reverse (line 2) – PR = 1, CL = 0 and the flip-flop goes into a Q' = 1 state. When these two inputs are used, J, K and C are marked as X or don't care, because the PR and CL inputs override them. Line 3 corresponds to the unused state of the R-S flip-flop.

Line 5 shows that if J=1 and K=0, the next clock transition from high to low sets Q=1 and Q'=0. Alternately, line 4 shows J=0 and K=1 sets Q=0 and Q'=1. Therefore if a signal is applied to J, and the inverted signal sent to K, the J-K flip-flop will mimic a D flip-flop, echoing its input.

The most unique feature of the J-K flip-flop is line 7. If both J and K are connected to a 1, then each clock 1 to 0 transition will flip or toggle the flop-flop. Thus the J-K flip-flop can be used as a T flip-flop, as in a ripple counter (see the following **Counters** section.)

**Table 4.8** summarizes D and J-K flip-flops.

Table 4.8

#### Summary of Standard Flip-Flops

q = current state Q = next state

X = don't care

| Flip-Flop<br>Type | Symbol Truth Table                      |                                                             | Characteristic<br>Equation                                                        | Excitation<br>Table                                                                 |  |

|-------------------|-----------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|

| D                 | — □ Q — — — — — — — — — — — — — — — — — | D CLK Q<br>X _4 q<br>0 _4 0<br>1 _4 1                       | Q = D • CLK                                                                       | q Q D CLK       0 0 X →       0 1 1 →       1 0 0 →       1 1 X →                   |  |

| JK                | — J Q —<br>→ к Q —                      | J K CLK Q X X _ 4 q 0 0 _ 4 q 1 1 _ 4 0 1 0 _ 4 1 1 1 _ 4 t | $Q = (J \cdot \overline{q} + \overline{K} \cdot q) \cdot CLK$ Positive Edge Clock | q Q J K CLK       0 0 0 X _ 4       0 1 1 X _ 4       1 0 X 1 _ 4       1 1 X 0 _ 4 |  |

| JK                | _ J Q                                   | J K CLK Q<br>0 0 7 0<br>0 1 7 0<br>1 0 7 1<br>1 1 7 t       | Q = (J ∙ q̄ + K̄ ∙ q ) ∙ CLK<br>Negative Edge Clock                               | 9 Q J K CLK<br>0 0 0 0 X 7<br>0 1 1 X 7<br>1 0 X 1 7<br>1 1 X 0 7                   |  |

HBK0668

t: If J = K, the clock toggles the flip-flop

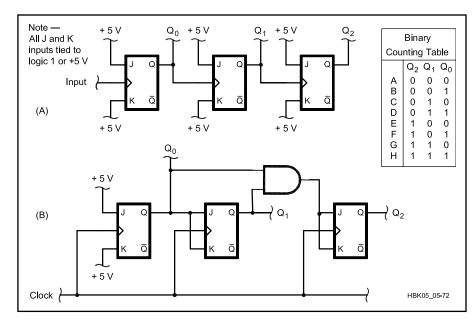

# 4.5.3 Groups of Flip-Flops COUNTERS

Groups of flip-flops can be combined to make counters. Intuitively, a counter is a circuit that starts at state 0 and sequences up through states 1, 2, 3, to m, where m is the maximum number of states available. From state m, the next state will return the counter to 0. This describes the most common counter: the *n-bit binary counter*, with n outputs corresponding to  $2^n = m$  states. Such a counter can be made from n flip-flops, as shown in Fig 4.21. This figure shows implementations for each of the types of synchronicity. Both circuits pass the data count from stage to stage. In the asynchronous counter, Fig 4.21A, the clock is also passed from stage to stage and the circuit is called *ripple* or *ripple-carry*.

The J-K flip-flop truth table shows that with PR (Preset) and CL (Clear) both positive, and therefore not effecting the operation, the flip-flop will toggle if J and K are tied to a logic 1. In Fig 4.21A the first stage has its J and K inputs permanently tied to a logic 1, and each succeeding stage has its J and K inputs tied to Q of the proceeding stage. This provides a direct ripple counter implementation.

Design of a synchronous counter is bit more

involved. It consists of determining, for a particular count, the conditions that will make the next stage change at the same clock edge when all the stages are changing.

To illustrate this, notice the binary counting table of Fig 4.21. The right-hand column represents the lowest stage of the counter. It alternates between 1 and 0 on every line. Thus, for the first stage the J and K inputs are tied to logic 1. This provides the alternation required by the counting table.

The middle column or second stage of the counter changes state right after the lower stage is a 1 (lines C, E and G). Thus if the Q output of the lowest stage is tied to the J and K inputs of the second stage, each time the output of the lowest stage is a 1 the second stage toggles on the next clock pulse.

Finally, the third column (third stage) toggles when both the first stage and the second stage are both 1s (line D). Thus by ANDing the Q outputs of the first two stages, and then connecting them to the J and K inputs of the third stage, the third stage will toggle whenever the first two stages are 1s.

There are formal methods for determining the wiring of synchronous counters. The illustration above is one manual method that may be used to design a counter of this type.

The advantage of the synchronous counter is that at any instant, except during clock pulse transition, all counter stage outputs *are correct* and delay due to propagation through the flip flops is not a problem.

In the synchronous counter, Fig 4.21B, each stage is controlled by a common clock signal.

There are numerous variations on this first example of a counter. Most counters have the ability to *clear* the count to 0. Some counters can also *preset* to a desired count. The clear and preset control inputs are often asynchronous — they change the output state without being clocked. Counters may either count up (increment) or down (decrement). *Up/down* counters can be controlled to count in either direction. Counters can have sequences other than the standard numbers, for example a BCD counter

Counters are also not restricted to changing state on every clock cycle. An n-bit counter that changes state only after m clock pulses is called a *divider* or *divide-by-m* counter. There are still  $2^n = m$  states; however, the output after p clock pulses is now p / m. Combining different divide-by-m counters can result in almost any desired count. For example, a base 12 counter can be made from a divide-by-2 and a divide-by-6 counter; a base 10 (decade) counter consists of a divide-by-2 and a BCD divide-by-5 counter.

The outputs of these counters are binary. To produce output in decimal form, the output of a counter would be provided to a binary-to-decimal decoder chip and/or an LED display.

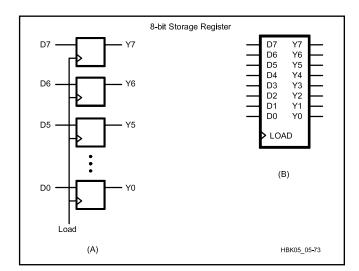

#### **REGISTERS**

Groups of flip-flops can be combined to make registers, usually implemented with D flip-flops. A *register* stores n bits of information, delivering that information in response to a clock pulse. Registers usually have asynchronous *set* to 1 and *clear* to 0 capabilities.

#### **Storage Register**

A storage register simply stores temporary information, for example, incoming information or intermediate results. The size is related to the basic size of information handled by a computer: 8 flip-flops for an 8-bit or *byte register* or 16 bits for a *word register*. **Fig 4.22** shows a typical circuit and schematic symbols for an 8-bit storage register.

#### **Shift Register**

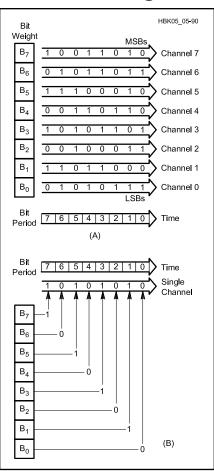

Shift registers also store information and provide it in response to a clock signal, but they handle their information differently: When a clock pulse occurs, instead of each flip-flop passing its result to the output, the flip-flops pass their data to each other, up and down the row. For example, in up mode, each flip-flop receives the output of the preceding flip-flop. A data bit starting in flip-flop D0 in a left

Fig 4.21 — Three-bit binary counter using J-K flip-flops: (A) asynchronous or ripple, (B) synchronous.

shifter would move to D1, then D2 and so on until it is shifted out of the register. If a 0 was input to the least significant bit, D0, on each clock pulse then, when the last data bit has been shifted out, the register contains all 0s.

Shift registers can be left shifters, right shifters or controlled to shift in either direction. The most general form, a *universal shift register*, has two control inputs for four states: Hold, Shift right, Shift left and Load. Most also have asynchronous inputs for preset, clear and parallel load. The primary use of shift registers is to convert parallel information to serial or vice versa. Additional uses for a shift register are to delay or synchronize data, and to multiply or divide a number by a factor 2<sup>n</sup>. Data can be delayed simply by

taking advantage of the Hold feature of the register control inputs. Multiplication and division with shift registers is best explained by example: Suppose a 4-bit shift register currently has the value 1000 = 8. A right shift results in the new parallel output 0100 = 4 = 8/2. A second right shift results in 0010 = 2 = (8/2)/2. Together the 2 right shifts performed a division by  $2^2$ . In general, shifting right n times is equivalent to dividing by  $2^n$ . Similarly, shifting left multiplies by  $2^n$ . This can be useful to compiler writers to make a computer program run faster.

#### 4.5.4 Multivibrators

Multivibrators are a general type of circuit

with three varieties: bistable, monostable and astable. The only truly digital multivibrator is bistable, having two stable states. The flipflop is a *bistable multivibrator*: both of its two states are stable; it can be triggered from one stable state to the other by an external signal. The other two varieties of multivibrators are partly analog circuits and partly digital. While their output is one or more pulses, the internal operation is strictly analog.

#### MONOSTABLE MULTIVIBRATOR

A monostable or one-shot multivibrator has one energy-storing element in its feedback paths, resulting in one stable and one quasistable state. It can be switched, or triggered, to its quasi-stable state; then returns to the stable state after a time delay. Thus, when triggered, the one-shot multivibrator puts out a pulse of some duration, T.

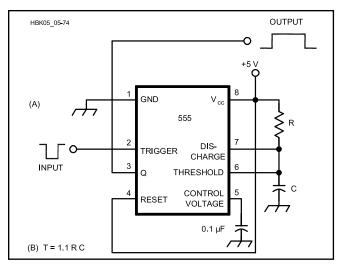

A very common integrated circuit used for non-precision generation of a signal pulse is the 555 timer IC. Fig 4.23 shows a 555 connected as a one-shot multivibrator. The one-shot is activated by a negative-going pulse between the trigger input and ground. The trigger pulse causes the output (Q) to go positive and capacitor C to charge through resistor R. When the voltage across C reaches two-thirds of  $V_{\rm CC}$ , the capacitor is quickly discharged to ground and the output returns to 0. The output remains at logic 1 for a time determined by

T = 1.1 RC

where:

R = resistance in ohms, and C = capacitance in farads.

A very common, but again, non-precision application of this circuit is the generation of a delayed pulse. If there is a requirement

Fig 4.22 — An eight-bit storage register: (A) circuit and (B) schematic symbol.

Fig 4.23 — (A) A 555 timer connected as a monostable multivibrator. (B) The equation to calculate values where T is the pulse duration in seconds, R is in ohms and C is in farads.

to generate a 50  $\mu$ s pulse, but delayed from a trigger by 20 ms, two 555s might be used. The first 555, configured as an astable multivibrator, generates the 20-ms pulse, and the trailing edge of the 20-ms pulse is used to trigger a second 555 that in turn generates the 10  $\mu$ s pulse. See the **Analog Basics** chapter for more information on the 555 timer and related circuits.

#### **ASTABLE MULTIVIBRATOR**

An astable or free-running multivibrator has two energy-storing elements in its feedback paths, resulting in two quasi-stable states. It continuously switches between these two states without external excitation. Thus, the astable multivibrator puts out a sequence of pulses. By properly selecting circuit components, these pulses can be of a desired frequency and width.

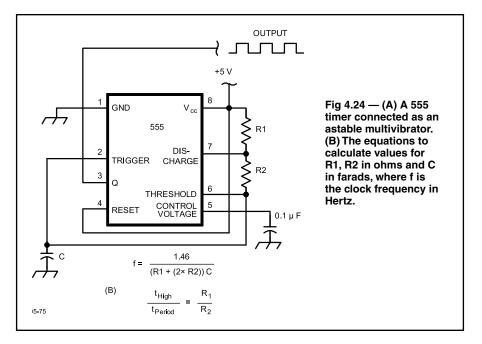

**Fig 4.24** shows a 555 timer IC connected as an astable multivibrator. The capacitor C charges to two-thirds  $V_{CC}$  through R1 and R2 and discharges to one-third  $V_{CC}$  through R2. The ratio R1: R2 sets the asserted high duty cycle of the pulse:  $t_{HIGH}/t_{PERIOD}$ . The output frequency is determined by:

$$f = \frac{1.46}{(R1 + 2 R2) C}$$

where

R1 and R2 are in ohms, C is in farads and f is in hertz.

It may be difficult to produce a 50% duty cycle due to manufacturing tolerance for the resistors R1 and R2. One way to ensure a 50% duty cycle is to run the astable multivibrator at 2f and then divide by 2 with a toggle flip-flop.

Astable multivibrators, and the 555 integrated circuit in particular, are very often used to generate clock pulses. Although this

is a very inexpensive and minimum hardware approach, the penalty is stability with temperature. Since the frequency and the pulse dimensions are set by resistors and capacitors, drift with temperature and to some extent aging of components will result in changes with time. This is no different than the problem faced by designers of L-C controlled VFOs.

### 4.6 Digital Integrated Circuits

Integrated circuits (ICs) are the cornerstone of digital logic devices. Modern technology has enabled electronics to become smaller and smaller in size and less and less expensive. Much of today's complex digital equipment would be impossible to build with discrete transistors and discrete components.

An IC is a miniature electronic module of components and conductors manufactured as a single unit. All you see is a ceramic or black plastic package and the silver-colored pins sticking out. Inside the package is a piece of material, usually silicon, created (fabricated) in such a way that it conducts an electric current to perform logic functions, such as a gate, flip-flop or decoder.

As each generation of ICs surpassed the previous one, they became classified accord-

ing to the number of gates on a single chip. These classifications are roughly defined as:

Small-scale integration (SSI):

10 or fewer gates on a chip.

Medium-scale integration (MSI): 10-100 gates.

Large-scale integration (LSI):

100-1000 gates. Very-large-scale integration (VLS)

Very-large-scale integration (VLSI): 1000 or more gates.

Though SSI and MSI logic chips are still useful for building circuits to handle very simple tasks, it is more common to see them either used along with or completely replaced by programmable logic arrays and microcontrollers. In many cases you will see the smaller logic circuits referred to as "glue logic."

# 4.6.1 Comparing Logic Families

When selecting devices for a circuit, a designer is faced with choosing between many families and subfamilies of logic ICs. The determination of which logic subfamily is right for a specific application is based upon several desirable characteristics: logic speed, power consumption, fan-out, noise immunity and cost. From a practical viewpoint, the primary IC families available and in common use today are CMOS, with TTL a distant second place. Within these families, there are tradeoffs that can be made with respect to individual circuit capabilities, especially in the areas of speed and power consumption. Except under the most demanding circumstances, normal commercial

Fig 4.25 — Nonverting buffers used to increase fan-out: Gate A (fan-out = 2) is connected to two buffers, B and C, each with a fan-out of 2. Result is a total fanout of 4.

grade temperature rating will do for amateur service.

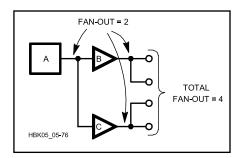

#### **FAN-OUT**

Fan-out is a term with which you will need to become familiar when working with TTL logic families such as 7400, 74LS or 74S. A gate output can supply only a limited amount of current. Therefore, a single output can only drive a limited number of inputs. The measure of driving ability is called fan-out, expressed as the number of inputs (of the same subfamily) that can be driven by a single output. If a logic family that is otherwise desirable does not have sufficient fan-out, consider using noninverting buffers to increase fan-out, as shown by **Fig 4.25**.

Another approach is to use a CMOS logic family. These families typically have output drivers capable of sourcing or sinking 20 to 25 mA, and input current leakage in the microampere range. Thus, fan-out is seldom a problem when using these devices.

#### **NOISE IMMUNITY**

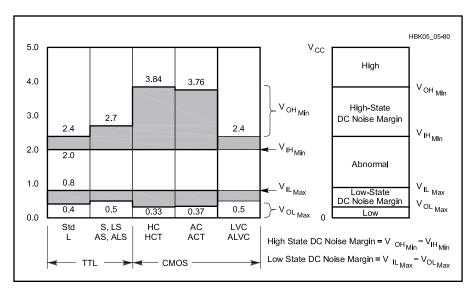

The noise margin was illustrated in Fig 4.2. The choice of voltage levels for the binary states determines the noise margin. If the gap is too small, a spurious signal can too easily produce the wrong state. Too large a gap, however, produces longer, slower transitions and thus decreased switching speeds.

Circuit impedance also plays a part in noise immunity, particularly if the noise is from external sources such as radio transmitters. At low impedances, more energy is needed to change a given voltage level than at higher impedances.

#### 4.6.2 Bipolar Logic Families

Two broad categories of digital logic ICs are *bipolar* and *metal-oxide semiconductor* (MOS). Numerous manufacturing techniques have been developed to fabricate each type. Each surviving, commercially available family has its particular advantages and disadvantages and has found its own special niche in the market. The designer is cautioned, how-

ever, that sometimes this niche is simply the ongoing maintenance of old products. There are still very old logic families available for reasonable prices that would be considered quite obsolete and generally not suitable for new designs.

Bipolar semiconductor ICs usually employ NPN junction transistors. (Bipolar ICs can be manufactured using PNP transistors, but NPN transistors make faster circuits.) While early bipolar logic was faster and had higher power consumption than MOS logic, the speed difference has largely disappeared as manufacturing technology has developed.

There are several families of bipolar logic devices, and within some of these families there are subfamilies. The most-used bipolar logic family is transistor-transistor logic (TTL). Another bipolar logic family, Emitter Coupled Logic (ECL), has exceptionally high speed but high power consumption.

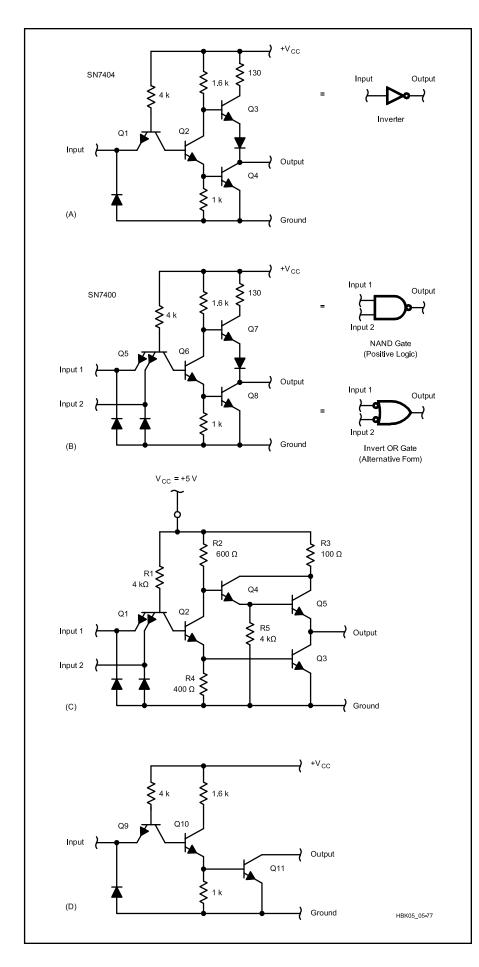

# TRANSISTOR-TRANSISTOR LOGIC (TTL)

The TTL family saw widespread acceptance through the 1960s, 1970s and 1980s because it was fast compared to early MOS and CMOS logic, and has good noise immunity. It was by far the most commonly used logic family for a couple of decades. Though TTL logic is not in widespread use today for new designs, the device numbering system devised for TTL chips survives to this day for newer technologies. You will also often see TTL, especially the later low power, higher speed TTL subfamilies, in various equipment you may use and repair.

#### **TTL Subfamilies**

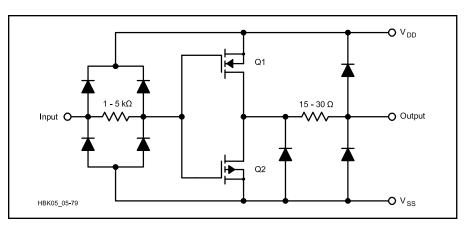

The original standard TTL used bipolar transistors and "totem-pole" outputs (see **Fig 4.26A** and B), which were a great improvement over the earlier diode-transistor logic (DTL) and resistor-transistor logic (RTL). Still, TTL logic consumed quite a bit of power

even at idle, and there were limits on how many inputs could be driven by a single output. Later versions used Schottky diodes to greatly improve switching speed, and reduced power requirements were introduced.

TTL IC identification numbers begin with either 54 or 74. The 54 prefix denotes an extended military temperature range of –55 to 125 °C, while 74 indicates a commercial temperature range of 0 to 70 °C. The next letters, in the middle of the TTL device number, indicate the TTL subfamily. Following the subfamily designation is a 2, 3 or 4-digit device-identification number. For example, a 7400 is a standard TTL NAND gate and a 74LS00 is a low-power Schottky NAND gate (The NAND gate is the workhorse TTL chip). A partial list of TTL subfamilies includes:

|     | 74xx    | standard TTL       |

|-----|---------|--------------------|

| Н   | 74Hxx   | High-speed         |

| L   | 74Lxx   | Low-power          |

| S   | 74Sxx   | Schottky           |

| F   | 74Fxx   | Fairchild Advanced |

|     |         | Schottky           |

| LS  | 74LSxx  | Low-power Schottky |

| AS  | 74ASxx  | Advanced Schottky  |

| ALS | 74ALSxx | Advanced           |

|     |         | Low-power Schottky |

|     |         |                    |

Each subfamily is a compromise between speed and power consumption. **Table 5.9** shows some of these characteristics. Because the speed-power product is approximately constant, less power consumption generally results in lower speed and vice versa. The advanced low power Schottky devices (ALS, F) offer both increased speed and reduced power consumption. Historically, an additional consideration to the speed-versus-power trade-off has been the cost trade-off. For the amateur, this is not nearly the factor it once was as component costs are relatively low for the newer, faster, lower powered parts.

When a TTL gate changes state, the amount of current that it draws changes rapidly. These

Table 4.9 TTL and CMOS Subfamily Performance Characteristics

| TTL Family                 | Propagation | Per Gate Power   | Speed Power Product |

|----------------------------|-------------|------------------|---------------------|

| ·                          | Delay (ns)  | Consumption (mW) | (pico-joules)       |

| Standard                   | 9           | 10               | 90                  |

| L                          | 33          | 1                | 33                  |

| Н                          | 6           | 22               | 132                 |

| S                          | 3           | 20               | 60                  |

| F                          | 3           | 8.5              | 25.5                |

| LS                         | 9           | 2                | 18                  |

| AS                         | 1.6         | 20               | 32                  |

| ALS                        | 5           | 1.3              | 6.5                 |

| CMOS Family Operating with |             |                  |                     |

| $4.5 < V_{CC}$ | <5.5 V | f=100 kHz | f=1 MHz | f=10 MHz | f=100 kHz | f=1 MHz | f=10 MHz |

|----------------|--------|-----------|---------|----------|-----------|---------|----------|

| HC             | 18     | 0.0625    | 0.6025  | 6.0025   | 1.1       | 10.8    | 108      |

| HCT            | 18     | 0.0625    | 0.6025  | 6.0025   | 1.1       | 10.8    | 108      |

| AC             | 5.25   | 0.080     | 0.755   | 7.505    | 0.4       | 3.9     | 39       |

| ACT            | 4.75   | 0.080     | 0.755   | 7.505    | 0.4       | 3.6     | 36       |

|                |        |           |         |          |           |         |          |

changes in current, called switching transients, appear on the power supply line and can cause false triggering of other devices. For this reason, the power bus should be adequately decoupled. For proper decoupling of TTL circuits, connect a 0.01 to 0.1 µF capacitor from V<sub>CC</sub> to ground near each device to minimize the transient currents caused by device switching and magnetic coupling. These capacitors must be low-inductance, highfrequency RF capacitors (ceramic capacitors are preferred). In addition, a large-value (50 to 100 µF) capacitor should be connected from V<sub>CC</sub> to ground somewhere on the board to accommodate the continually changing I<sub>CC</sub> requirements of the total V<sub>CC</sub> bus line. These are generally low-inductance tantalum capacitors.

#### Darlington and Open-Collector Outputs

Fig 4.26C and D show variations from the totem-pole configuration. They are the Darlington transistor pair and the open-collector configuration respectively.

The Darlington pair configuration replaces the single transistor Q4 with two transistors, Q4 and Q5. The effect is to provide more current-sourcing capability in the high state. This has two benefits: (1) the rise time is decreased and (2) the fan-out is increased.

Transistor(s) on the output in both the totem-pole and Darlington configurations provide active pull-up. Omitting the transistor(s) and providing an external resistor for passive pull-up gives the open-collector configuration. This configuration, unfortunately, results in slower rise time, since a relatively large external resistor must be used. The technique has some very useful applications, however: driving other devices, performing wired logic, busing and interfacing between logic devices.

Devices that need other than a 5-V supply can be driven with the open-collector output by substituting the device for the external resistor. Example devices include LEDs, relays and solenoids. Inductive devices like relay coils and solenoids need a protection diode across the coil. You must pay attention to the current ratings of open-collector outputs in such applications. You may need a switching transistor to drive some relays or other high-current loads.

Fig 4.26 — Example TTL circuits and their equivalent logic symbols: (A) an inverter and (B) a NAND gate, both with totem-pole outputs. (C) A NAND gate with a Darlington output. (D) A NAND gate with an open-collector output. (Indicated resistor values are typical. Identification of transistors is for text reference only. These are not discrete components but parts of the silicon die.)

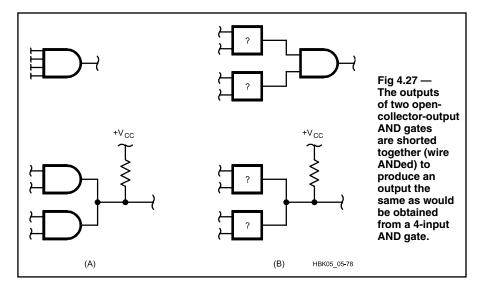

Open-collector outputs can perform wired logic, rather than gated IC logic, by wire-ANDing the outputs. This can save the designer an AND gate, potentially simplifying the design. Wire-ANDed outputs are several open-collector outputs connected to a single external pull-up resistor. The overall output, then, will only be high when all pull-down transistors are OFF (all connected outputs are high), effectively performing an AND of the connected outputs. If any of the connected outputs are low, the output after the external resistor will be low. Fig 4.27 illustrates the wire-ANDing of open-collector outputs.

The wire-ANDed concept can be applied to several devices sharing a common bus. At any time, all but one device has a high-impedance (off) output. The remaining device, enabled with control circuitry, drives the bus output.

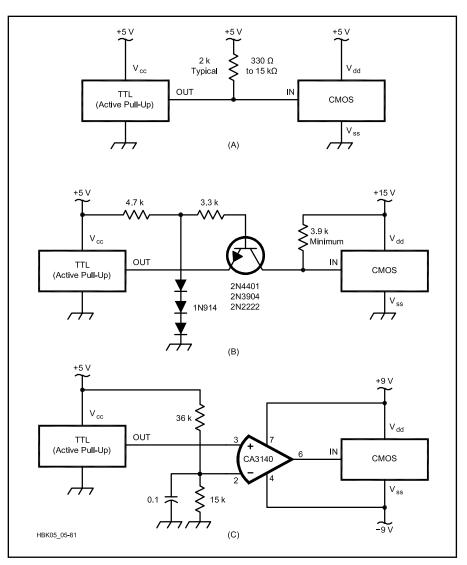

Open-collector outputs are also useful for interfacing TTL gates to gates from other logic families. TTL outputs have a minimum high level of 2.4 V and a maximum low level of 0.4 V. When driving non-TTL circuits, a pull-up resistor (typically  $2.2\,\mathrm{k}\Omega$ ) connected to the positive supply can raise the high level to 5 V. If a higher output voltage is needed, a pull-up resistor on an open-collector output can be connected to a positive supply greater than 5 V, so long as the chip output voltage and current maximums are not exceeded.

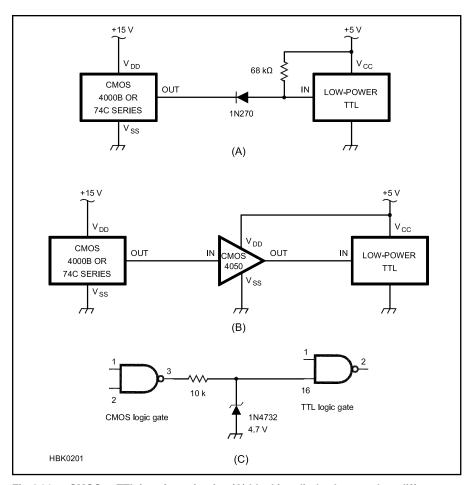

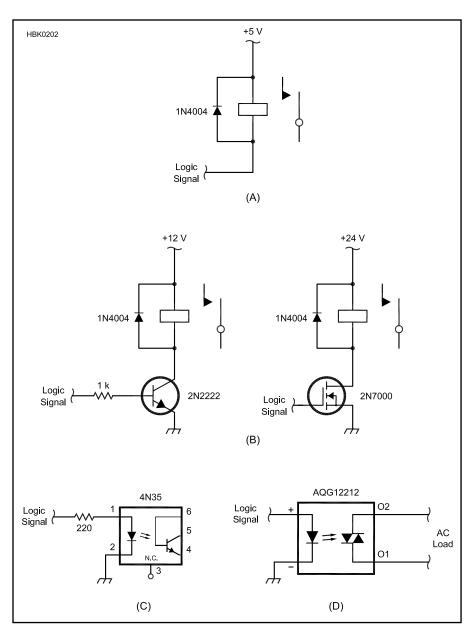

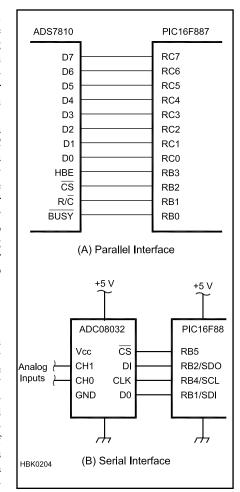

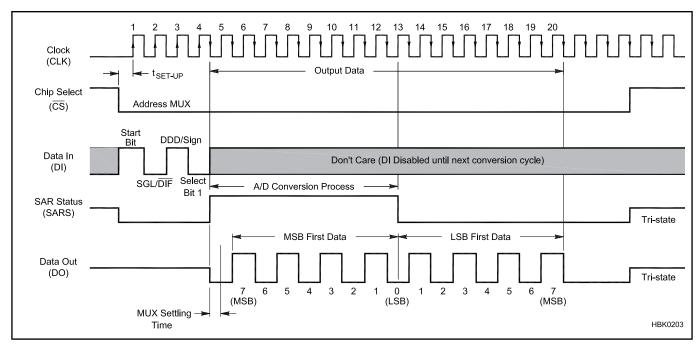

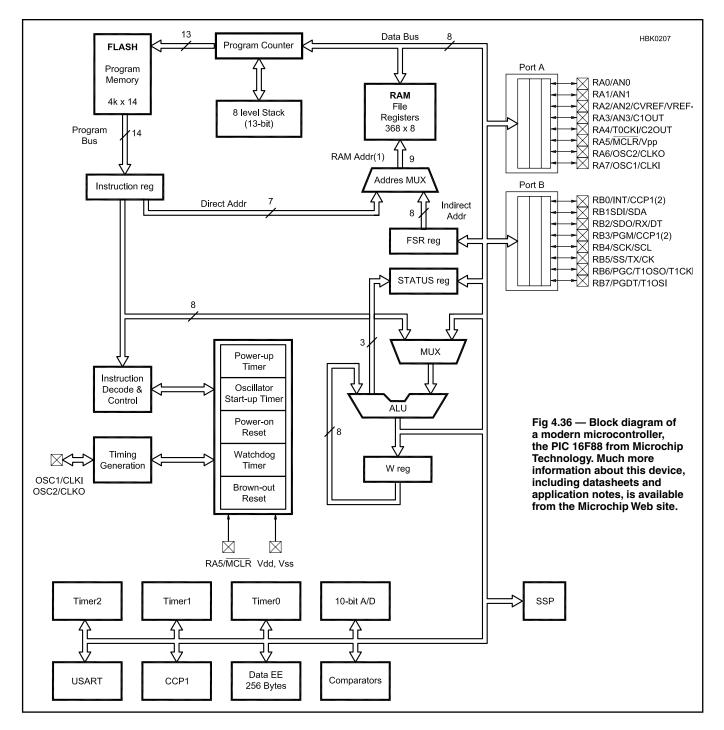

#### **Three-State Outputs**