## THE ARRL HANDBOOK FOR RADIO COMMUNICATIONS

## Practical Design and Principles — Part 1

Chapters 5-11

and here the property of the publication of the state

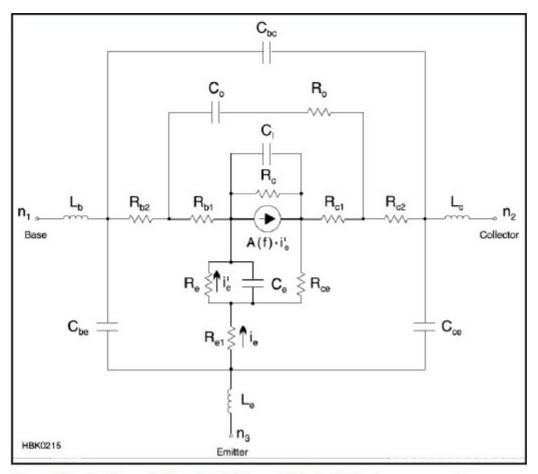

## The ARRL HANDBOOK FOR RADIO COMMUNICATIONS

Volume 1: Introduction and Fundamental Theory - Ch. 1-4

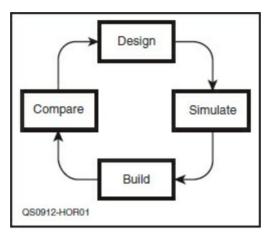

Volume 2: Practical Design and Principles PART 1 - Ch. 5-11

Volume 3: Practical Design and Principles PART 2 — Ch. 12-18

Volume 4: Antenna Systems and Radio Propagation - Ch. 19-21

Volume 5: Equipment Construction and Station Accessories - Ch. 22-24

Volume 6: Test Equipment, Troubleshooting, RFI, and Index - Ch. 25-28

#### Editor

H. Ward Silver, NØAX Contributing Editors Steven R. Ford, WB8IMY

Mark J. Wilson, K1RO Editorial Assistant Maty Weinberg, KB1EIB Technical Consultants Bob Allison, WB1GCM Michael E. Gruber, W1MG Edward F. Hare, Jr., W1RFI

Zachary H.J. Lau, W1VT

Cover Design Sue Fagan, KB1OKW Bob Inderbitzen, NQ1R

Production Michelle Bloom, WB1ENT Jodi Morin, KA1JPA David F. Pingree, N1NAS

Additional Contributors to the 2019 Edition

John Boal, K9JEB Bill Brown, WB8ELK Ken Cechura, KC9UMR Joe Eisenberg, KØNEB Dick Frey, K4XU Joel Hallas, W1ZR Rick Lindquist, WW1ME Carl Luetzelschwab, K9LA Ulrich Rohde, N1UL Larry Peterson, WA9TT John Petrich, W7FU Ajay Poddar, AC2KG Steve Stearns, K6OIK Joe Taylor, K1JT, and the WSJT-X team Jim Tonne, W4ENE Paul Verhage, KD4STH

| Copyright © 2018 by<br>The American Radio Relay League, Inc.                                                                                                                                                                                              |

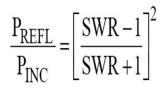

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Copyright secured under the Pan-American Convention<br>International Copyright secured                                                                                                                                                                    |

| All rights reserved. No part of this work may be reproduced in any form except by written permission of the publisher. All rights of translation are reserved.                                                                                            |

| Printed in the USA                                                                                                                                                                                                                                        |

| Quedan reservados todos los derechos                                                                                                                                                                                                                      |

| ISBN: 978-1-62595-088-8 Softcover<br>ISBN: 978-1-62595-089-5 Six-Volume Boxed Set                                                                                                                                                                         |

| Kindle eBook Editions<br>ISBN: 978-1-62595-091-8 — Volume 1<br>ISBN: 978-1-62595-092-5 — Volume 2<br>ISBN: 978-1-62595-093-2 — Volume 3<br>ISBN: 978-1-62595-094-9 — Volume 4<br>ISBN: 978-1-62595-095-6 — Volume 5<br>ISBN: 978-1-62595-096-3 — Volume 6 |

| Ninety-Sixth Edition                                                                                                                                                                                                                                      |

**Please Note**: This eBook is based on the ninety-sixth edition (2019 edition) of *The ARRL Handbook for Radio Communications*. Supplemental content, referenced throughout this volume, is available for download at <u>www.arrl.org/product-notes</u>.

## Contents

#### A more detailed Table of Contents is included at the beginning of each chapter.

**VOLUME 2**

PRACTICAL DESIGN AND PRINCIPLES — PART 1

#### **5 RF Techniques**

5.1 Introduction 5.2 Lumped-Element versus Distributed Characteristics 5.3 Effects of Parasitic (Stray) Characteristics 5.4 Semiconductor Circuits at RF 5.5 Ferrite Materials 5.6 Impedance Matching Networks 5.7 RF Transformers 5.8 Noise 5.9 Two-Port Networks 5.10 RF Design Techniques Glossary 5.11 References and Bibliography

#### **<u>6 Computer-Aided Circuit Design</u>**

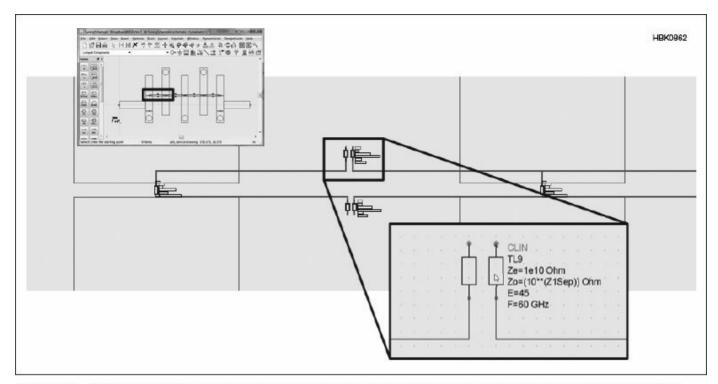

6.1 Circuit Simulation Overview

- 6.2 Simulation Basics

- 6.3 Limitations of Simulation at RF

- 6.4 Electromagnetic Analysis of RF Circuits

- 6.5 References and Bibliography

#### **7 Power Sources**

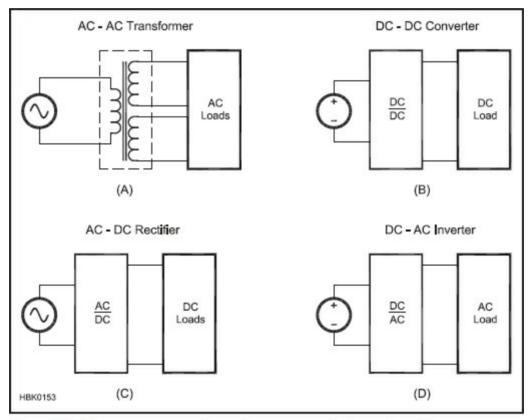

- 7.1 Power Processing

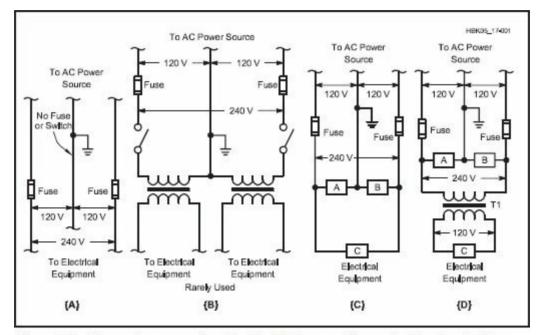

- 7.2 AC-AC Power Conversion

- 7.3 Power Transformers

- 7.4 AC-DC Power Conversion

- 7.5 Voltage Multipliers

- 7.6 Current Multipliers

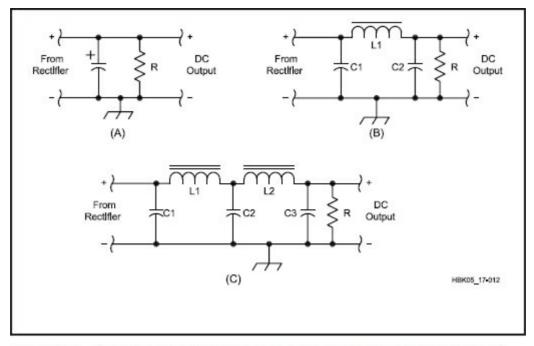

- 7.7 Rectifier Types

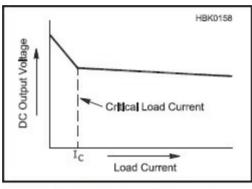

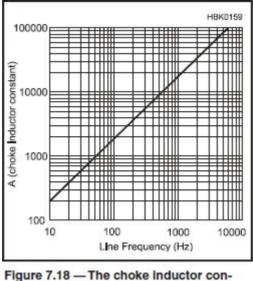

- 7.8 Power Filtering

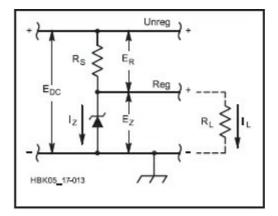

7.9 Power Supply Regulation

7.10 "Crowbar" Protective Circuits

7.11 DC-DC Switchmode Power Conversion

7.12 High-Voltage Techniques

7.13 Batteries

7.14 Glossary of Power Source Terms

7.15 References and Bibliography

7.16 Power Supply Projects

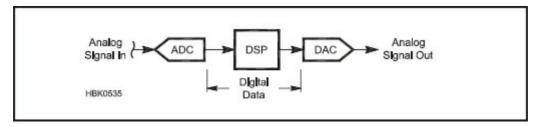

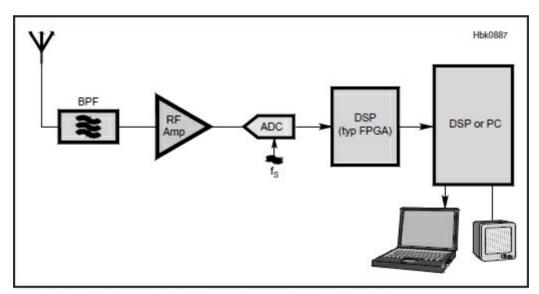

#### **8 DSP and SDR Fundamentals**

8.1 Introduction to DSP

8.2 Introduction to SDR

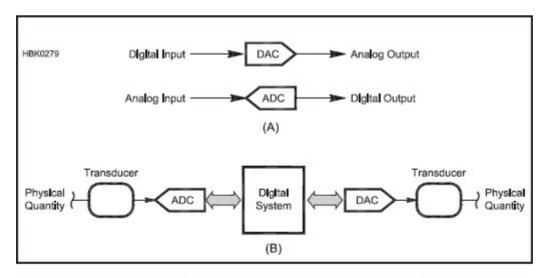

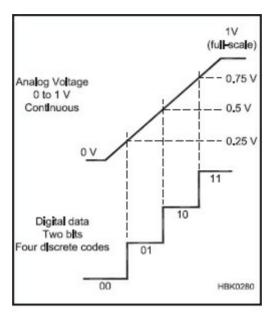

8.3 Analog-Digital Conversion

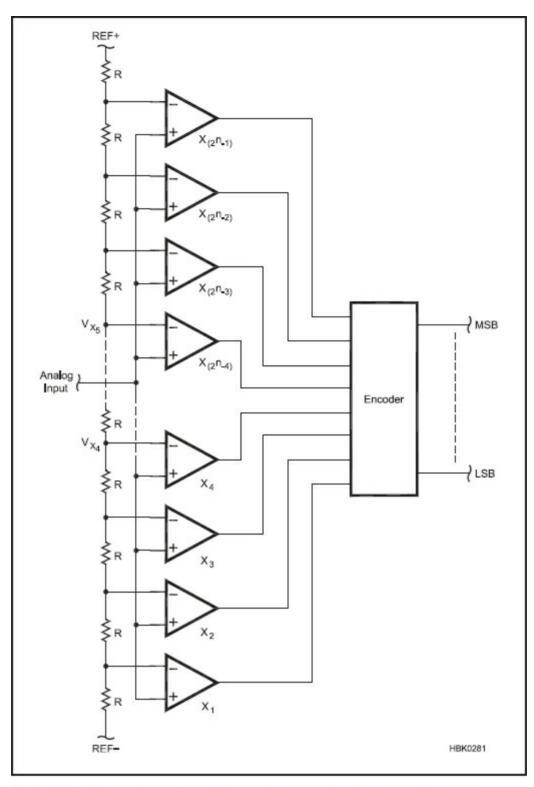

8.4 Data Converters for SDR and DSP

8.5 Digital Signal Processors

8.6 Digital (Discrete-time) Signals

8.7 The Fourier Transform

8.8 Glossary of DSP and SDR Terms

8.9 References and Bibliography

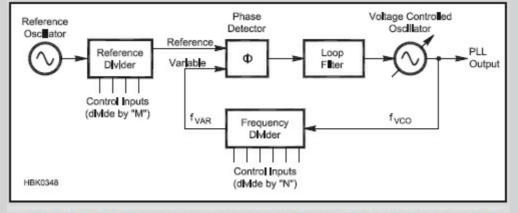

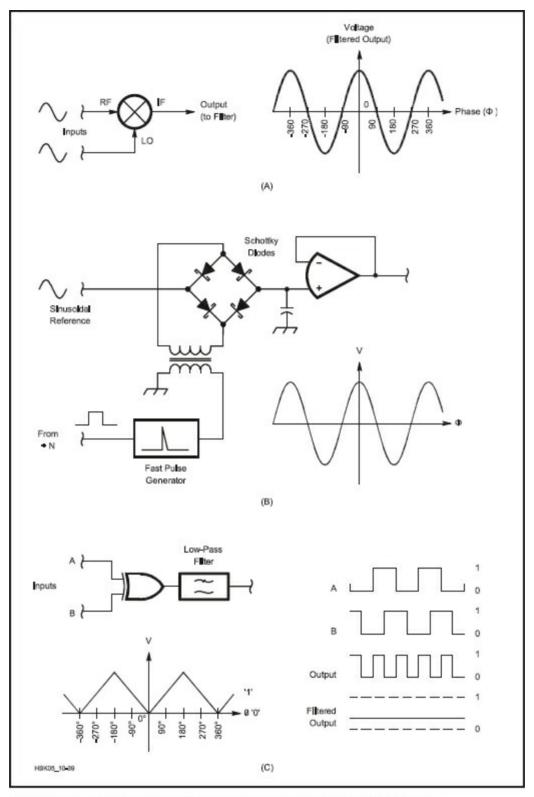

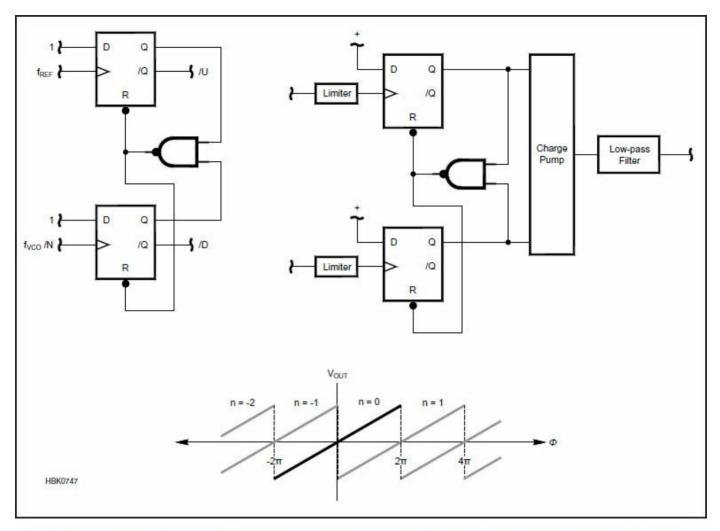

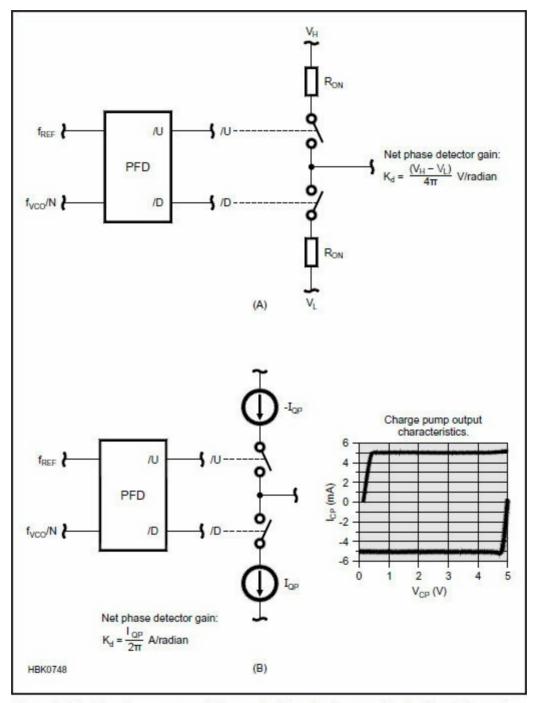

#### **9 Oscillators and Synthesizers**

9.1 How Oscillators Work

9.2 LC Variable Frequency Oscillator (VFO) Circuits

9.3 Building an Oscillator

9.4 Crystal Oscillators

9.5 Oscillators at UHF and Above

9.6 Frequency Synthesizers

9.7 Phase Noise

9.8 Glossary of Oscillator and Synthesizer Terms

9.9 References and Bibliography

#### **10 Analog and Digital Filtering**

10.1 Introduction

10.2 Filter Basics

10.3 Passive LC Filters

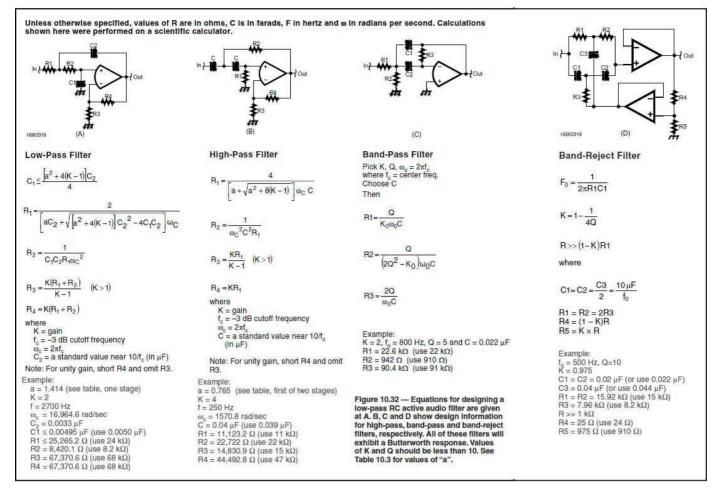

10.4 Active Audio Filters

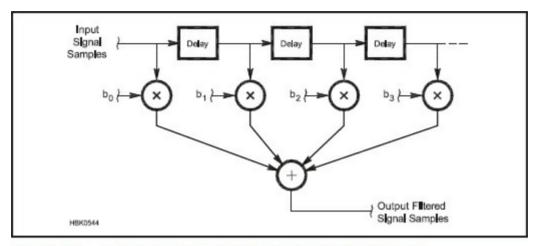

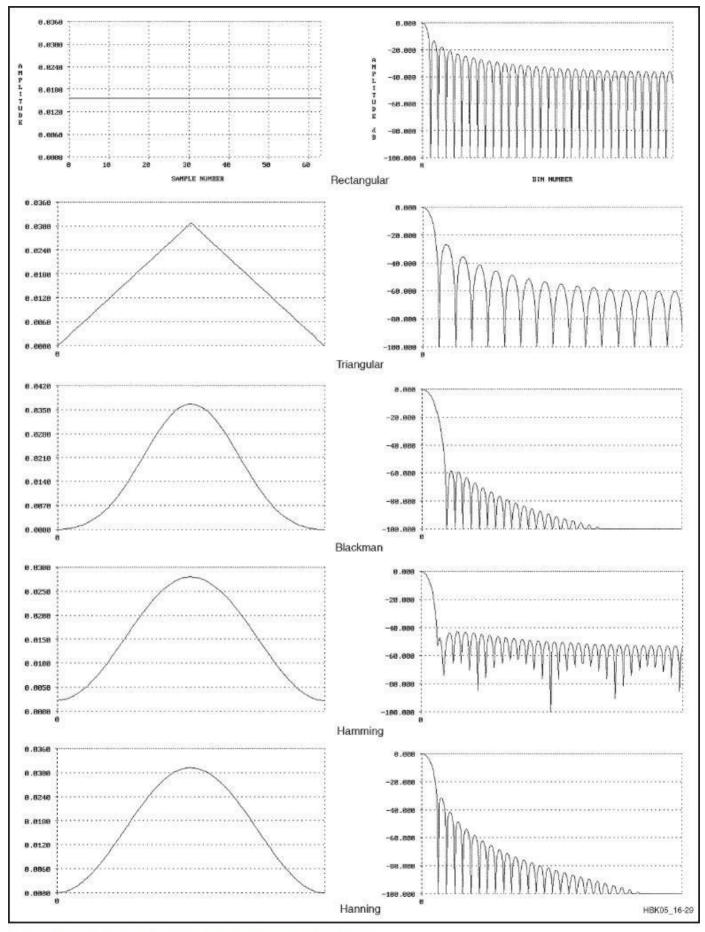

10.5 Digital Filters

10.6 Quartz Crystal Filters

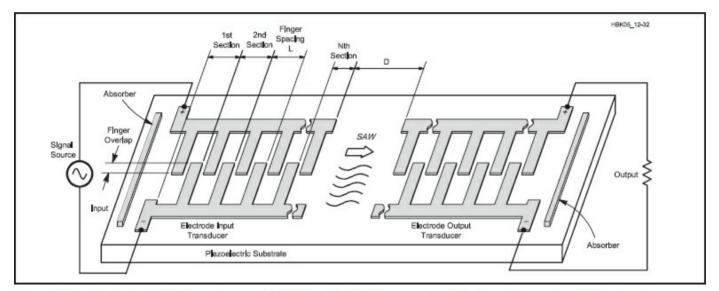

10.7 SAW Filters

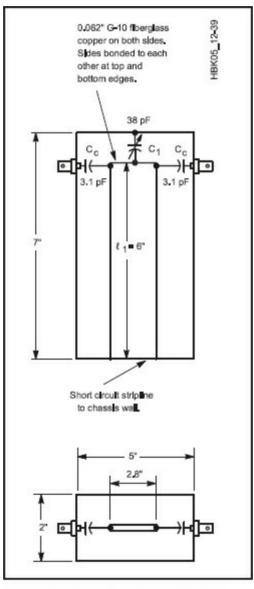

10.8 Transmission Line VHF/UHF/Microwave Filters

10.9 Helical Resonators10.10 Filter Projects10.11 Glossary of Filter Terms10.12 References and Bibliography

#### **<u>11 Modulation</u>**

11.1 Introduction

11.2 Amplitude Modulation (AM)

11.3 Angle Modulation

11.4 FSK and PSK

11.5 Quadrature Modulation

11.6 Analytic Signals and Modulation

11.7 Image Modulation

11.8 Spread Spectrum Modulation

11.9 Pulse Modulation

11.10 Modulation Bandwidth and Impairments

11.11 Glossary of Modulation Terms

11.12 References and Further Reading

#### VOLUME 1

#### INTRODUCTION AND FUNDAMENTAL THEORY

#### 1 What is Amateur (Ham) Radio?

- 1.1 Do-It-Yourself Wireless

- 1.2 Joining the Ham Radio Community

- 1.3 Your Ham Radio Station

- 1.4 Getting on the Air

- 1.5 Your Ham Radio "Lifestyle"

- 1.6 Public Service

- 1.7 Ham Radio in the Classroom

- 1.8 Resources

- 1.9 Glossary

#### **2** Electrical Fundamentals

- 2.1 Introduction to Electricity

- 2.2 Resistance and Conductance

- 2.3 Basic Circuit Principles

- 2.4 Power and Energy

- 2.5 Circuit Control Components

- 2.6 Capacitance and Capacitors

- 2.7 Inductance and Inductors

- 2.8 Semiconductor Devices

- 2.9 References and Bibliography

#### **3 Radio Fundamentals**

- 3.1 AC Waveforms

- 3.2 Measuring AC Voltage, Current and Power

- 3.3 Effective Radiated Power

- 3.4 AC in Capacitors and Inductors

- 3.5 Working with Reactance

- 3.6 Impedance

- 3.7 Quality Factor (Q) of Components

- 3.8 Resonant Circuits

- 3.9 Analog Signal Processing

- 3.10 Electromagnetic Waves

- 3.11 References and Bibliography

#### 4 Circuits and Components

4.1 Practical Resistors

- 4.2 Practical Capacitors

- 4.3 Practical Inductors

- 4.4 Transformers

- 4.5 Practical Semiconductors

- 4.6 Amplifiers

- 4.7 Operational Amplifiers

- 4.8 Miscellaneous Analog ICs

- 4.9 Analog-Digital Interfacing

- 4.10 Analog Device and Circuits Glossary

- 4.11 Heat Management

- 4.12 References and Bibliography

#### **VOLUME 3**

#### PRACTICAL DESIGN AND PRINCIPLES — PART 2

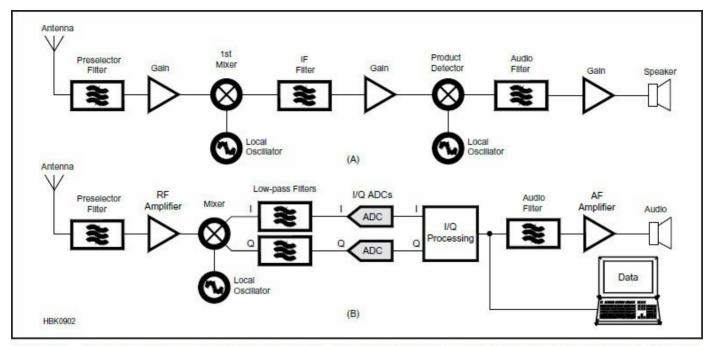

#### 12 Receiving

- 12.1 Characterizing Receivers12.2 Heterodyne Receivers

- 12.3 SDR Receivers

- 12.4 Mixing and Mixers

- 12.5 Demodulation and Detection

- 12.6 Automatic Gain Control (AGC)

- 12.7 Noise Management

- 12.8 References and Bibliography

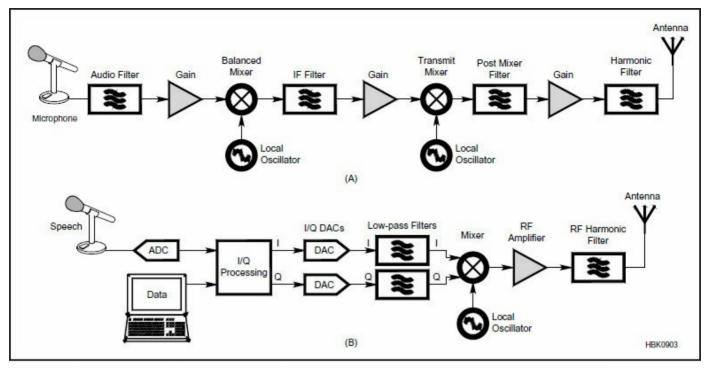

#### 13 Transmitting

- 13.1 Characterizing Transmitters

- 13.2 Transmitter Architecture

- 13.3 Modulators

- 13.4 Transmitting CW

- 13.5 Transmitting AM and SSB

- 13.6 Transmitting Angle Modulation

- 13.7 Effects of Transmitted Noise

- 13.8 Microphones and Speech Processing

- 13.9 Voice Operation

- 13.10 Transmitter Power Stages

- 13.11 References and Bibliography

#### **14 Transceiver Design Topics**

- 14.1 Signal Chains in SDR Transceivers

- 14.2 User Interfaces

- 14.3 Configuration and Control Interfaces

- 14.4 SDR Design Tools

#### **15 Digital Protocols and Modes**

- 15.1 Digital "Modes"

- 15.2 Unstructured Digital Modes

- 15.3 Fuzzy Modes

- 15.4 Structured Digital Modes

- 15.5 Networking Modes

- 15.6 Digital Mode Table

- 15.7 Glossary of Digital Protocol and Mode Terms

#### 15.8 References and Bibliography

#### 16 Amateur Radio Data Platforms

16.1 Platform Overview

16.2 Sensors

16.3 Navigation Data and Telemetry

16.4 Payloads

16.5 High Altitude Balloon Platforms

16.6 Unmanned Aerial Vehicles (UAVs)

16.7 Rockets

16.8 Robotics

16.9 Fixed Stations

16.10 References and Bibliography

#### **17 RF Power Amplifiers**

- 17.1 High Power, Who Needs It?

- 17.2 Types of Power Amplifiers

- 17.3 Vacuum Tube Basics

- 17.4 Tank Circuits

- 17.5 Transmitting Tube Ratings

- 17.6 Sources of Operating Voltages

- 17.7 Tube Amplifier Cooling

- 17.8 Vacuum Tube Amplifier Stabilization

- 17.9 MOSFET Design for RF Amplifiers

- 17.10 Solid-State RF Amplifiers

- 17.11 Solid State Amplifier Projects

- 17.12 Tube Amplifier Projects

- 17.13 References and Bibliography

#### **18 Repeaters**

- 18.1 A Brief History

- 18.2 Repeater Overview

- 18.3 FM Voice Repeaters

- 18.4 D-STAR Repeater Systems

- 18.5 System Fusion Repeater Systems

- 18.6 Digital Mobile Radio (DMR)

- 18.7 Other Digital Voice Repeater Technologies

- 18.8 Glossary of FM and Repeater Terms

- 18.9 References and Bibliography

#### **VOLUME 4**

#### ANTENNA SYSTEMS AND RADIO PROPAGATION

#### **19** Propagation of Radio Signals

- 19.1 Fundamentals of Radio Waves

- 19.2 Sky-Wave Propagation and the Sun

- **19.3 MUF Predictions**

- 19.4 Propagation in the Troposphere

- 19.5 VHF/UHF Mobile Propagation

- 19.6 Propagation for Space Communications

- 19.7 Noise and Propagation

- 19.8 Propagation Below the AM Broadcast Band

- 19.9 Glossary of Radio Propagation Terms

- 19.10 References and Bibliography

#### **20 Transmission Lines**

- 20.1 Transmission Line Basics

- 20.2 Choosing a Transmission Line

- 20.3 The Transmission Line as Impedance Transformer

- 20.4 Matching Impedances in the Antenna System

- 20.5 Baluns and Transmission-Line Transformers

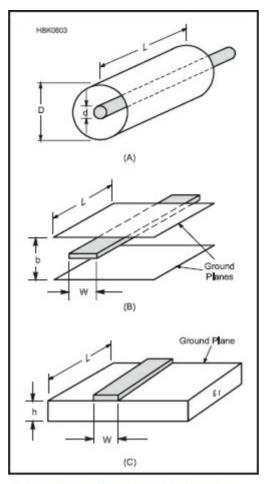

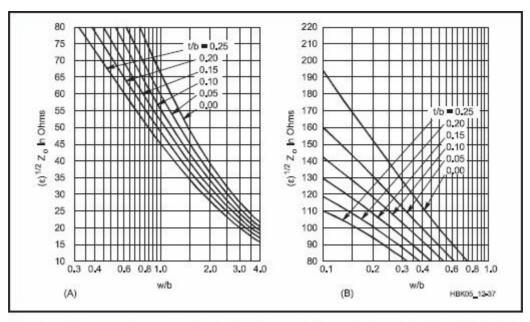

- 20.6 PC Transmission Lines

- 20.7 Waveguides

- 20.8 Glossary of Transmission Line Terms

- 20.9 References and Bibliography

#### 21 Antennas

- 21.1 Antenna Basics

- 21.2 Dipoles and the Half-Wave Antenna

- 21.3 Vertical (Ground-Plane) Antennas

- 21.4 T and Inverted-L Antennas

- 21.5 Slopers and Vertical Dipoles

- 21.6 Yagi Antennas

- 21.7 Quad and Loop Antennas

- 21.8 HF Mobile Antennas

- 21.9 VHF/UHF Mobile Antennas

- 21.10 VHF/UHF Antennas

- 21.11 VHF/UHF Beams

- 21.12 Radio Direction Finding Antennas

- 21.13 Glossary of Antenna Terms

21.14 References and Bibliography

#### **VOLUME 5** EQUIPMENT CONSTRUCTION AND STATION ACCESSORIES

#### 22 Component Data and References

- 22.1 Component Data

- 22.2 Resistors

- 22.3 Capacitors

- 22.4 Inductors

- 22.5 Transformers

- 22.6 Semiconductors

- 22.7 Tubes, Wire, Materials, Attenuators, Miscellaneous

- 22.8 Computer Connectors

- 22.9 RF Connectors and Transmission Lines

- 22.10 Reference Tables

#### **23** Construction Techniques

- 23.1 Electronic Shop Safety

- 23.2 Tools and Their Use

- 23.3 Soldering Tools and Techniques

- 23.4 Surface Mount Technology (SMT)

- 23.5 Constructing Electronic Circuits

- 23.6 CAD for PCB Design

- 23.7 Microwave Construction

- 23.8 Mechanical Fabrication

#### 24 Assembling a Station

- 24.1 Fixed Stations

- 24.2 Mobile Installations

- 24.3 Portable Installations

- 24.4 Remote Stations

#### **VOLUME 6**

#### TEST EQUIPMENT, TROUBLESHOOTING, RFI, AND INDEX

#### **25 Test Equipment and Measurements**

- 25.1 Introduction

- 25.2 DC Measurements

- 25.3 AC Measurements

- 25.4 RF Measurements

- 25.5 Receiver Measurements

- 25.6 Transmitter Measurements

- 25.7 Antenna System Measurements

- 25.8 Miscellaneous Measurements

- 25.9 Construction Projects

- 25.10 References and Further Reading

- 25.11 Glossary of Test Equipment and Measurement Terms

#### 26 Troubleshooting and Maintenance

- 26.1 Test Equipment

- 26.2 Components

- 26.3 Getting Started

- 26.4 Inside the Equipment

- 26.5 Testing at the Circuit Level

- 26.6 After the Repairs

- 26.7 Professional Repairs

- 26.8 Typical Symptoms and Faults

- 26.9 Radio Troubleshooting Hints

- 26.10 Antenna Systems

- 26.11 Repair and Restoration of Vintage Equipment

- 26.12 References and Bibliography

#### **27 RF Interference**

- 27.1 Managing Radio Frequency Interference

- 27.2 FCC Rules and Regulations

- 27.3 Elements of RFI

- 27.4 Identifying the Type of RFI Source

- 27.5 Locating Sources of RFI

- 27.6 Power-Line Noise

- 27.7 Elements of RFI Control

- 27.8 Troubleshooting RFI

- 27.9 Automotive RFI

27.10 RFI Projects27.11 Glossary of RFI Terms27.12 References and Bibliography

#### 28 Safety

28.1 Electrical Safety28.2 Antenna and Tower Safety28.3 RF Safety

Advertiser's Index Index Project Index Author's Index

DOWNLOADABLE CONTENT AND TOOLS\* Space Communications Digital Communications Image Communications Digital Basics Station Accessories and Projects 2019 HF Transceiver Survey Radio Mathematics

\*Included with complete print edition only (sold separately).

## Contents

- 5.1. Introduction

- 5.2. Lumped-Element versus Distributed Characteristics

- 5.3. Effects of Parasitic (Stray) Characteristics

- 5.3.1 Parasitic Inductance

- 5.3.2 Parasitic Capacitance

- 5.3.3 Inductors at Radio Frequencies

- 5.3.4 Skin Effect

- 5.3.5 RF Heating

- 5.3.6 Effect on Q

- 5.3.7 Self-Resonance

- 5.3.8 Dielectric Breakdown and Arcing

- 5.3.9 Radiative Losses

- 5.3.10 Bypassing and Decoupling

- 5.3.11 Effects on Filter Performance

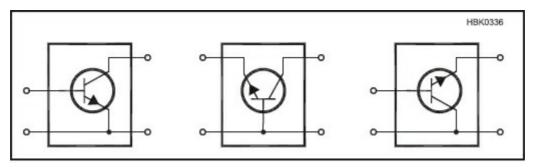

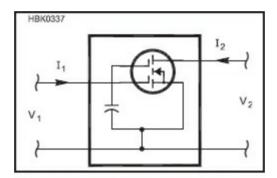

- 5.4. Semiconductor Circuits at RF

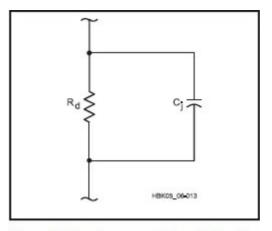

- 5.4.1 The Diode at High Frequencies

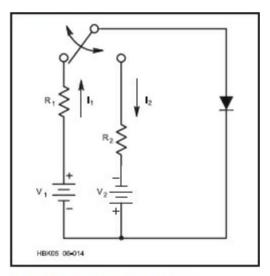

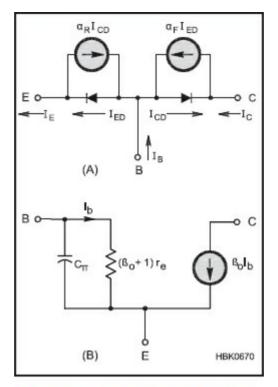

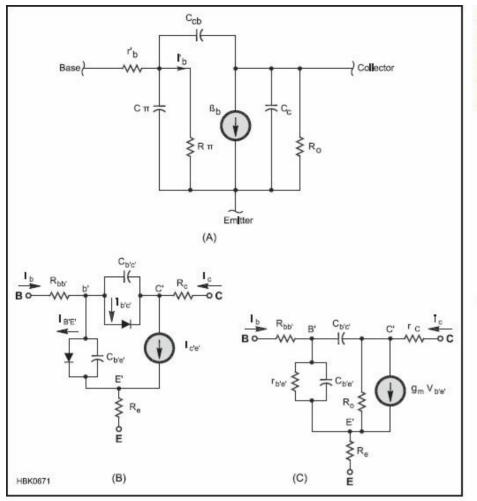

- 5.4.2 The Transistor at High Frequencies

- 5.4.3 Amplifier Classes

- 5.4.4 RF Amplifiers with Feedback

- 5.5. Ferrite Materials

- 5.5.1 Ferrite Permeability and Frequency

- 5.5.2 Resonances of Ferrite Cores

- 5.5.3 Ferrite Series and Parallel Equivalent Circuits

- 5.5.4 Type 31 Material

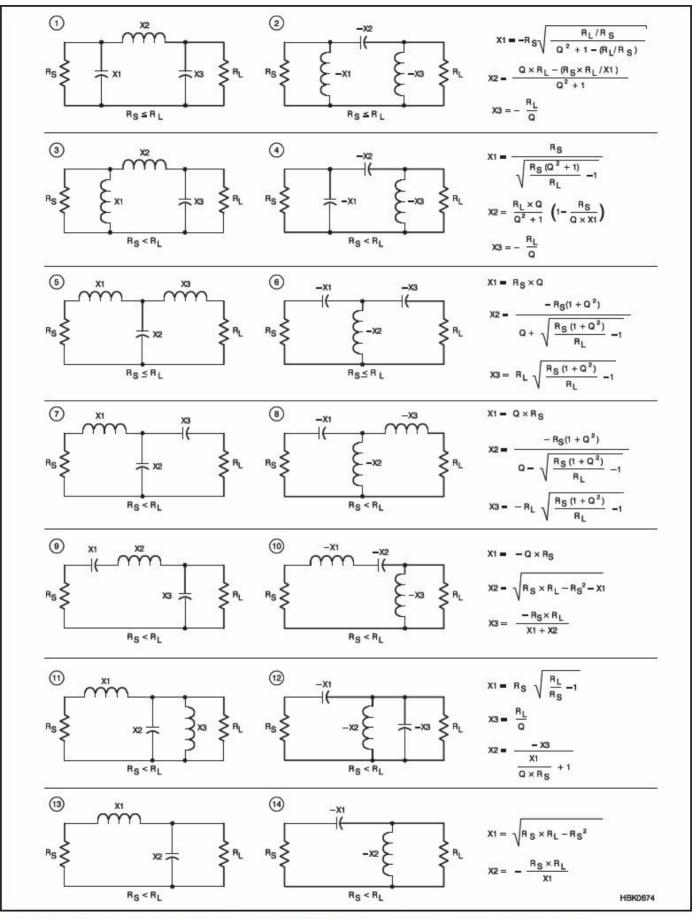

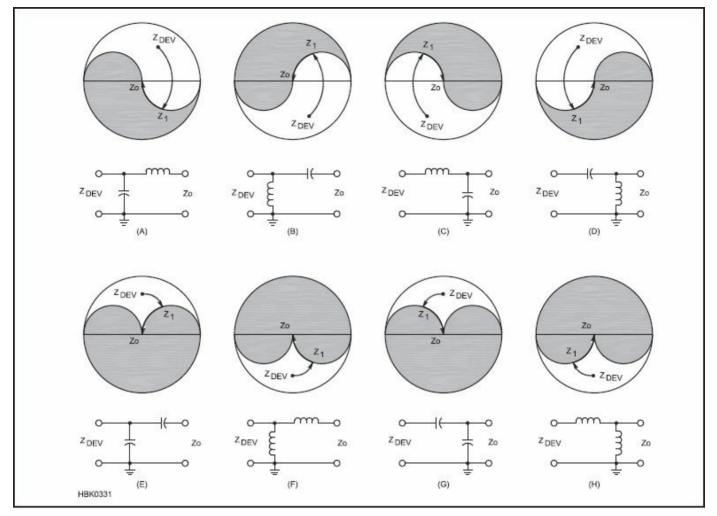

- 5.6. Impedance Matching Networks

- 5.6.1 L Networks

- 5.6.2 Pi Networks

- 5.6.3 T Networks

- 5.6.4 Impedance Inversion

- 5.7. RF Transformers

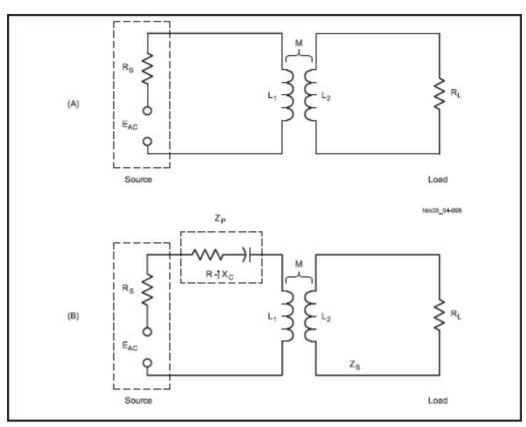

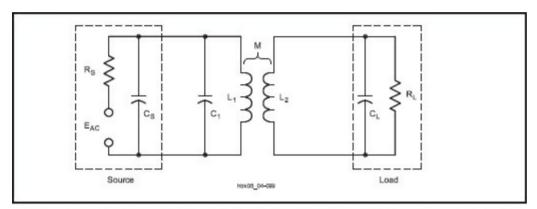

- 5.7.1 Air-Core Nonresonant RF Transformers

- 5.7.2 Air-Core Resonant RF Transformers

- 5.7.3 Broadband Ferrite RF Transformers

- 5.8. Noise

- 5.8.1 Noise Power

- 5.8.2 Signal to Noise Ratio

5.8.3 Noise Temperature

5.8.4 Noise Factor and Noise Figure

5.8.5 Losses

5.8.6 Cascaded Amplifiers

5.8.7 Antenna Temperature

5.8.8 Image Response

5.8.9 Background Noise

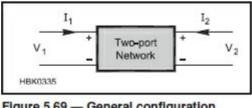

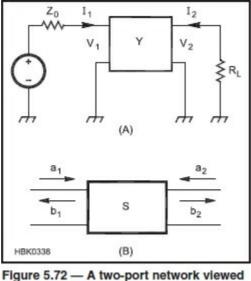

5.9. Two-Port Networks

5.9.1 Two-port Parameters

5.9.2 Return Loss

5.10. RF Techniques Glossary

5.11. References and Bibliography

## **RF** Techniques

This chapter is a compendium of material from ARRL publications and other sources. It assumes the reader is familiar with the concepts introduced in the **Electrical Fundamentals**, **Radio Fundamentals**, and **Circuits and Components** chapters. The topics and techniques discussed here are associated with the special demands of circuit design in the HF and VHF ranges. The material is collected from previous editions of this book written by Leonard Kay, K1NU; *Introduction to Radio Frequency Design* by Wes Hayward, W7ZOI; and *Experimental Methods in RF Design* by Wes Hayward, W7ZOI, Rick Campbell, KK7B, and Bob Larkin, W7PUA. Material on ferrites is drawn from publications by Jim Brown, K9YC. The section on Noise was written by Paul Wade, W1GHZ, with contributions from Joe Taylor, K1JT.

#### Chapter 5 — Downloadable Supplemental Content

Supplemental Articles

• "Reflections on the Smith Chart" by Wes Hayward, W7ZOI

Tuned Networks

• "Simplified Design of Impedance-Matching Networks," Parts I through III by George Grammer, W1DF

• *LTSpice* simulation files for Section 5.3, Effects of Parasitic Characteristics

• "The Galactic Background in the Upper HF Band" by Dave Typinski, AJ4CO

## **5.1 Introduction**

When is an inductor not an inductor? When it's a capacitor! This statement may seem odd, but it suggests the main message of this chapter. In the earlier chapter, **Electrical Fundamentals**, the basic components of electronic circuits were introduced. As you may know from experience, those simple component pictures are ideal. That is, an ideal component (or element) by definition behaves exactly like the mathematical equations that describe it, and only in that fashion. For example, the current through an ideal capacitor is equal to the capacitance times the rate of change of the voltage across it without consideration of the materials or techniques by which a real capacitor is manufactured.

It is often said that, "Parasitics are anything you don't want," meaning that the component is exhibiting some behavior that detracts from or compromises its intended use. Real components only approximate ideal components, although sometimes quite closely. Any deviation from ideal behavior a component exhibits is called *non-ideal, parasitic*, or *stray*. One way of thinking about parasitic and stray effects — although this is by no means universal — is that parasitic effects are intrinsic to the component and stray effects include both parasitics and environmental effects such as coupling to nearby materials. Since most of what we'll discuss in the following sections deals with the characteristics of actual components, we'll use the term parasitic. Remember that stray and parasitic are often treated as interchangeable terms.

The important thing to realize is that *every* component has parasitic aspects that become significant when it is used in certain ways. This chapter deals with parasitic effects that are commonly encountered at radio frequencies.Knowing to what extent and under what conditions real components cease to behave like their ideal counterparts, and what can be done to account for these behaviors, allows the circuit designer or technician to work with circuits at radio frequencies. We will explore how and why the real components behave differently from ideal components, how we can account for those differences when analyzing

circuits and how to select components to minimize, or exploit, non-ideal behaviors.

## **5.2 Lumped-Element versus Distributed Characteristics**

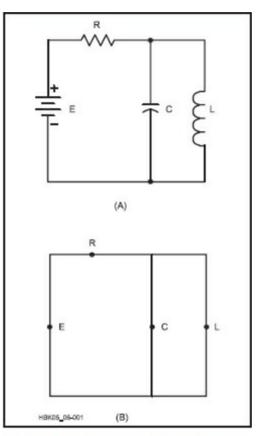

Most electronic circuits that we use every day are inherently and mathematically considered to be composed of *lumped elements*. That is, we assume each component acts at a single point in space, and the wires that connect these lumped elements are assumed to be perfect conductors (with zero resistance and insignificant length). This concept is illustrated in **Figure 5.1**. These assumptions are perfectly reasonable for many applications, but they have limits. Lumped element models break down when:

Figure 5.1 — The lumped element concept. Ideally, the circuit at A is assumed to be as shown at B, where the components are isolated points connected by perfect conductors. Many components exhibit nonideal behavior when these assumptions no longer hold.

- Circuit impedance is so low that the small, but non-zero, resistance in the wires is important. (A significant portion of the circuit power may be lost to heat in the conductors.)

- Lead and interconnection inductance is high enough (or the frequency is high enough) that the additional reactance affects circuit behavior.

- Operating frequency is high enough that the length of the connecting wires is a significant fraction (>0.1) of the wavelength causing the propagation delay along the conductor or radiation from it to affect the circuit in which it is used.

- Transmission lines are used as conductors. (Their characteristic impedance is usually significant, and impedances connected to them are transformed as a function of the line length. See the **Transmission** Lines chapter for more information.)

Effects such as these are called *distributed*, and we talk of *distributed elements* or effects to contrast them

to lumped elements.

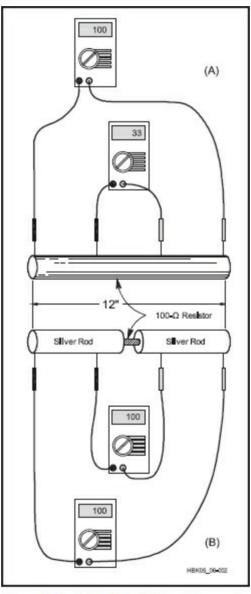

To illustrate the differences between lumped and distributed elements, consider the two resistors in **Figure 5.2**, which are both 12 inches long. The resistor at A is a uniform rod of carbon. The second "resistor" B is made of two 6-inch pieces of silver rod (or other highly conductive material), with a small resistor soldered between them. Now imagine connecting the two probes of an ohmmeter to each of the two resistors, as in the figure. Starting with the probes at the far ends, as we slide the probes toward the center, the carbon rod will display a constantly decreasing resistance on the ohmmeter. This represents a distributed resistance. On the other hand, the ohmmeter connected to the other 12-inch "resistor" will display a constant resistance as long as one probe remains on each side of the small resistance and as long as we neglect the resistance of the silver rods! This represents a lumped resistance connected by perfect conductors.

Figure 5.2 — Distributed (A) and lumped (B) resistances. See text for discussion.

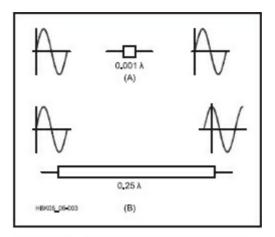

Lumped elements also have the very desirable property that they introduce no phase shift resulting from propagation delay through the element. (Although combinations of lumped elements can produce phase shifts by virtue of their R, L and C properties.) Consider a lumped element that is carrying a sinusoidal current, as in **Figure 5.3A**. Since the element has negligible length, there is no phase difference in the

current between the two sides of the element — *no matter how high the frequency* — precisely *because* the element length is negligible. If the physical length of the element were long, say 0.25 wavelength (0.25  $\lambda$ ) as shown in Figure 5.3B, the current phase would *not* be the same from end to end. In this instance, the current is delayed by 90 electrical degrees as it moves along the element. The amount of phase difference depends on the circuit's electrical length.

Figure 5.3 — The effects of distributed resistance on the phase of a sinusoidal current. There is no phase delay between ends of a lumped element.

Because the relationship between the physical size of a circuit and the wavelength of an ac current present in the circuit will vary as the frequency of the ac signal varies, the ideas of lumped and distributed effects actually occupy two ends of a spectrum. At HF (30 MHz and below), where  $\lambda \ge 10$  m, the lumped element concept is almost always valid. In the UHF and microwave region (300 MHz and above), where  $\lambda \le 1$  m and physical component size can represent a significant fraction of a wavelength, nearly all components and wiring exhibits distributed effects to one degree or another. From roughly 30 to 300 MHz, whether the distributed effects are significant must be considered on a case-by-case basis.

Of course, if we could make resistors, capacitors, inductors and so on, very small, we could treat them as lumped elements at much higher frequencies. For example, surface-mount components, which are manufactured in very small, leadless packages, can be used at much higher frequencies than leaded components and with fewer non-ideal effects.

It is for these reasons that circuits and equipment are often specified to work within specific frequency ranges. Outside of these ranges the designer's assumptions about the physical characteristics of the components and the methods and materials of the circuit's assembly become increasingly invalid. At frequencies sufficiently removed from the design range, circuit behavior often changes in unpredictable ways.

### 5.3 Effects of Parasitic (Stray) Characteristics

Parasitic effects can be important at almost any frequency where performance is held to tight specifications. Stray reactances can have a big effect even at audio frequencies, for example. Lightning protection is very sensitive to grounding conductor inductance. Power connections to high-current solid-state amplifiers must have very low resistance, and so on. At HF and above (where we do much of our circuit design) these considerations become very important, in some cases dominant, in the models we use to describe our components. To understand what happens to circuits at RF we turn to a brief discussion of some electromagnetic and microwave theory concepts.

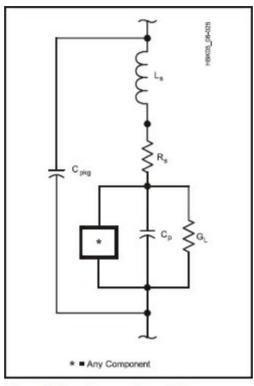

Parasitic effects due to component leads, packaging, leakage and so on are relatively common to all

components. When working at frequencies where many or all of the parasitics become important, a complex but completely general model such as that in **Figure 5.4** can be used for just about any component, with the actual component placed in the box marked \*. Parasitic capacitance,  $C_p$ , and leakage conductance,  $G_L$ , appear in parallel across the device, while series resistance,  $R_s$ , and parasitic inductance,  $L_s$ , appear in series with it. Package capacitance,  $C_{pkg}$ , appears as an additional capacitance in parallel across the whole device.

Figure 5.4 — A general model for electrical components at VHF frequencies and above. The box marked \* represents the component. See text for discussion.

These small parasitics can significantly affect frequency responses of RF circuits. Either take steps to minimize or eliminate them, or use simple circuit theory to predict and anticipate changes. This maze of effects may seem overwhelming, but remember that it is very seldom necessary to consider all parasitics at all frequencies and for all applications. The **Computer-Aided Circuit Design** chapter shows how to incorporate the effect of multiple parasitics into circuit design and performance modeling. Files for the *LTSpice* simulation package that include parasitic characteristics for a resistor, capacitor and inductor are provided in the downloadable supplemental information for this *Handbook*.

#### **5.3.1 Parasitic Inductance**

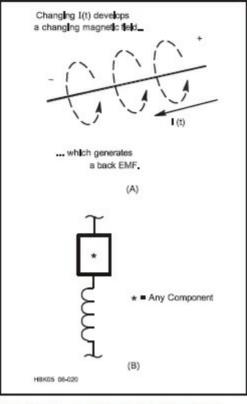

Maxwell's equations — the basic laws of electromagnetism that govern the propagation of electromagnetic waves and the operation of all electronic components — tell us that any wire carrying a current that changes with time (one example is a sine wave) develops a changing magnetic field around it. This changing magnetic field in turn induces an opposing voltage, or *back EMF*, on the wire. The back EMF is proportional to how fast the current changes (see Figure 5.5).

Figure 5.5 — Inductive consequences of Maxwell's equations. At A, any wire carrying a changing current develops a voltage difference along it. This can be mathematically described as an effective inductance. B adds parasitic inductance to a generic component model.

We exploit this phenomenon when we make an inductor. The reason we typically form inductors in the shape of a coil is to concentrate the magnetic field and thereby maximize the inductance for a given physical size. However, *all* wires carrying varying currents have these inductive properties. This includes the wires we use to connect our circuits, and even the *leads* of capacitors, resistors and so on. The inductance of a straight, round, nonmagnetic wire in free space is given by:

$$L = 0.00508 b \left[ \ln \left( \frac{2b}{a} \right) - 0.75 \right]$$

<sup>(1)</sup>

where

$L = inductance, in \mu H$

a = wire radius, in inches

b = wire length, in inches

$\ln = natural logarithm (2.303 \times log_{10})$

Skin effect (discussed below) changes this formula slightly at VHF and above. As the frequency approaches infinity, the value 0.75 in the above equation increases to approach 1. This effect usually causes a change of no more than a few percent.

As an example, let's find the inductance of a typical #18 wire (diameter = 0.0403 inch and a = 0.0201) that is 4 inches long (b = 4):

L = 0.00508 (4)

$$\left[ \ln \left( \frac{8}{0.0201} \right) - 0.75 \right]$$

= 0.0203 [5.98 - 0.75] = 0.106 µH

Wire of this diameter has an inductance of about 25 nH per inch of length. In circuits operating at VHF and higher frequencies, including high-speed digital circuits, the inductance of component leads can become significant. (The #24 AWG wire typically used for component leads has an inductance on the order of 20 nH per inch.) At these frequencies, lead inductance can affect circuit behavior, making the circuit hard to reproduce or repair. Good design and construction practice is to minimize the effects of lead inductance by using surface-mount components or trimming the leads to be as short as possible.

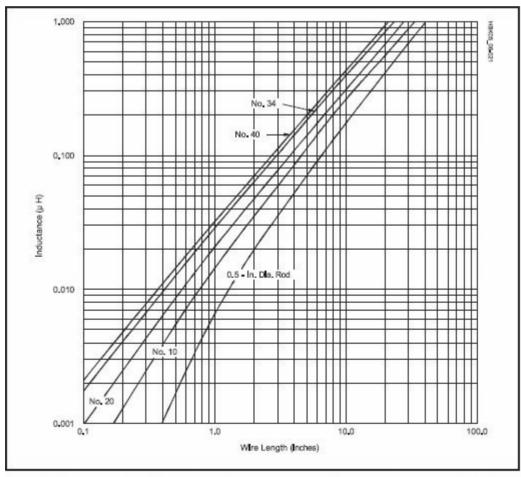

The impact of reactance due to parasitic inductance is usually very small; at AF or LF, parasitic inductive reactance of most components is practically zero. To use this example, the reactance of a 0.106  $\mu$ H inductor even at 10 MHz is only 6.6  $\Omega$ . Figure 5.6 shows a graph of the inductance for wires of various gauges (radii) as a function of length. Whether the reactance is significant or not depends on the application and the frequency of use.

Figure 5.6 — A plot of inductance vs length for straight conductors in several wire sizes.

We can represent parasitic inductance in component models by adding an inductor of appropriate value in series with the component since the wire leads are in series with the element. This (among other reasons) is why minimizing lead lengths and interconnecting wires becomes very important when designing circuits

for VHF and above.

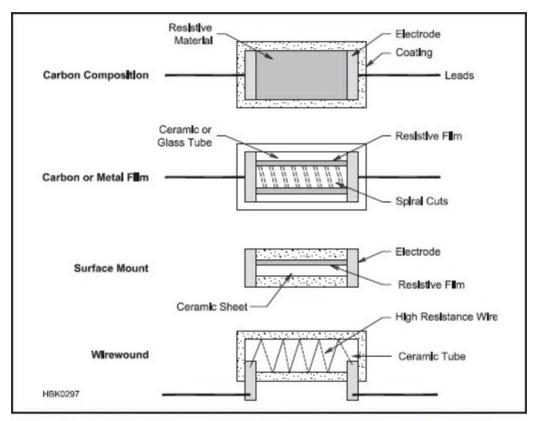

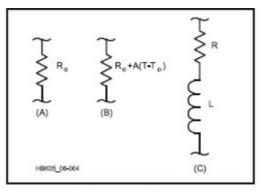

#### PARASITIC INDUCTANCE IN RESISTORS

The basic construction of common resistor types is shown in **Figure 5.7**. The primary parasitic effect associated with resistors is parasitic inductance. (Some parasitic capacitance exists between the leads or electrodes due to packaging.) **Figure 5.8** shows some more accurate circuit models for resistors at low to medium frequencies. The type of resistor with the most parasitic inductance are wire-wound resistors, essentially inductors used as resistors. Their use is therefore limited to dc or low-frequency ac applications where their reactance is negligible. Remember that this inductance will also affect switching transient waveforms, because the component will act as an RL circuit. The inductive effects of wire-wound resistors begin to become significant in the audio range above a few kHz.

Figure 5.7 — The electrical characteristics of different resistor types are strongly affected by their construction. Reactance from parasitic inductance and capacitance strongly impacts the resistor's behavior at RF.

Figure 5.8 — Circuit models for resistors. The wire-wound model with associated inductance is shown at C. B includes the effect of temperature (T). For designs at VHF and higher frequencies, the model at C could be used with L representing lead inductance.

As an example, consider a  $1-\Omega$  wire-wound resistor formed from 300 turns of #24 wire closely-wound in a single layer 6.3 inches long on a 0.5-inch diameter form. What is its approximate inductance? From the inductance formula for air-wound coils in the **Electrical Fundamentals** chapter:

$$L = \frac{d^2n^2}{18d + 401} = \frac{0.5^2 \times 300^2}{(18 \times 0.5) + (40 \times 6.3)} = 86 \,\mu\text{H}$$

If we want the inductive reactance to be less than 10% of the resistor value, then this resistor cannot be used above  $f = 0.1 / (2\pi \times 86 \mu H) = 185 \text{ Hz}!$  Real wire-wound resistors have multiple windings layered over each other to minimize both size and parasitic inductance (by winding each layer in opposite directions, much of the inductance is canceled). If we assume a five-layer winding, the length is reduced to 1.8 inches and the inductance to approximately 17  $\mu$ H, so the resistor can then be used below 937 Hz. (This has the effect of increasing the resistor's parasitic capacitance, however.)

The resistance of certain types of tubular film resistors is controlled by inscribing a spiral path through the film on the inside of the tube. This creates a small inductance that may be significant at and above the higher audio frequencies.

#### NON-INDUCTIVE RESISTORS

The resistors with the least amount of parasitic inductance are the bulk resistors, such as carboncomposition, metal-oxide, and ceramic resistors. These resistors are made from a single linear cylinder, tube or block of resistive material so that inductance is minimized. Each type of resistor has a maximum usable frequency, above which parasitic capacitance and inductance begin to become significant. Review the manufacturer's data sheet for the component to learn about its performance at high frequencies.

Some resistors advertised as "noninductive" are actually wire-wound resistors with a special winding technique that minimizes inductance. These resistors are intended for use at audio frequencies and are not suitable for use at RF. If you are not sure, ask the vendor if the resistors are suitable for use in RF circuits.

Because resistors are manufactured with an insulating coating, it can be difficult to determine their internal structure and thus estimate their parasitic inductance. In cases where a surplus or used component is to be included, it is recommended that you test the component with an impedance meter or make some other type of reactance measurement if you are unable to access the manufacturer's specifications for the resistor.

The size and shape of a capacitor's plates and the leads used to connect them to circuits create parasitic inductance, often referred to as *equivalent series inductance* (ESL) by capacitor manufacturers. **Figs 5.9** and **5.10** show reasonable models for capacitors that are good up to VHF.

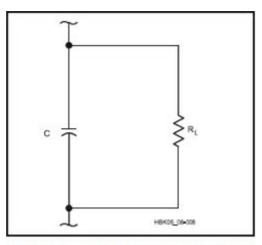

Figure 5.9 — A simple capacitor model for frequencies well below self-resonance.

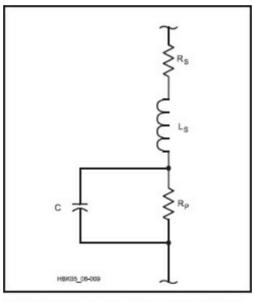

Figure 5.10 — A capacitor model for VHF and above including series resistance and distributed inductance.

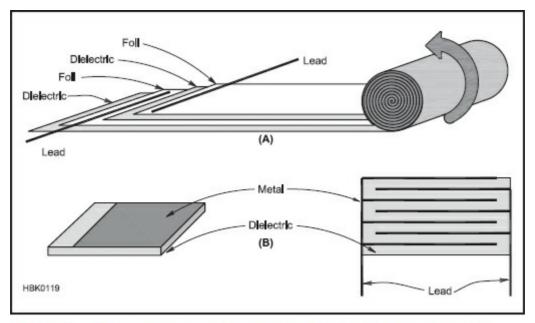

**Figure 5.11** shows a roll-type capacitor made of two strips of very thin metal foil and separated by a dielectric. After leads are attached to the foil strips, the sandwich is rolled up and either placed in a metal can or coated with plastic. *Radial leads* both stick out of one end of the roll and *axial leads* from both ends along the roll's axis. Because of the rolled strips, the ESL is high. Electrolytic and many types of film capacitors are made with roll construction. As a result, they are generally not useful in RF circuits.

Figure 5.11 — Two common types of capacitor construction. (A) Roll construction uses two strips of foil separated by a strip of dielectric. (B) Stack construction layers dielectric material (such as ceramic or film), one side coated with metal. Leads are attached and the assembly coated with epoxy resin.

In the stack capacitor, thin sheets of dielectric are coated on one side with a thin metal layer. A stack of the sheets is placed under pressure and heated to make a single solid unit. Metal side caps with leads attached contact the metal layers. The ESL of stack capacitors is very low and so they are useful at high frequencies. Ceramic and mica capacitors are the most common stack-style capacitor.

Parallel-plate air and vacuum capacitors used at RF have relatively low parasitic inductance, but transmitting capacitors made to withstand high voltages and current are large enough that parasitic inductance becomes significant, limiting their use to low-VHF and lower frequencies. Adjustable capacitors (air variables and compression or piston trimmer capacitors) for tuning low-power circuits are much smaller and so have correspondingly lower parasitic inductance.

It is difficult for a single capacitor to work well over a very wide frequency range, so capacitors are often placed in parallel as discussed in the section below on Bypassing and Decoupling. It is often suggested that different types of capacitors be connected in parallel to avoid the effects of parasitic inductance at different frequencies, but without testing and careful modeling the results are often unpredictable or even counterproductive as the referenced discussion shows.

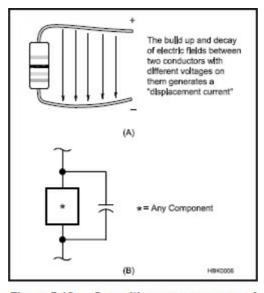

#### 5.3.2 Parasitic Capacitance

Maxwell's equations also tell us that if the voltage between any two points changes with time, a displacement current is generated between these points as illustrated in **Figure 5.12.** This *displacement current* results from the propagation of the electromagnetic field between the two points and is not to be confused with *conduction current*, which is the movement of electrons. Displacement current is directly proportional to the rate at which the voltage is changing.

Figure 5.12 — Capacitive consequences of Maxwell's equations. A: Any changing voltage between two points, for example along a bent wire, generates a displacement current running between them. This can be treated mathematically as a capacitance. B adds parasitic capacitance to a generic component model.

When a capacitor is connected to an ac voltage source, a steady ac current can flow because taken together, conduction current and displacement current "complete the loop" from the positive source terminal, across the plates of the capacitor, and back to the negative terminal.

In general, parasitic capacitance shows up *wherever* the voltage between two points is changing with time, because the laws of electromagnetics require a displacement current to flow. Since this phenomenon represents an *additional* current path from one point in space to another, we can add this parasitic capacitance to our component models by adding a capacitor of appropriate value in *parallel* with the component. These parasitic capacitances are typically less than 1 pF, so that below VHF they can be treated as open circuits (infinite reactances) and thus neglected.

#### PACKAGE CAPACITANCE

Another source of capacitance, also in the 1-pF range and therefore important only at VHF and above, is the packaging of the component itself. For example, a power transistor packaged in a TO-220 case (see **Figure 5.13**), often has either the emitter or collector connected to the metal tab itself. This introduces an extra *inter-electrode capacitance* across the junctions.

Figure 5.13 — Unexpected stray capacitance. The mounting tab of TO-220 transistors is often connected to one of the device leads. Because one lead is connected to the chassis, small capacitances from the other lead to the chassis appear as additional package capacitance at the device. Similar capacitance can appear at any device with a conductive package.

The copper traces on a PC board also create capacitance with the circuit components, to other traces, and to power and ground planes. Double-sided PC boards have a certain capacitance per square inch between the layers of copper on each side of the board. (Multi-layer PC boards have higher values of capacitance due to the smaller separation between layers.) It is possible to create capacitors by leaving unetched areas of copper on both sides of the board. The dielectric constant of inexpensive PC board materials intended for use at low-frequencies is not well-controlled, however, leading to significant variations in capacitance. For this reason, the copper on one side of a double-sided board should be completely removed under frequency-determining circuits such as VFOs.

*Stray* capacitance (a general term used for any "extra" capacitance that exists due to physical construction) appears in any circuit where two metal surfaces exist at different voltages. Such effects can be modeled as an extra capacitor in parallel with the given points in the circuit. A rough value can be obtained with the parallel-plate formula given in the chapter on **Electrical Fundamentals**. Similar to parasitic inductance, *any* circuit component that has wires attached to it, or is fabricated from wire, or is near or attached to metal, will have a parasitic capacitance associated with it, which again, becomes important only at RF.

Stray capacitance can be difficult to account for in circuit design because it exists *between* components and other circuit structures, depending on the physical orientation of the component. Its presence may allow signals to flow in ways that disrupt the normal operation of a circuit and may have a greater affect in a high-impedance circuit because the capacitive reactance may be a greater percentage of the circuit impedance. Also, because stray capacitance often appears in parallel with the circuit, the stray capacitor may bypass more of the desired signal at higher frequencies. Careful physical design of an RF circuit and selection of components can minimize the effects of stray capacitance.

#### **5.3.3 Inductors at Radio Frequencies**

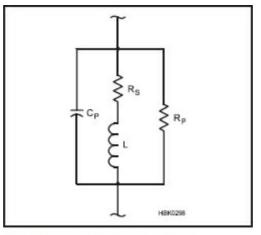

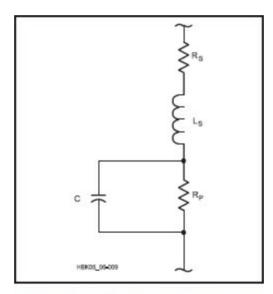

Inductors are perhaps the component with the most significant parasitic effects. Where there are many different varieties of form for capacitors and resistors, most inductors are fundamentally similar: a coil of wire on a tubular or toroidal form. As such, they are affected by both parasitic resistance and capacitance as shown in the simple inductor model of **Figure 5.14**.

Figure 5.14 — General model for inductor with parasitic capacitance and resistance. The parasitic capacitance represents the cumulative effect of the capacitance between the different turns of wire. Parasitic resistance,  $R_S$ , depends on frequency due to the skin effect.  $R_p$ represents leakage resistance. At low frequencies, parasitic capacitance,  $C_p$ , can be neglected.

While the leakage conductance of a capacitor is usually negligible, the series resistance of an inductor often is not. This is caused by the long lengths of thin wire needed to create typical inductance values used in RF circuits and the skin effect (discussed below). Consider a typical air-core inductor, with L = 33 mH and a minimum Q of 30 measured at 2.5 MHz. This would indicate a series resistance of  $R_s = 2 \pi f L / Q = 17 \Omega$  that could significantly alter the bandwidth of a circuit. The skin effect also results in parasitic resistance in the upper HF ranges and above. To minimize losses due to the skin effect, inductors at these frequencies, particularly those intended for use in transmitters and amplifiers and that are expected to carry significant currents, are often made from large-diameter wire or tubing or even flat strap to maximize the surface area for current flow.

For coils with many turns for which large conductors are impractical, *Litz wire* is sometimes used. Litz wire is made of many fine insulated strands woven together, each with a diameter smaller than the skin depth at the expected frequency of use, thus presenting a larger surface area than a solid wire or normal stranded wire. This creates multiple resistive inductors in parallel, which reduces the total impedance. The reduction is not proportional to the number of parallel paths, however, because they are inductively coupled.

If an inductor is wound on a magnetic core, the core itself can have losses that are treated as parasitic resistance. Each type of core — iron, powdered iron or ferrite — has a frequency range over which it is designed for maximum efficiency. Outside of that range, the core may have significant losses, raising the parasitic resistance of the inductor.

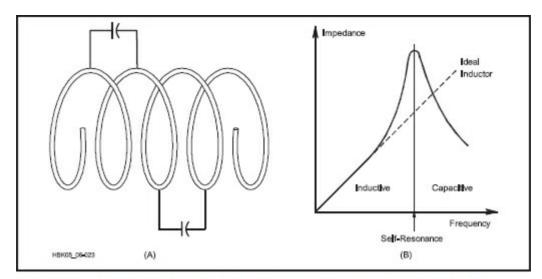

Parasitic capacitance is a particular concern for inductors because of their construction. Consider the inductor in **Figure 5.15**. If this coil has n turns, then the ac voltage between identical points of two neighboring turns is 1/n times the ac voltage across the entire coil. When this voltage changes due to an ac current passing through the coil, the effect is that of many small capacitors acting in parallel with the inductance of the coil. Thus, in addition to the capacitance resulting from the leads, inductors have higher parasitic capacitance due to their physical shape.

Figure 5.15 — Colls exhibit distributed capacitance as explained in the text. The graph at B shows how distributed capacitance resonates with the inductance. Below resonance, the reactance is predominantly inductive which increases as frequency increases. However, above resonance, the reactance becomes predominantly capacitive which decreases as frequency increases.

Figure 5.16 — Unshielded coils in close proximity should be mounted perpendicular to each other to minimize coupling.

These various effects illustrate why inductor construction has such a large effect on performance. As an example, assume you're working on a project that requires you to wind a 5  $\mu$ H inductor. Looking at the coil inductance formula in the **Electrical Fundamentals** chapter, it comes to mind that many combinations of length and diameter could yield the desired inductance. If you happen to have both 0.5 and 1-inch coil forms, why should you select one over the other? To eliminate some other variables, let's make both coils 1 inch long, close-wound, and give them 1-inch leads on each end.

Let's calculate the number of turns required for each. On a 0.5-inch-diameter form:

$$n = \frac{\sqrt{L(18d + 401)}}{d} = \frac{\sqrt{5[(18 \times 0.5) + (40 \times 1)]}}{0.5} = 31.3 \text{ turns}$$

This means coil 1 will be made from #20 AWG wire (29.9 turns per inch). Coil 2, on the 1-inch form, yields

$$n = \frac{\sqrt{5 \left[ (18 \times 1) + (40 \times 1) \right]}}{1} = 17 \text{ turns}$$

which requires #15 AWG wire in order to be close-wound.

What are the series resistances associated with each? For coil 1, the total wire length is 2 inches +  $(31.3 \times \pi \times 0.5) = 51$  inches, which at 10.1  $\Omega$  /1000 ft gives  $R_s = 0.043 \Omega$  at dc. Coil 2 has a total wire length of 2 inches +  $(17.0 \times \pi \times 1) = 55$  inches, which at 3.18  $\Omega$  /1000 ft gives a dc resistance of  $R_s = 0.015 \Omega$ , or about  $\nu_3$  that of coil 1. Furthermore, at RF, coil 1 will begin to suffer from skin effect at a frequency about 3 times lower than coil 2 because of its smaller conductor diameter. Therefore, if Q were the sole consideration, it would be better to use the larger diameter coil.

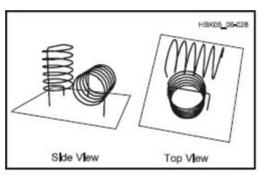

Q is not the only concern, however. Such coils are often placed in shielded enclosures. A common rule of thumb says that to prevent the enclosure from affecting the inductor, the enclosure should be at least one coil diameter from the coil on all sides. That is,  $3 \times 3 \times 2$  inches for the large coil and  $1.5 \times 1.5 \times 1.5$  for the small coil, a volume difference of over 500%.

#### **INDUCTOR COUPLING**

Mutual inductance (see the **Electrical Fundamentals** chapter) will also have an effect on the resonant frequency and Q of RF circuits. For this reason, inductors in frequency-critical circuits should always be oriented and with sufficient spacing to minimize coupling. For example, mount coils near each other with their axes perpendicular as in **Figure 5.16**. The use of ferrous cores also tends to keep magnetic fields within the core, reducing unwanted coupling.

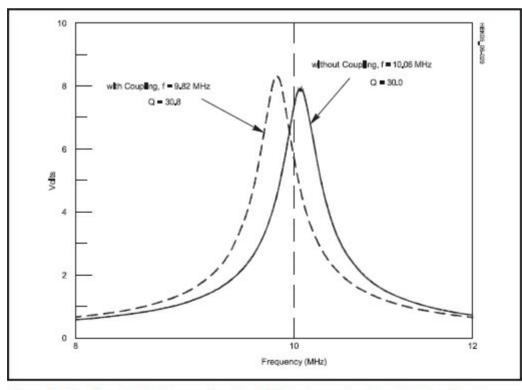

As an example, assume we build an oscillator circuit that has both input and output resonant circuits. If we are careful to keep the two coils in these circuits uncoupled, the frequency response of either of the two circuits is shown by the solid line in **Figure 5.17**.

Figure 5.17 — Result of light coupling (k = 0.05) between two identical circuits of Figure 5.19A on their frequency responses.

If the two coils are coupled either through careless placement or improper shielding, the resonant

frequency and Q will be affected. The dashed line in Figure 5.17 shows the frequency response that results from a coupling coefficient of k = 0.05, a reasonable value for air-wound inductors mounted perpendicularly in close proximity on a circuit chassis. Note the resonant frequency shifted from 10.06 to 9.82 MHz, or 2.4%. The Q has gone up slightly from 30.0 to 30.8 as a result of the slightly higher inductive reactance at the resonant frequency.

Capacitance between coils can also affect a circuit's frequency response. Using shielded inductors or canmounted coils reduces the effects of stray capacitance between components.

#### 5.3.4 Skin Effect

The resistance of a conductor to ac is different than its value for dc because of the way ac fields interact with the conductor. As a result, thick, near-perfect conductors (such as metals) conduct ac only to a certain *skin depth*,  $\delta$ , inversely proportional to the square root of the frequency of the current. Called the *skin effect*, this decreases the effective cross-section of the conductor at high frequencies and thus increases its resistance.

$$\delta = \frac{1}{\sqrt{\pi f \,\mu \sigma}} \tag{2}$$

where

$\mu$  is the conductor's permeability, and

$\sigma$  is the conducting material's conduc- tance.

The increase in resistance caused by the skin effect is insignificant at and below audio frequencies, but beginning around 1 MHz (depending on the size of the conductor) it is so pronounced that practically all the current flows in a very thin layer near the conductor's surface. For example, at 10 MHz, the skin depth of a copper conductor is about 0.02 mm (0.00079 inch). For this reason, at RF a hollow tube and a solid rod of the same diameter and made of the same metal will have the same resistance and the RF resistance of a conductor is often much higher than its dc resistance. A rough estimate of the frequency above which a nonmagnetic wire (one made of nonferrous metal) will begin to show appreciable skin effect can be calculated from

$$f = \frac{124}{d^2}$$

(3)

where

f = frequency, in MHz

d = diameter in mils (a mil is 0.001 inch)

Above this frequency, increase the resistance of the wire by  $10 \times$  for every 2 decades of frequency (roughly  $3.2 \times$  for every decade). For example, say we wish to find the RF resistance of a 2-inch length of #18 AWG copper wire at 100 MHz. From the wire tables in the **Component Data and References** chapter, we see that this wire has a dc resistance of 2 inches  $\times$  6.386  $\Omega/1000$  ft = 1.06 mW. From the above formula, the frequency is found to be  $124 / 40.3^2 = 76$  kHz. Since 100 MHz is roughly three decades above this (100 kHz to 100 MHz), the RF resistance will be approximately  $1.06 \text{ m}\Omega \times 3.2^3 = 1.06 \text{ m}\Omega \times 32.8 = 34.8 \text{ m}\Omega$ . Again, values calculated in this manner are approximate and should be used qualitatively — like when you want an answer to a question such as, "Can I neglect the RF resistance of this length of connecting wire at 100 MHz?" Several useful charts regarding skin effect are available in *Reference Data for Engineers*, listed in the References section of this chapter.

Losses associated with skin effect can be reduced by increasing the surface area of the conductor carrying the RF current. Flat, solid strap and tubing are often used for that reason. In addition, because the current-carrying layer is so thin at UHF and microwave frequencies, a thin highly conductive layer at the surface of the conductor, such as silver plating, can lower resistance. Silver plating is too thin to improve HF conductivity significantly, however.

#### 5.3.5 RF Heating

RF current often causes component heating problems where the same level of dc or low frequency ac current may not. These losses result from both the skin effect and from dielectric losses in insulating material, such as a capacitor dielectric.

An example is the tank circuit of an RF oscillator. If several small capacitors are connected in parallel to achieve a desired capacitance, skin effect will be reduced and the total surface area available for heat dissipation will be increased, thus significantly reducing the RF heating effects as compared to a single large capacitor. This technique can be applied to any similar situation; the general idea is to divide the heating among as many components as possible.

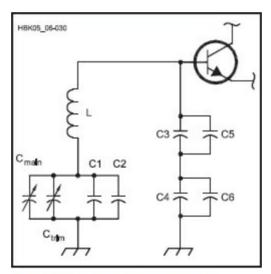

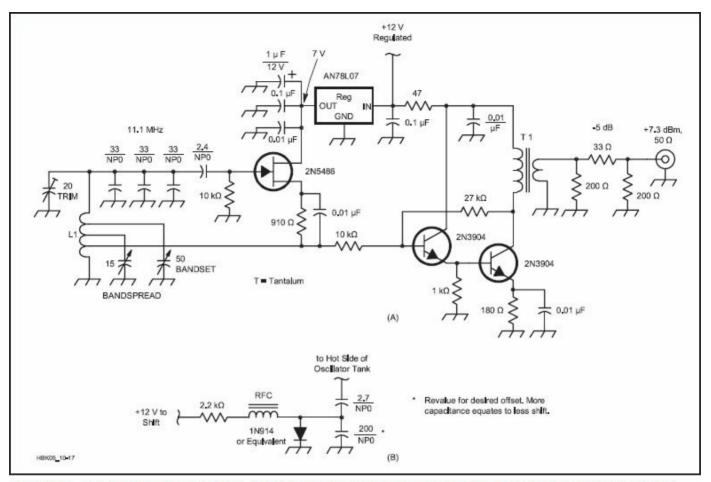

An example is shown in the circuit block in **Figure 5.18**, which is representative of the input tank circuit used in many HF VFOs. Along with L,  $C_{main}$ ,  $C_{trim}$ , C1 and C3 set the oscillator frequency. Therefore, temperature effects are critical in these components. By using several capacitors in parallel, the RF current (and resultant heating, which is proportional to the square of the current) is reduced in each component. Parallel combinations are used for the feedback capacitors for the same reason.

Figure 5.18 — A tank circuit of the type commonly used in VFOs. Several capacitors are used in parallel to distribute the RF current, which reduces temperature effects.

At high power levels, losses due to RF heating — either from resistive or dielectric losses — can be significant. Insulating materials may exhibit dielectric losses even though they are excellent insulators. For example, nylon plastic insulators may work very well at low frequencies, but being quite lossy at and above VHF, they are unsuitable for use in RF circuits at those frequencies. To determine whether material is suitable for use as an insulator at RF, a quick test can be made by heating the material in a microwave oven for a few seconds and measuring its temperature rise. (Take care to avoid placing parts or materials containing any metal in the microwave!) Insulating materials that heat up are lossy and thus unsuitable for use in RF circuits.

#### 5.3.6 Effect on Q

Recall from the **Electrical Fundamentals** chapter that circuit Q, a useful figure of merit for tuned RLC circuits, can be defined in several ways:

$$Q = \frac{X_L \text{ or } X_C}{R}$$

<sup>(4)</sup>

# $=\frac{\text{energy stored per cycle}}{\text{energy dissipated per cycle}}$

Q is also related to the bandwidth of a tuned circuit's response by

$$Q = \frac{f_0}{BW_{3 dB}}$$

<sup>(5)</sup>

Parasitic inductance, capacitance and resistance can significantly alter the performance and characteristics of a tuned circuit if the design frequency is close to the self-resonant frequencies of the components.

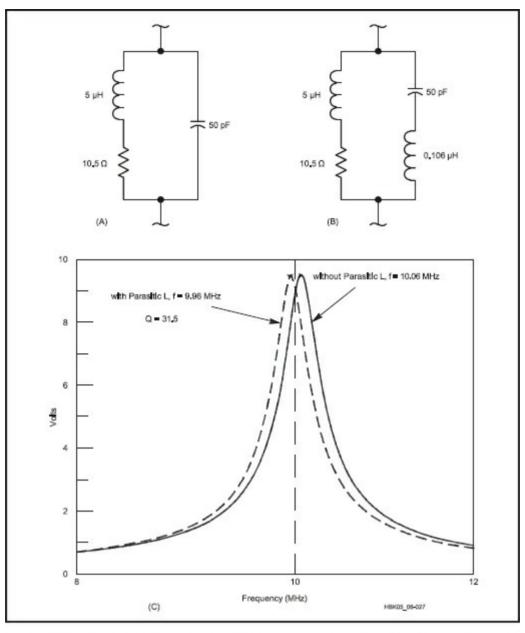

As an example, consider the resonant circuit of **Figure 5.19A**, which could represent the frequencydetermining resonant circuit of an oscillator. Neglecting any parasitics,

Figure 5.19 — A is a tank circuit, neglecting parasitics. B is the same circuit including  $L_p$  on capacitor. C is the frequency response curves for A and B. The solid line represents the unaltered circuit (also see Figure 5.17) while the dashed line shows the effects of adding parasitic inductance.

$$f_0 = \frac{1}{2\pi\sqrt{LC}} = 10.06 \text{ MHz}$$

As in many practical cases, assume the resistance arises entirely from the inductor series resistance. The data sheet for the inductor specified a minimum Q of 30, so assuming Q = 30 yields an R value of

$$\frac{X_{L}}{Q} = \frac{2\pi (10.06 \text{ MHz}) (5 \,\mu\text{H})}{30} = 10.5 \,\Omega$$

Next, let's include the parasitic inductance of the capacitor (Figure 5.19B). A reasonable assumption is

that this capacitor has the same physical size as the example from the section on Parasitic Inductance for which we calculated  $L_s = 0.106 \mu$ H. This would give the capacitor a self-resonant frequency of 434 MHz — well above our frequency of interest. However, the added parasitic inductance does account for an extra 0.106/5.0 = 2% inductance. Since this circuit is no longer strictly series or parallel, we must convert it to an equivalent form before calculating the new  $f_0$ .

An easier and faster way is to *simulate* the altered circuit by computer. This analysis was performed on a desktop computer using *SPICE*, a standard circuit simulation program described in the **Computer-Aided Circuit Design** chapter. The voltage response of the circuit (given an input current of 1 mA) was calculated as a function of frequency for both cases, with and without parasitics. The results are shown in the plot in Figure 5.19C, where we can see that the parasitic circuit has an f<sub>0</sub> of 9.96 MHz (a shift of 1%) and a Q (measured from the -3 dB points) of 31.5. For comparison, the simulation of the unaltered circuit does in fact show f<sub>0</sub> = 10.06 MHz and Q = 30.

## 5.3.7 Self-Resonance

Because of parasitic effects, a capacitor or inductor — all by itself — exhibits the properties of a resonant RLC circuit at frequencies for which the parasitic effects are significant. Figs 5.10 and 5.14 illustrate RF models for the capacitor and inductor, which are based on the general model in Figure 5.4, leaving out the packaging capacitance. Note the slight difference in configuration; the pairs  $C_p$ - $R_p$  and  $L_s$ - $R_s$  are in series in the capacitor but in parallel in the inductor. This is because of the different physical structure of the components.

At some sufficiently high frequency, both inductors and capacitors become *self-resonant* when the parasitic reactance cancels or equals the intended reactance, creating a series-resonant circuit. Similar to a series-resonant circuit made of discrete components, above the self-resonant frequency a capacitor will appear inductive, and an inductor will appear capacitive.

For an example, let's calculate the approximate self-resonant frequency of a 470-pF capacitor whose leads are made from #20 AWG wire (0.032-inch diameter), with a total length of 1 inch. Using equation 1, we calculate the approximate parasitic inductance

L (µH) = 0.00508 (1)

$$\left[ \ln \left( \frac{2(1)}{(0.032/2)} \right) - 0.75 \right]$$

# $= 0.021 \,\mu H$

and the self-resonant frequency is roughly

$$f = \frac{1}{2\pi\sqrt{LC}} = 50.6 \text{ MHz}$$

Similarly, an inductor can also have a parallel self-resonance.

The purpose of making these calculations is to provide a feel for actual component values. They could be used as a rough design guideline, but should not be used quantitatively. Other factors such as lead orientation, shielding and so on, can alter the parasitic effects to a large extent. Large-value capacitors tend to have higher parasitic inductances (and therefore a lower self-resonant frequency) than small-value capacitors.

Self-resonance becomes critically important at VHF and UHF because the self- resonant frequency of many common components is at or below the frequency where the component will be used. In this case, either special techniques can be used to construct components to operate at these frequencies, by reducing the parasitic effects, or else the idea of lumped elements must be abandoned altogether in favor of microwave techniques such as striplines and waveguides.

## 5.3.8 Dielectric Breakdown and Arcing

Anyone who has ever seen an arc form across a transmitting capacitor's plates, seen static discharges jump across an antenna insulator or touched a metal doorknob on a dry day has experienced the effects of dielectric breakdown.

In the ideal world, we could take any two conductors and put as large a voltage as we want across them, no matter how close together they are. In the real world, there is a voltage limit (*dielectric strength*, measured in kV/cm and determined by the insulating material between the two conductors) above which the insulator will break down.

Because they are charged particles, the electrons in the atoms of a dielectric material feel an attractive force when placed in an electric field. If the field is sufficiently strong, the force will strip the electron from the atom. This electron is available to conduct current, and furthermore, it is traveling at an extremely high velocity. It is very likely that this electron will hit another atom, and free another electron. Before long, there are many stripped electrons producing a large current, forming an *arc*. When this happens, we say the dielectric has suffered *breakdown*. Arcing in RF circuits is most common in transmitters and transmission line components where high voltages are common, but it is possible anywhere two components at significantly different voltage levels are closely spaced.

If the dielectric is liquid or gas, it will repair itself when the applied voltage is removed and the molecules in the dielectric return to their normal state. A solid dielectric, however, cannot repair itself because its molecules are fixed in place and the low-resistance path created by the arc is permanent. A good example of this is a CMOS integrated circuit. When exposed to the very high voltages associated with static electricity, the electric field across the very thin gate oxide layer exceeds the dielectric strength of silicon dioxide, and the device is permanently damaged by the resulting hole created in the oxide layer.

The breakdown voltage of a dielectric layer depends on its composition and thickness (see **Table 5.1**). The variation with thickness is not linear; doubling the thickness does not quite double the breakdown voltage. Breakdown voltage is also a function of geometry: Because of electromagnetic considerations, the breakdown voltage between two conductors separated by a fixed distance is less if the surfaces are pointed or sharp-edged than if they are smooth or rounded. Therefore, a simple way to help prevent breakdown in many projects is to file and smooth the edges of conductors. (See the **Power Sources** and **RF Power Amplifier** chapters for additional information on high voltage applications.)

| Material              | Dielectric | Puncture  |

|-----------------------|------------|-----------|

|                       | Constant*  | Voltage** |

| Aisimag 196           | 5.7        | 240       |

| Bakelite              | 4.4-5.4    | 240       |

| Bakelite, mica filled | 4.7        | 325-375   |

| Cellulose acetate     | 3.3-3.9    | 250-600   |

| Fiber                 | 5-7.5      | 150-180   |

| Formica               | 4.6-4.9    | 450       |

| Glass, window         | 7.6-8      | 200-250   |

| Glass, Pyrex          | 4.8        | 335       |

| Mica, ruby            | 5.4        | 3800-5600 |

| Mycalex               | 7.4        | 250       |

| Paper, Royalgrey      | 3.0        | 200       |

| Plexiglas             | 2.8        | 990       |

| Polyethylene          | 2.3        | 1200      |

| Polystyrene           | 2.6        | 500-700   |

| Porcelain             | 5.1-5.9    | 40-100    |

| Quartz, fused         | 3.8        | 1000      |

| Steatite, low loss    | 5.8        | 150-315   |

| Teflon                | 2.1        | 1000-2000 |

Capacitors are, by nature, the component most often associated with dielectric failure. To prevent damage, the working voltage of a capacitor — and there are separate dc and ac ratings — should ideally be two or three times the expected maximum voltage in the circuit. Capacitors that are not air-insulated or have a *self-healing dielectric* should be replaced if a dielectric breakdown occurs.

Resistors and inductors also have voltage ratings associated with breakdown of their insulating coating. High-value resistors, in particular, can be bypassed by leakage current flowing along the surface of the resistor. High-voltage resistors often have elongated bodies to create a long *leakage path* to present a high resistance to leakage current. Cleaning the bodies of resistors and inductors in high-voltage circuits helps prevent arcs from forming and minimizes leakage current.

## 5.3.9 Radiative Losses

Any conductor placed in an electromagnetic field will have a current induced in it. We put this principle to good use when we make an antenna. The unwelcome side of this law of nature is the phrase "any conductor"; even conductors we don't intend to act as antennas will respond this way.

Fortunately, the efficiency of such "antennas" varies with conductor length. They will be of importance only if their length is a significant fraction of a wavelength. When we make an antenna, we usually choose a length on the order of  $\lambda/2$ . Therefore, when we *don't* want an antenna, we should be sure that the conductor length is *much less* than  $\lambda/2$ , no more than 0.1  $\lambda$ . This will ensure a very low-efficiency antenna. This is why even unpaired 60-Hz power lines do not lose a significant fraction of the power they carry — at 60 Hz, 0.1  $\lambda$  is about 300 miles!

In addition, we can use shielded cables. Such cables do allow some penetration of EM fields if the shield is not solid, but even 95% coverage is usually sufficient, especially if some sort of RF choke is used to reduce shield current.

Radiative losses and coupling can also be reduced by using twisted or parallel pairs of conductors — the fields tend to cancel. In some applications, such as audio cables, this may work better than shielding. Critical stages such as tuned circuits should be placed in shielded compartments where possible.

This argument also applies to large components — remember that a component or long wire can both radiate and receive RF energy. Measures that reduce radiative losses will also reduce unwanted RF pickup. See the **RF Interference** chapter for more information.

## 5.3.10 Bypassing and Decoupling

### **BYPASSING**

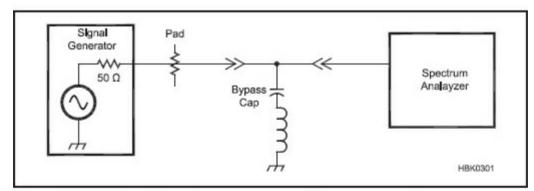

Circuit models showing ac behavior often show ground connections that are not at dc ground. Bias voltages and currents are neglected in order to show how the circuit responds to ac signals. Rather, those points are "signal grounded" through bypass capacitors. Obtaining an effective bypass can be difficult and is often the route to design difficulty. The problem is parasitic inductance. Although we label and model parts as "capacitors," a more complete model is needed. The better model is a series RLC circuit, shown in **Figure 5.20**. Capacitance is close to the marked value while inductance is a small value that grows with component lead length. Resistance is a loss term, usually controlled by the Q of the parasitic inductor. Even a leadless SMT (surface-mount technology) component will display inductance commensurate with its dimensions. As shown in the Parasitic Inductance section, wire component leads have an inductance of about 1 nH per mm of length (20-25 nH per inch).

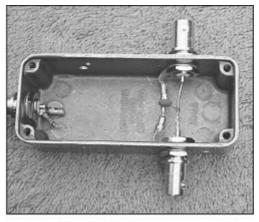

Bypass capacitor characteristics can be measured in the home lab with the test setup of **Figure 5.21**. **Figure 5.22** shows a test fixture with an installed 470-pF leaded capacitor. The fixture is used with a signal generator and spectrum analyzer to evaluate capacitors. Relatively long capacitor leads were required to interface to the BNC connectors, even though the capacitor itself was small. The signal generator was tuned over its range while examining the spectrum analyzer response, showing a minimum at the series resonant frequency. Parasitic inductance is calculated from this frequency. The C value was measured with a low-frequency LC meter. Additional test instruments and techniques are discussed in the **Test Equipment and Measurement** chapter.

Figure 5.21 — Test set for home lab measurement of a bypass capacitor.

Figure 5.22 — Test fixture for measuring self-resonant frequency of capacitors.

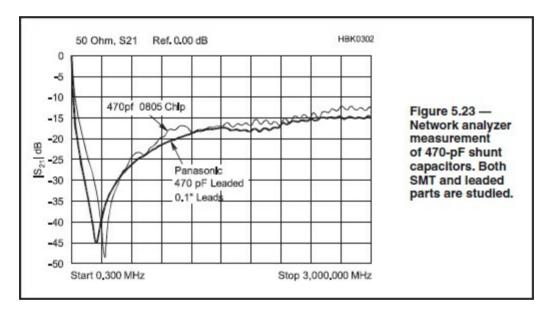

The measured 470-pF capacitor is modeled as 485 pF in series with an inductance of 7.7 nH. The L is larger than we would see with shorter leads. A 0.25-inch 470-pF ceramic disk capacitor with zero lead length will show a typical inductance closer to 3 nH. The measured capacitor Q was 28 at its self-resonance of 82 MHz but is higher at lower frequency. Data from a similar measurement, but with a network analyzer is shown in **Figure 5.23**. Two 470-pF capacitors are measured, one surface mounted and the other a leaded part with 0.1-inch leads.

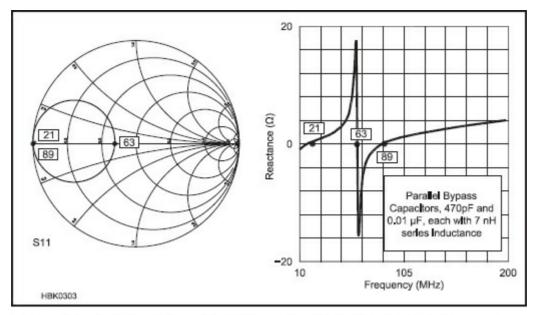

It is often suggested that the bandwidth for bypassing can be extended by paralleling a capacitor that works well at one frequency with another to accommodate a different part of the spectrum. Hence, paralleling the 470 pF with a 0.01- $\mu$ F capacitor should extend the bypassing to lower frequencies. The calculations are shown in the plots of **Figure 5.24**. The results are terrible! While the low frequency bypassing is indeed improved, a high impedance response is created at 63 MHz. This complicated behavior is again the result of inductance. Each capacitor was assumed to have a series inductance of 7 nH. A parallel resonance is approximately formed between the L of the larger capacitor and the C of the smaller. The Smith Chart plot shows us that the impedance is nearly 50  $\Omega$  at 63 MHz. Impedance would be even higher with greater capacitor Q.

Figure 5.24 — The classic technique of paralleling bypass capacitors of two values, here 470 pF and 0.01  $\mu$ F. This is a *terrible* bypass! See text.

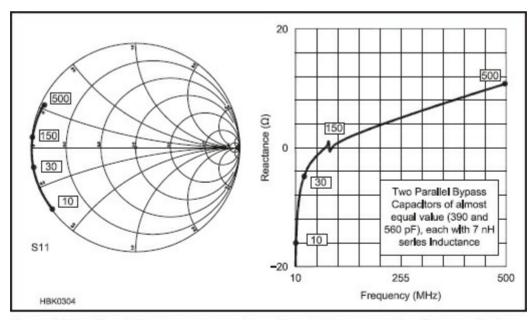

Bypassing can be improved by paralleling capacitors. However, the capacitors should be approximately identical. **Figure 5.25** shows the result of paralleling two capacitors of about the same value. They differ slightly at 390 and 560 pF, creating a hint of resonance. This appears as a small perturbation in the reactance plot and a tiny loop on the Smith Chart. These anomalies disappear as the C values become equal. Generally, paralleling is the scheme that produces the best bypassing. The ideal solution is to place an SMT capacitor on each side of a printed circuit trace or wire at a point that is to be bypassed.

Figure 5.25 — Paralleling bypass capacitors of nearly the same value. This results in improved bypassing without complicating resonances.

Matched capacitor pairs form an effective bypass over a reasonable frequency range. Two 0.01- $\mu$ F disk capacitors have a reactance magnitude less than 5  $\Omega$  from 2 to 265 MHz. A pair of the 0.1- $\mu$ F capacitors was even better, producing the same bypassing impedance from 0.2 to 318 MHz. The 0.1- $\mu$ F capacitors are chip-style components with attached wire leads. Even better results can be obtained with multi-layer ceramic chip capacitors. Construction with multiple layers creates an integrated paralleling.

Some applications (for example, IF amplifiers) require effective bypassing at even lower frequencies.

Modern tantalum electrolytic capacitors are surprisingly effective through the RF spectrum while offering high enough C to be useful at audio. In critical applications, however, the parts should be tested to be sure of their effectiveness.

## DECOUPLING

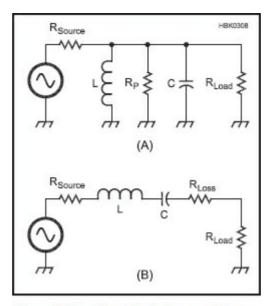

The bypass capacitor usually serves a dual role, first creating the low impedance needed to generate a "signal" ground. It also becomes part of a decoupling low-pass filter that passes dc while attenuating signals. The attenuation must function in both directions, suppressing noise in the power supply that might reach an amplifier while keeping amplifier signals from reaching the power supply. A low-pass filter is formed with alternating series and parallel component connections. A parallel bypass is followed by a series impedance, ideally a resistor.

Additional shunt elements can then be added, although this must be done with care. An inductor between shunt capacitors should have high inductance. It will resonate with the shunt capacitors to create high impedances just like those that came from parasitic inductance in the bypasses. This makes it desirable to have an inductance that is high enough that any resonance is below the band of interest. But series inductors have their own problems; they have parasitic capacitance, creating their own self-resonance. As an example, a pair of typical RF chokes (RFCs) were measured (now as series elements) as described earlier. A 2.7- $\mu$ H molded choke was parallel resonant at 200 MHz, indicating a parallel capacitance of 0.24 pF. The Q at 20 MHz was 52. A 15- $\mu$ H molded choke was parallel resonant at 47 MHz, yielding a parallel C of 0.79 pF. This part had a Q of 44 at 8 MHz.

Large inductors can be fabricated from series connections of smaller ones. The best wideband performance will result only when all inductors in a chain have about the same value. The reasons for this (and the mathematics that describe the behavior) are identical with those for paralleling identical capacitors.

Low inductor Q is often useful in decoupling applications, encouraging us to use inductors with ferrite cores. Inductors using the Fair-Rite Type #43 material have low Q in the 4 to 10 range over the HF spectrum. One can also create low-Q circuits by paralleling a series inductor of modest Q with a resistor.

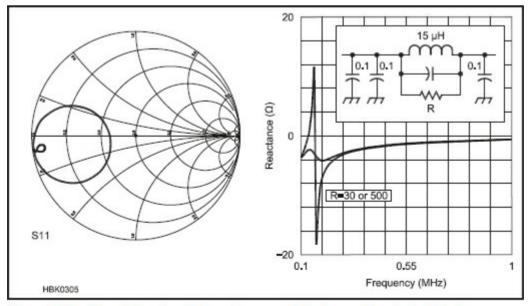

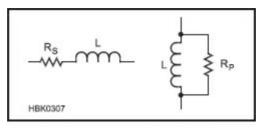

**Figure 5.26** shows a decoupling network and the resulting impedance when viewed from the "bypass" end. The 15- $\mu$ H RFC resonates with a 0.1- $\mu$ F capacitor to destroy the bypass effect just above 0.1 MHz. A low-value parallel resistor fixes the problem.

Figure 5.26 — Two different resistor values parallel a decoupling choke. The lower,  $30-\Omega$  value is more effective. See text.

A major reason for careful wideband bypassing and decoupling is the potential for amplifier oscillation. Instability that allows oscillations is usually suppressed by low impedance terminations. The base and collector (or gate and drain) should both "see" low impedances to ensure stability. But that must be true at all frequencies where the device can produce gain. It is never enough to merely consider the operating frequency for the amplifier. A parallel resonance in the base or collector circuits can be a disaster. When wideband bypassing is not possible, negative feedback that enhances wideband stability is often used.

Emitter bypassing is often a critical application. As demonstrated in the **Circuits and Components** chapter, a few extra ohms of impedance in the emitter circuit can drastically alter amplifier performance. A parallel-resonant emitter bypass could be a profound difficulty while a series-resonant one can be especially effective.

Capacitors also appear in circuits as blocking elements. A blocking capacitor, for example, appears between stages, creating a near short circuit for ac signals while accommodating different dc voltages on the two sides. A blocking capacitor is not as critical as a bypass, for the impedances on either side will usually be higher than that of the block.

With parasitic effects having the potential to strongly affect circuit performance, the circuit designer must account for them wherever they are significant. The additional complexity of including parasitic elements can result in a design too complex to be analyzed manually. Clearly, detailed modeling is the answer to component selection and the control of parasitic effects.

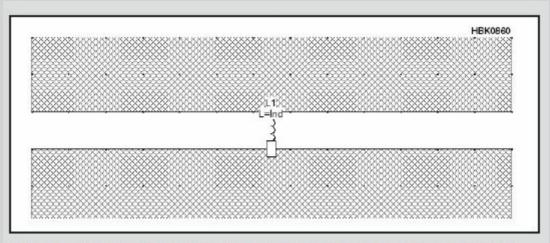

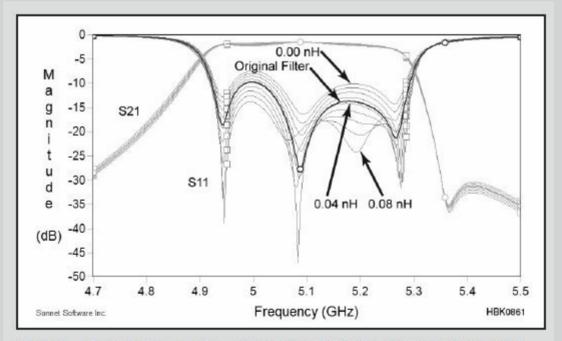

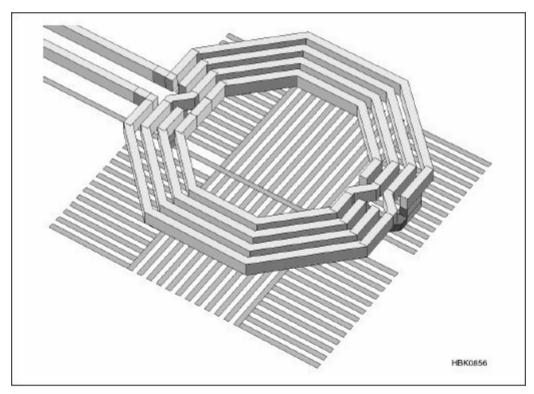

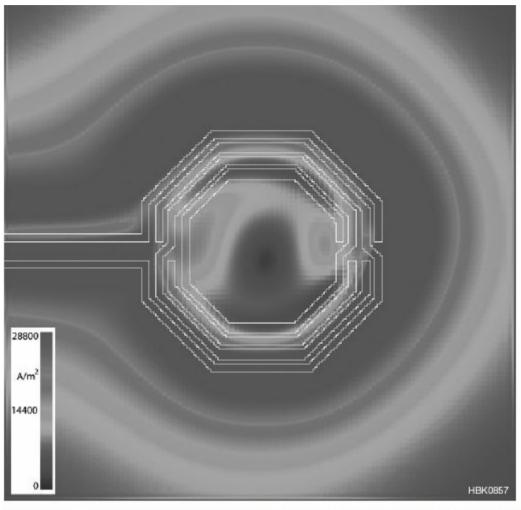

## **5.3.11 Effects on Filter Performance**

LC bandpass filters perform a critical function in determining the performance of a typical RF system such as a receiver. An input filter, usually a bandpass, restricts the frequency range that the receiver must process. Transmitters use LC filters to reduce harmonic output. Audio and LF filters may also use LC elements. The LC filters we refer to in this section are narrow with a bandwidth from 1 to 20% of the center frequency. Even narrower filters are built with resonators having higher Q; the quartz crystal filter discussed in the **Analog and Digital Filtering** chapter is used where bandwidths of less than a part per thousand are possible. The basic concepts that we examine with LC circuits will transfer to the crystal filter.

## LOSSES IN FILTERS AND Q

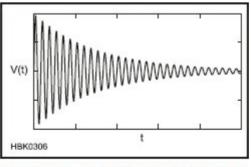

The key elements in narrow filters are tuned circuits made from inductor-capacitor pairs, quartz crystals, or transmission line sections. These resonators share the property that they store energy, but they have losses. A chime is an example. Striking the chime with a hammer produces the waveform of **Figure 5.27**. The rate at which the amplitude decreases with time after the hammer strike is determined by the filter's Q, which is discussed in the chapter on **Circuits and Components**. The higher the Q, the longer it takes for the sound to disappear. The oscillator amplitude would not decrease if it were not for the losses that expend energy stored in the resonator. The mere act of observing the oscillation will cause some energy to be dissipated.

Figure 5.27 — The amplitude of a chime's ring after being struck by a hammer. Units are arbitrary.

A chime is an acoustic resonator, but the same behavior occurs in electric resonators. A pulse input to an