March/April 2013

C11

## A Forum for Communications Experimenters

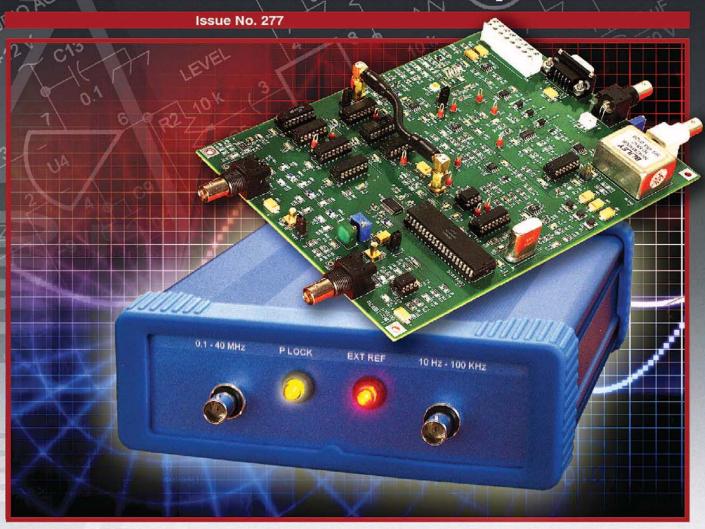

K61QL presents A Precision DDS for the Frequency Measuring Tests. A bit more involved than many of the DDS projects we have seen, this one provides resolution accuracy to the nearest 0.1 millihertz.

## **Nothing But Performance**

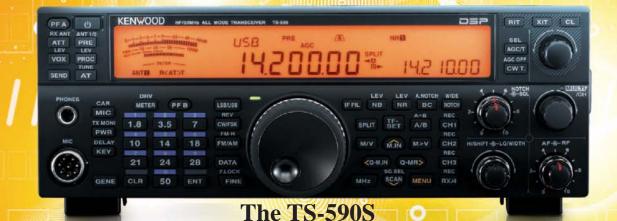

Kenwood has essentially redefined HF performance with the TS-590S compact HF transceiver. The TS-590S RX section sports IMD (intermodulation distortion) characteristics that are on par with those "top of the line" transceivers, not to mention having the best dynamic range in its class when handling unwanted, adjacent off-frequency signals.\*

- HF-50MHz 100W

- Digital IF Filters

- Built-in Antenna Tuner

- Advanced DSP from the IF stage forward

- 500Hz and 2.7KHz roofing filters included

- Heavy duty TX section

download TS-590S brochure.

2 Color LCD

**KENWOOI**

Customer Support: (310) 639-4200 Fax: (310) 537-8235

QEX (ISSN: 0886-8093) is published bimonthly in January, March, May, July, September, and November by the American Radio Relay League, 225 Main Street, Newington, CT 06111-1494. Periodicals postage paid at Hartford, CT and at additional mailing offices.

POSTMASTER: Send address changes to: QEX, 225 Main St, Newington, CT 06111-1494 Issue No 277

Harold Kramer, W.I1B Publisher

Larry Wolfgang, WR1B Editor

Lori Weinberg, KB1EIB Assistant Editor

Zack Lau, W1VT Ray Mack, W5IFS Contributing Editors

#### **Production Department**

Steve Ford, WB8IMY Publications Manager

Michelle Bloom, WB1ENT Production Supervisor

Sue Fagan, KB1OKW Graphic Design Supervisor

David Pingree, N1NAS Senior Technical Illustrator

Carol Michaud, KB1QAW Technical Illustrator

#### **Advertising Information Contact:**

Janet L. Rocco, W1JLR Business Services 860-594-0203 - Direct 800-243-7768 - ARRL 860-594-4285 - Fax

#### **Circulation Department**

Cathy Stepina, QEX Circulation

#### Offices

225 Main St, Newington, CT 06111-1494 USA Telephone: 860-594-0200 Fax: 860-594-0259 (24 hour direct line) e-mail: qex@arrl.org

#### Subscription rate for 6 issues:

In the US: ARRL Member \$24, nonmember \$36;

US by First Class Mail: ARRL member \$37, nonmember \$49;

International and Canada by Airmail: ARRL member \$31, nonmember \$43;

Members are asked to include their membership control number or a label from their QST when

In order to ensure prompt delivery, we ask that you periodically check the address information on your mailing label. If you find any inaccuracies, please contact the Circulation Department immediately. Thank you for your assistance.

Copyright © 2013 by the American Radio Relay League Inc. For permission to quote or reprint material from QEX or any ARRL publication, send a written request including the issue date (or book title), article, page numbers and a description of where you intend to use the reprinted material. Send the request to the office of the Publications Manager (permission@arrl.org).

#### March/April 2013

#### **About the Cover**

John Roos, K6IQL, presents A Precision DDS for the Frequency Measuring Tests. Unlike many of the DDS projects we have seen, this one provides resolution accuracy to the nearest 0.1 millihertz, with an RF output between 100 kHz and 40 MHz. This meets John's requirements for an FMT DDS.

In This Issue

### **Features**

A Two Turn Magnetic Loop Antenna for 30 through 10 Meters

Wayne Openlander, W9NZB

**Fun with Voltage-to-Frequency Converters** Dr Sam Green, WØPCE

**A Precision DDS for the Frequency Measurement Tests** John C. Roos, K6IQL

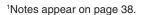

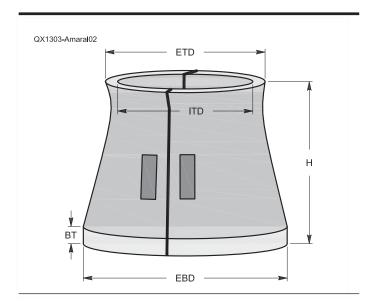

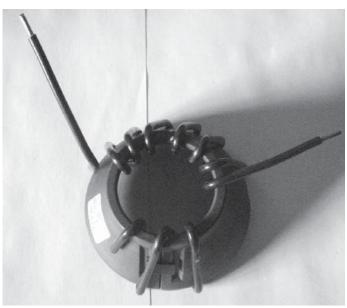

An Output Filter for My 500 kHz CW Transmitter Luiz Amaral, PY1LL/AC2BR

**SDR: Simplified** Ray Mack, W5IFS

#### **Index of Advertisers**

| American Radio Relay League: | 47, Cover II |

|------------------------------|--------------|

| Down East Microwave Inc:     | 38           |

| Kenwood Communications:      | Cover II     |

| National RF Inc:             | 46           |

| Nemal Electronics International, | , Inc:3  | 8 |

|----------------------------------|----------|---|

| Quicksilver Radio Products       | Cover I' | V |

| RF Parts:                        | 45, 4    | 7 |

| Tucson Amateur Packet Radio:     | 4        | 8 |

#### **The American Radio Relay League**

The American Radio Relay League, Inc, is a noncommercial association of radio amateurs, organized for the promotion of interest in Amateur Radio communication and experimentation, for the establishment of networks to provide communications in the event of disasters or other emergencies, for the advancement of the radio art and of the public welfare, for the representation of the radio amateur in legislative matters, and for the maintenance of fraternalism and a high standard of conduct.

ARRL is an incorporated association without capital stock chartered under the laws of the state of Connecticut, and is an exempt organization under Section 501(c)(3) of the Internal Revenue Code of 1986. Its affairs are governed by a Board of Directors, whose voting members are elected every three years by the general membership. The officers are elected or appointed by the Directors. The League is noncommercial, and no one who could gain financially from the shaping of its affairs is eligible for membership on its Board.

"Of, by, and for the radio amateur," ARRL numbers within its ranks the vast majority of active amateurs in the nation and has a proud history of achievement as the standard-bearer in amateur

A bona fide interest in Amateur Radio is the only essential qualification of membership; an Amateur Radio license is not a prerequisite, although full voting membership is granted only to licensed amateurs in the US.

Membership inquiries and general correspondence should be addressed to the administrative headquarters:

225 Main Street Newington, CT 06111 USA Telephone: 860-594-0200 FAX: 860-594-0259 (24-hour direct line)

President: KAY C. CRAIGIE, N3KN 570 Brush Mountain Rd, Blacksburg, VA 24060

Chief Executive Officer: DAVID SUMNER, K1ZZ

#### The purpose of QEX is to:

- 1) provide a medium for the exchange of ideas and information among Amateur Radio experimenters,

- 2) document advanced technical work in the Amateur Radio field, and

- 3) support efforts to advance the state of the Amateur Radio art.

All correspondence concerning QEX should be addressed to the American Radio Relay League, 225 Main Street, Newington, CT 06111 USA. Envelopes containing manuscripts and letters for publication in QEX should be marked Editor, QEX.

Both theoretical and practical technical articles are welcomed. Manuscripts should be submitted in word-processor format, if possible. We can redraw any Figures as long as their content is clear.

Photos should be glossy, color or black-and-white prints of at least the size they are to appear in QEX or high-resolution digital images (300 dots per inch or higher at the printed size). Further information for authors can be found on the Web at www.arrl.org/qex/ or by e-mail to qex@arrl.org.

Any opinions expressed in QEX are those of the authors, not necessarily those of the Editor or the League. While we strive to ensure all material is technically correct, authors are expected to defend their own assertions. Products mentioned are included for your information only; no endorsement is implied. Readers are cautioned to verify the availability of products before sending money to vendors.

#### Larry Wolfgang, WR1B

### **Empirical Outlook**

### **Experimenting for Fun and Necessity**

QEX: A Forum for Communications Experimenters. There, it says it right in the title of our magazine: QEX is for experimenters. What kind of experimenting do you do? Why do you experiment? What do you learn from or gain from your experiments?

Most of us will be quick to say that experimenting is fun. We build projects, test new circuits, even try new communications modes, because it we enjoy it. Along the way we learn something new, whether it is a personal accomplishment such as a deeper understanding of some electronics principle, or perhaps we help advance the state of the electronics/communications art.

When you share the results of your experimentation you help your fellow Amateurs gain insight and understanding. You may spur some to continue your research and provide even greater benefits to the Amateur Radio community or mankind.

That may seem like quite a lot, just from one QEX article, but who knows where that information may lead someone else. By sharing the joy of building projects and experimenting with electronics you might be inspiring the next generation of scientists and engineers.

We share some of those "stories" in every issue of QEX, and this one is no exception.

Wayne Openlander, W9NZB, describes his efforts to build a small magnetic loop antenna for 20 meters. Wayne's article is not a construction project, but a story about some of the experiments he conducted along his journey. Using an infrared thermometer to search for hot spots along his loop is an interesting idea. Perhaps others will find this technique useful in other ways.

Sam Green, WØPCE, describes some of the fun he had experimenting with voltage to frequency converter ICs. Sam describes several ways he used these converters to create an audio signal that he could hear as he adjusted various circuits or equipment. There are several ideas here that readers may find helpful in their own experimentation. Sam even describes one circuit that lead to a patent application. Who knows where your experiments might lead?

John Roos, K6IQL, describes a direct digital synthesizer circuit that he developed with one of his particular interests in mind — ARRL frequency measuring tests (FMT). John points out that you would need a reference oscillator accuracy of 7 parts in one billion to accurately measure a 40 meter signal in one of these tests. A DDS that would prove perfectly adequate as a transceiver LO or VFO will not fulfill the needs for an FMT station. John describes his efforts to build a suitable DDS While his circuitry is a bit more involved than the typical DDS that we have looked at, he did achieve a synthesizer that provides mHz resolution, suitable for his FMT application. Might this also lead to new performance in more general applications? Where might it take us?

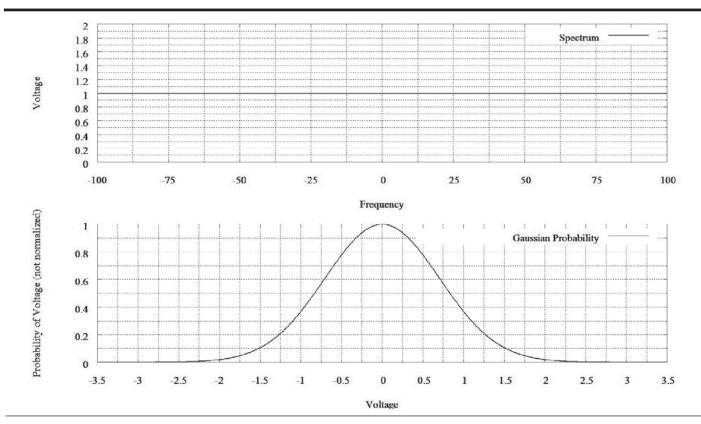

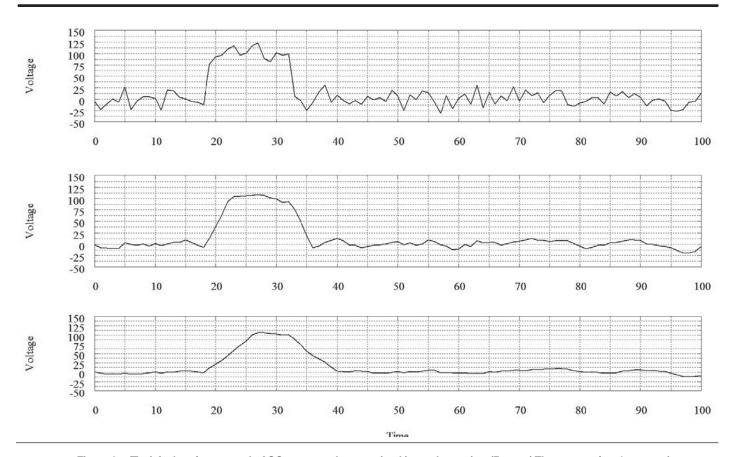

Ray Mack, W5IFS, continues to lead us through some DSP topics in our study of software defined radio concepts. In this issue we learn more about noise analysis and adaptive filtering DSP techniques. I know I have been learning a lot from Ray's tutorials, and gaining a better understanding of many topics I've read about but never quite "gotten" over the years. It is fun to learn about new technology.

In the earliest days of radio, amateur experimenters probably felt this same sense of pride in extending the body of knowledge for future generations. They were discovering new ways to make use of this new thing called radio. Those must have been exciting times to be an Amateur Radio operator!

One of the things that strikes me about those early experimenters is that they couldn't just go to the local parts emporium (or on-line store) and order the capacitors, tubes, transformers and other parts they needed. Often they had to build these elements from materials found in a literal junk heap or salvaged from some equipment that was no longer useful. I am in awe of the You Tube videos I've seen of some amateur experimenter building a power tube in his home workshop or crafting a fine Morse paddle from a block of brass or other metal. I could not do it, but some of these expert machinists, with fairly sophisticated workshops, produce some fine equipment. But in those early days of radio, the amateur experimenters were building tubes, capacitors, transformers and more with rather crude workshops and no step by step instructions! What they accomplished is truly amazing.

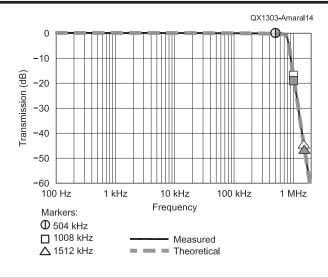

The construction of components went well beyond just the joy of crafting your own parts. Then it was absolute necessity, because suitable parts were not commercially available. In this issue we have an article by Luiz Amaral, PY1LL/AC2BR. Luiz has been experimenting on the 500 kHz band, and had to build his own transmitter. When he realized he needed an output filter for his transmitter he built the capacitors and inductors needed for the filter. (See his article in the Jan/Feb 2012 issue of QEX for a description of his home made capacitors.)

With the prospect of a new Amateur Radio allocation in the 475 kHz region (See "It Seems to Us," Feb 2013 QST by Dave Sumner, K1ZZ), more of us may be taking an interest in this region of the spectrum. While an official allocation in that frequency range probably means commercial equipment will become available, we may find ourselves experimenting with home built components of necessity again, at least for a while. Have fun!

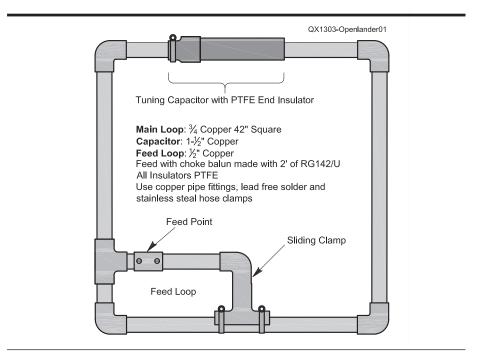

# A Two Turn Magnetic Loop Antenna for 30 through 10 Meters

The journey to success with this antenna included several interesting detours.

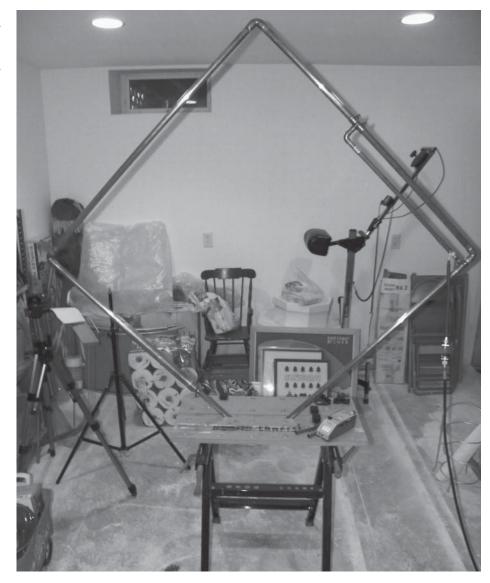

I've been working on the construction of an efficient small magnetic loop antenna for Amateur Radio on 20 meters. This is the story of what I did, not a construction project.

My home is in a restricted area and I cannot have a highly visible antenna, nor run much power without inviting problems from my neighbors and the homeowners association.

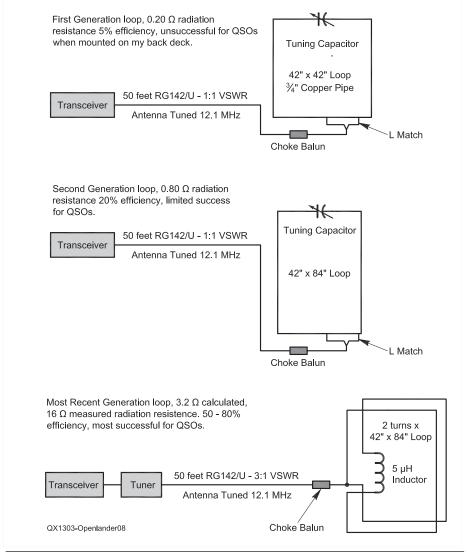

I started with a  $42 \times 42$  inch square loop using \(^3\)4 inch ID copper pipe with an L match and a trombone tuning capacitor following a design published by John Portune, W6NBC.1,2

I then spent a number of hours operating the loop in my basement lab at low transmitter power levels. Using an established measurement criterion – comparing the calculated Q from the radiation resistance<sup>3a and 3b</sup> and loop inductance<sup>4</sup> to the measured O — I calculated an overall efficiency of 5%.

I looked for power-sucking hot spots with an infrared thermometer. Operating at 25 W input, both the tuning capacitor and the choke balun became warm. I had made the capacitor insulator from Delrin and this was getting hot. I replaced all the Delrin insulators with Teflon insulators and then replaced the RG58 coax in the choke balun with RG142/u. This cooled down the hot spots but with no appreciable improvement in efficiency.

#### **Tests and Tweaks**

I put the loop outside on my deck. Using the concept of reciprocity<sup>5</sup> and averaging several days of WSPR operation (a digital mode used to study HF propagation), my observations appeared to confirm the 5% efficiency estimate.

Given the remarkably low efficiency of the loop and, aside from WSPR, my inabil-

<sup>1</sup>Notes appear on page 6.

Figure 1 - John Portune's 20 meter loop.

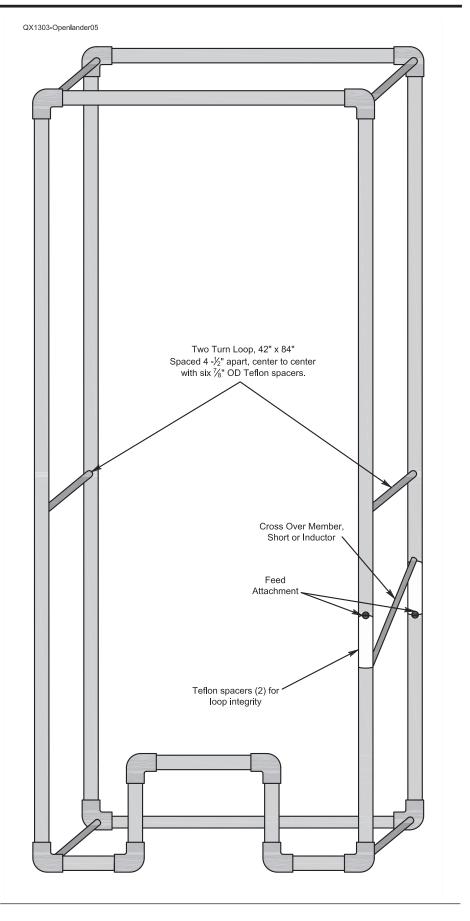

ity to make any contacts with it, I rebuilt the loop to  $42 \times 84$  inches. According to the formula for small loop radiation resistance<sup>6</sup> this doubling of area increases the radiation resistance by a factor of four.

Testing the antenna with an antenna analyzer and recalculating the efficiency by the same method as before gave me an overall efficiency of 20%.

I again used the WSPR network to confirm the efficiency, but with less rigor than before. I was also able to make a number of contacts on 20 meters using the JT65 HF mode.

It's a judgment call. I felt that the 42  $\times$ 84-inch footprint of this loop was as big as my neighbors would ignore. My next step was to add a second turn to the existing loop

with the hope of a practical 80% efficiency. The formula for loop radiation resistance predicts that this doubling in area would further quadruple the radiation resistance.

I used Teflon spacers to separate the turns 8 inches center to center and kept the tuning capacitor and L match from the original W6NBC design.

Nothing worked as expected. No matter how much I worked with the tuning capacitor, the matching network or turn to turn spacing I could not get the antenna to resonate. My observations suggested that the loop antenna impedance had become capacitive at 14.1 MHz.

Thinking that using a closer spacing between turns would return the loop to an inductive reactance, I closed the spacing to 4¾ inches between turns. A chart in one of my references<sup>7</sup> cautions that too close a spacing increases the antennas skin resistance. A good rule of thumb is a minimum spacing of a 3X the wire diameter. My 4¾ inch spacing comfortably exceeds this limit.

Unable to resonate the loop with a series capacitor, I then tried several schemes to tune the antenna with an antenna tuner. I installed a tuner at the antenna to reduce the VSWR on my feed line to 1:1. I experimented with various balun arrangements. Nothing gave me satisfactory results.

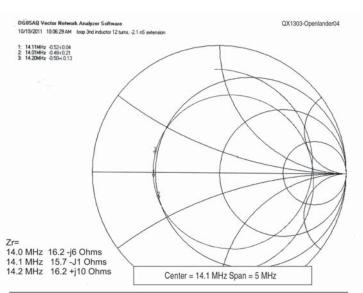

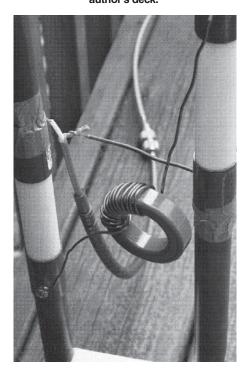

Then, in frustration, I borrowed a Vector Network Analyzer from another lab. After a quick sweep the answer was obvious - the loop had a natural resonance at 21 MHz and below that frequency was capacitive at 14 MHz, not the inductance I had expected. After a little trial and error I resonated the antenna with a 5 µH inductor.

At 14.1 MHz resonance the antenna impedance measures 16  $\Omega$ . On a Q meter the 5 µH inductor measures a resistance of about  $1 \Omega$ . A 3:1 VSWR presents no difficulty for a transmission line and antenna tuner.

The operation of the antenna on 20 meters was now entirely satisfactory as evidenced by several sequential contacts with European stations using JT65, and as with WSPR, the S/N ratio was consistent with 50% efficiency.

The antenna then tested well on 15 meters with the tuning inductor replaced by a short circuit, and also on 30 and 17 meters relying on an external tuner near the antenna.

#### **Surprises**

This has been a long journey with a number of surprises.

Figure 2 – The 42 × 42 inch loop under test in the author's basement.

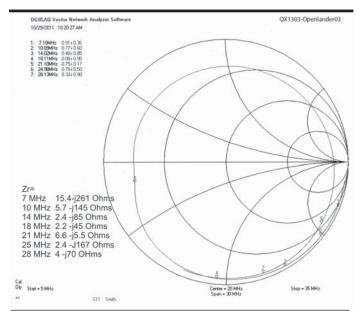

Figure 3 – A frequency sweep of the two turn loop from 5 to 35 MHz.

Figure 4 – Antenna Impedance at 14 MHz after added Inductance.

The first surprise was that basing the efficiency of small loop antennas on the ratio of skin resistance to radiation resistance proved grossly in error. I invested endless hours in an effort to find sources of loss by looking for hot spots. After eliminating the insulator and the balun I was stumped.

Antenna engineers recognize that, because there are practical limits on the O of the antenna's impedance matching network, very low radiation resistances will be accompanied by high matching network losses. The degree of loss is a surprise.

The second surprise is that adding a second turn to the antenna changed the antenna's impedance behavior from an inductive loop to a dipole below resonance. It was no longer a magnetic loop, but something like a 15 meter dipole. The small loop formulas no longer applied.

My thinking here is that the inter-turn capacitance exceeds the loop inductance. My evidence for this is that when I reduced the inter-turn spacing from 6 inches to 43/4 inches the self resonant frequency dropped from about 25 MHz, as measured with an antenna analyzer, to 21 MHz as measured with the VNA.

The third surprise is the increase in radiation impedance when the antenna was resonated. It is possible that there are errors in my VNA measurements. I tend to distrust impedances near the edge of the Smith chart. The angles are usually accurate but the magnitudes can be in error. This might explain some of the difference in radiation resistance between the matched and unmatched loops.

A fourth surprise is that a careful search of the antenna literature found very little information about rectangular, asymmetrically fed, multi-turn transmitting loops.

#### Improvements?

There is considerable room for future improvement and experimentation. If one is willing to accept the moderate VSWRs, around 3 or 4 to 1, band switching is very simple – little more than a matter of changing matching coils. A simple relay board would do this.

If one is limited to low power operation it is possible to tolerate even higher VSWR on the feed line. My initial experiments suggest that with the 20-meter tuning inductor replaced by a short circuit, and an antenna tuner in the shack, efficient operation is practical on all the bands from 30 through 10 meters.

Finally there are many still unanswered questions. The bottom of the antenna is only about four feet off the ground. What happens if the antenna elevation is raised?

What about adding more turns. If two turns is efficient on 20 meters, would 4 turns be similarly efficient on 40 meters?

Figure 5 – A diagram of the 42  $\times$  84-inch version of the loop.

Figure 6 - The two turn loop mounted on the author's deck.

Figure 7 - A balun feed and 5 µH inductor tunes the loop for 20 meters. Replacing the balun with a metal strap resonates the loop at 21 MHz.

#### **Notes**

Portune, John, W6NBC, "Compact 40 Meter HF Loop for Your Recreational Vehicle," QST, March 2007, pp 41-43.

<sup>2</sup>Portune, John, W6NBC, "Compact HF Loops for Your RV," www.w6nbc.com/hfrvloop. html, January 3, 2009.

<sup>3a</sup>Newman, Edward et al, "Two Methods for the Measurements of Antenna Efficiency,' IEEE Transactions on Antennas and Propagation, July 1975, pp 457-461.

3bBelrose, John S., "Performance Analysis of

Small Tuned Transmitting Loop Antennas Evaluated by Experiment and Simulation, IEEE Antennas and Propagation Magazine, June 2007, pp 128- 132,

<sup>4</sup>Air Core Inductor Inductance Calculator, www.daycounter.com/Calculators/

AirCoreInductorCalculator.phtml 5Reciprocity: The idea here is that the path conditions between two stations are identical in both directions and, as a consequence, signal strengths measured at both sites will be in linear proportion to their transmitter power. In actuality, because of the volatility of skip conditions this path symmetry is rarely a true case at any individual moment in time. However, if measurements

are averaged over a large enough number of samples, the rule holds. That is, if 50 W to the antenna yields an average S/N ratio report consistent with 2.5 W radiated power, the antenna efficiency is 5%.

<sup>6</sup>Reference formula for radiation resistance from Krauss, John D., Antennas, McGraw Hill Book Company, New York, 1950, pp 167. Radiation resistance is given by the formula:  $R = 31171 \times Number of Turns^2 \times (Area^2 / Part of Turns^2)$ Wavelength4)

At 14.1 MHz 42  $\times$  42 inches = 0.20  $\Omega$ 42  $\times$  84 inches = 0.80  $\Omega$ 2 turns  $\times$  42  $\times$  84 inches = 3.2  $\Omega$ <sup>7</sup>Balanis, Constantine A, *Antenna Theory,*

and Sons, New York, 1997, pp 211.

Engineering at Antenex, Inc.

ARRL member Wayne Openlander, Amateur Extra class W9NZB, holds five antenna and two instrument patents. He recently retired as Vice President of Resonance Instrument, Inc, a custom manufacturer of microwave instrumentation. Previously he was Vice President of

Analysis and Design, 2nd ed., John Wiley

Figure 8 – System block diagrams at various stages of development.

## Fun with Voltage-to-Frequency Converters

### These converters have many applications. Consider using one in a project.

A voltage-to-frequency (VFC) converter is a type of voltage controlled oscillator. It is often only useful at lower frequencies and may have a narrow pulse output instead of a nice sine wave or square wave. I used them in many applications over the years. I will describe several to give you an idea of how you may use them to benefit your own projects.

Many of these examples render signal measurements into audible signals that the user hears. This allows the user to perform other tasks that may require visual attention such as making precision adjustments while listening to the relative results of those adjustments. This method offers resolution better than that available from the close examination of an analog meter because the human ear is very sensitive to small changes in frequency or pitch.

#### **Remote Photocurrent Measurement**

The application was to measure the photocurrent of a photodiode at a remote receiver in a free-space laser communication link circa 1978. I steered the laser telescope at the transmitter telescope and used the photocurrent measurement to optimize pointing. A trans-impedance amplifier turned the photocurrent from the receiver into a voltage to control the frequency of VFC that in turn drove a loudspeaker transducer from an old acoustic modem in a rubber cup (remember those?) that attached to the microphone of a telephone handset. I controlled the frequency range to vary between 300 Hz and 3000 Hz to accommodate the telephone system. A telephone link carried the audio from the receiver back to me at the laser transmitter so I could optimize link performance by maximizing the audio frequency and thereby the received optical signal level. It was a

simple and effective solution to my problem.

The ICL80381 is the first chip I used as a VFC. Intersil called it a Precision Waveform Generator and Voltage Controlled Oscillator. The ICL8038 worked up to 300 kHz and had the decided advantage of simultaneous sinusoidal, square and triangle outputs. That made it more of a function generator chip than a VFC, but it's the first one I used. It is obsolete now and frequency control by a voltage was not straightforward, so I recommend against using it and provide no schematic diagram.

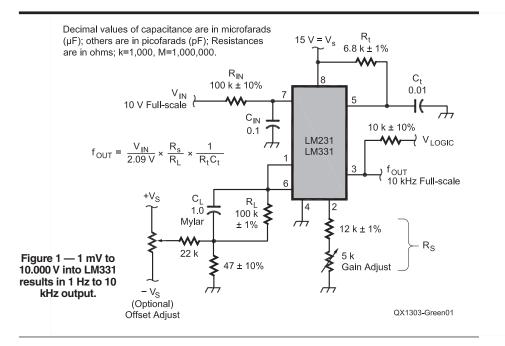

Better choices today are the National LM331<sup>2</sup> and the Analog Devices ADVFC32.<sup>3</sup>

<sup>1</sup>Notes appear on page 10.

These are both much simpler to interface and very linear. I prefer the LM331 because it is in an 8 pin DIP package and works with a single supply voltage from 4-40 Vdc while the ADVFC is in a 14 pin DIP and calls for symmetrical ±15 Vdc supplies. Analog Devices also makes the AD7741, which is in an 8 pin DIP and takes a single +5 Vdc supply, but I have no experience with it.

All of these are super linear, at least to the degree that you can read an input voltage by displaying the output frequency on a frequency counter if you scale the input voltage range and output frequency range accordingly. Figure 1 is an example from the LM331 data sheet that shows the setup and suitable component values.

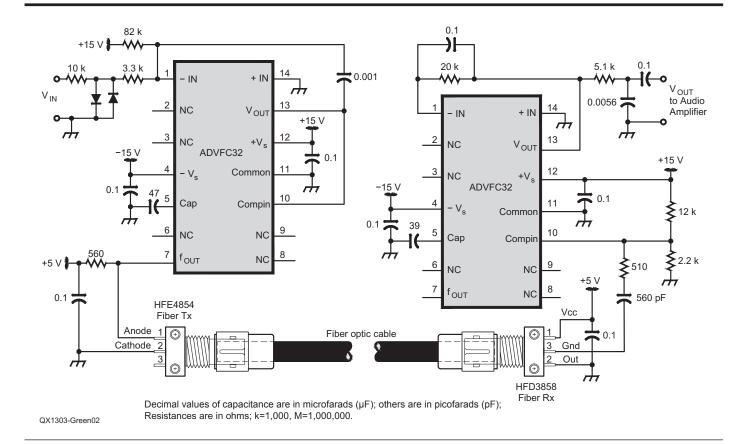

#### **Audio Link**

The ADVFC32 and LM331 data sheets show they are also able to serve as frequencyto-voltage converters. Figure 2 shows a fiber optic link I built in which an audio voltage modulates the frequency of a first ADVFC32 that in turn modulates light pulses into an optical fiber. A second ADVFC32 accepts pulses from the optical receiver to regenerate the original audio waveform. Think of this as an exercise in optical isolation. The input limiter helps maintain FM transmitter deviation in a desired range.

#### The BERT Trick

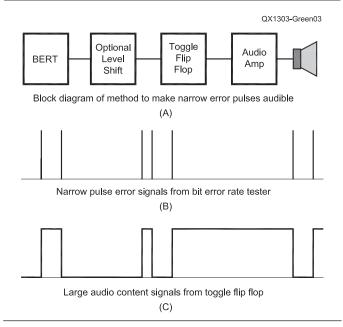

Both the LM331 and the ADVFC32 output narrow pulses. There is little audio energy in low duty cycle pulses, so the waveform is unsuitable for listening. There isn't much to hear. I had the same problem with bit-errorrate testers. These instruments monitor the performance of serial digital communication links and output a narrow one bit wide pulse each time an error occurs. At 1 Gbps that pulse lasts only 1 ns. Most people lock their eyes on the error counter display to determine error rate or when errors occur. It's

pretty hard to make useful adjustments while you monitor the display. Instead, I chose to listen to the errors. Simply feeding the error pulses to a toggle flip-flop yields a high duty cycle waveform with lots of audible energy4 as in Figure 3. The same trick works with these VFCs. A toggle flip-flop divides the frequency by two and converts the pulse train to a 50% duty cycle square wave.

Alternately, a Don Lancaster trick divides the frequency by 10 and synthesizes a decent sounding sine wave.<sup>5</sup> All audible solutions below use one of these frequency divider tricks to convert a train of narrow pulses into audible waveforms.

#### **Another Photocurrent Measurement**

The next project was another photocurrent measurement. This one utilized the sensitivity of the human ear to sense very small changes in pitch. I sent a fixed amount of unmodulated light into an optical fiber and used this instrument to indicate how much light came out the other end. The relative measurement was so sensitive that bending the fiber caused a noticeable decrease in the audible frequency due to the light lost in the bend. I intended this as a way to monitor fiber bending and strain when fiber is pulled during installation, where it often breaks. This method indicated a dramatic decrease in audible frequency before the fiber would break and so give the installer a chance to back off and try something else.

I patented this method.<sup>6</sup> My company sold it to another party who subsequently paid the maintenance fee that will keep this patent in force until 2015.

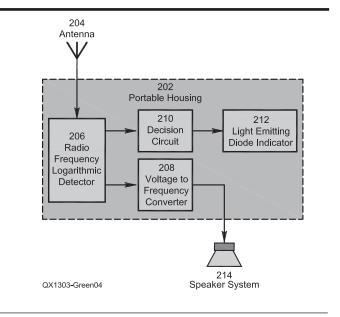

#### Radio Frequency Signal Strength Measurement

I designed and built a field strength meter that indicates higher power as a higher audio frequency pitch. The circuit is simply an Analog Devices AD83077 log-detector with 500 MHz response driving an LM331 VFC and toggle flip-flop. The output voltage of the log detector represents the logarithm of the RF signal input strength, compressing a wide dynamic range input into a couple volts of output swing. Applying that voltage to control the frequency of an oscillator in the audio range provides a simple and effective way to communicate the signal value to your ear. I constrained the audio frequency range to between 300 - 3000 Hz to match telephone

Figure 2 — The fiber optic link uses ADVFC32s to transmit and receive audio.

line and FM transceiver capabilities.

The human ear easily differentiates very small frequency changes, allowing very high resolution and high sensitivity to small changes. Sensitivity to amplitude changes is very much poorer, as the human ear is able to resolve variations of about 1 decibel which corresponds to about -20% or +25%.

I meant this to be an instrument for the amateur radio community to make remote measurements of relative field strength. I thought it would prove useful to measure radiated signal level at some distance from the transmitting source, perhaps for antenna comparisons or to see if an antenna tuner adjustment is real and not a phantom dip in VSWR. In the shack, you would read the meter of an ordinary instrument, but remote operation requires a way to return the measurement data to the user while making adjustments that affect the remote reading. Conversion of the field strength reading to a varying audio frequency signal allows return of the measurement data via a phone line or an audio modulated FM radio link. Rotate an antenna and listen to measure the effect in the far field.

I walked around my workplace with the prototype and listened to different sources of RF. When I heard the data exchange as the RF reader interrogated my employee badge, I got the idea that this could become a cell phone and wireless detector. That might prove useful to sense such devices operating where they shouldn't. I built up another prototype based on an AD8313 log detector with 2500 MHz response to sense cell phones and

wireless. With it I could tell which laptop had its wireless enabled when I walked up and down the aisle on a commercial airline flight with headphones connecting to the unit in my pocket.

Because airlines want RF emitters turned off, and because I worked for an airplane company that offers incentives for intellectual property, I patented this method as well.8 Again, you can look at the details in the patent online.

This is what I built into the two Altoids tins in the article "Hints & Kinks: Altoids Times Two" that appeared in *QST* and the ARRL Letter. Figure 4 is an excerpt from the patent. The decision circuit and light emitting diode indicator never existed and were an "attempt at completeness" by a patent attorney whom I will be glad never to work with again.

Company attorneys discouraged me from publishing actual schematic diagrams, but this is fairly simple to understand from the discussion. My hope is someone will notice this and license it for manufacture and sale. I wouldn't benefit, but I am grateful for the benefits already received during my years of employment.

For extending the AD8307 logarithmic detector to work at low frequencies, refer to my QEX article "Fully Automated DDS Sweep Generator Measurement System". 10

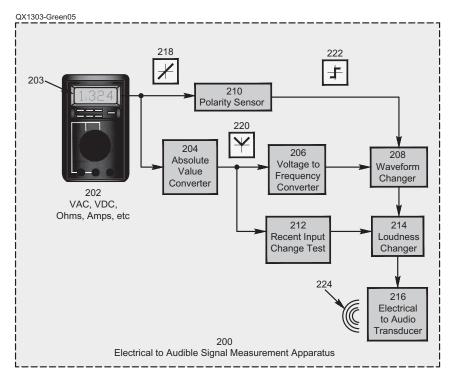

#### **Digital Multimeter Accessory**

This last project is a fairly recent attempt to overcome the worst problem of digital multimeters (DMM), the lack of a decent analog indication. Digital meters offer precision, resolution and accuracy that old moving needle analog meters never could. Analog meters did excel at indicating relative increases and decreases in magnitude.

Some DMMs add a crude bar graph display to indicate relative magnitude, but these are worthless except for large variations. No one would use such a display for any fine adjustment.

The use of a VFC in this application offers resolution that exceeds the resolution available from the moving needle of an analog meter. This is an obvious improvement, yet no vendor offers such a capability. Adding this to a DMM gives precise analog information that enables a user to perform adjustments that maximize or minimize any measurable parameter without even having to look at the DMM!

I set out to build an accessory for a DMM to demonstrate the concept. The nice thing about a DMM is that it performs all the scaling by converting all possible input signals, whether current, voltage, resistance, or any of a number of other parameters, to the range of the internal digital meter. This was ±200 mV for my demonstration unit. I added a gain of 10 before the VFC input to accommodate a 200 mV input range.

At this point, there is no advancement to the state of the art, and anyone can reproduce

Then I added three improvements that I thought would be desirable in a DMM.

1. I added an absolute value circuit, so that the VFC receives only positive going signals from the input.

Figure 3 — A method to make narrow pulses audible.

Figure 4 — A method and apparatus for detecting radio frequency signals.

- 2. I sensed when the input is negative and used this signal to change the way the audio sounds when the input goes negative to be able to tell the difference when listening. I tried switching between different waveforms such as sine waves and square waves and then settled on tremolo. When the input signal goes negative, a low frequency oscillator interrupts the voltage indicating waveform. This was very effective and much simpler to implement.

- 3. At the suggestion of my co-inventor, I added a squelch circuit to turn off the output when it wasn't changing. This turned out to be difficult to implement, but it makes for much less annoying operation.

We applied for patent protection on these key features. Figure 5 from the pending patent application<sup>11</sup> provides a general description.

#### Online Patent Information

Note that you need a TIFF viewer plug-in for your Internet browser to view the actual images of a patent or patent application on the USPTO website. The USPTO recommends several free TIFF viewers.<sup>12</sup> Of these, I have the best results with AlternaTIFF.<sup>13</sup> Without a TIFF viewer you can only read the text of a patent or patent application.

The message buried in this article is that you can search and read patents online. The USPTO site and the TIFF viewer are free. A huge amount of information resides on the site.

Eighteen months after the USPTO receives a patent application, they publish it on their website, whether or not they ever grant patent protection, and usually while the application is still pending. Did you know that? That's the deal you make to get patent protection. You explain and make obvious how your invention works, the USPTO makes it public and then they may or may not award patent protection. The adjective "patent" means readily visible, intelligible, or obvious. At that point, the information becomes public. If the USPTO agrees that the invention is sufficiently unique, they grant patent protection and you or your company gain exclusive rights for a number of years, while you pay increasingly larger fees to renew it.

So when you research a field of technology, consider looking among applications as well as patents. You can search on the names of known inventors, companies and areas of technology and look into what your competitors are doing. See the next great thing.

The USPTO also has a site called PAIR for Patent Application Information Retrieval that tells the licensing status of each patent and application and whether patent

Figure 5 — An audio frequency device for audible eyes-off measurements.

protection is expired for non-payment of fees.<sup>14</sup> PAIR even shows the correspondence between the patent examiner and the applicant's patent attorneys. It is all public information.

#### In Conclusion

Consider the utility of VFCs in your projects. You can send analog signals over a digital link, and you can listen to signals as they change. Enjoy!

Dr Sam Green, WØPCE, is a retired aerospace engineer. Sam lives in Saint Louis, Missouri. He holds degrees in Electronic Engineering from Northwestern University and the University of Illinois at Urbana. Sam specialized in free space and fiber optical data communications and photonics. Sam became KN9KEQ and K9KEQ in 1957, while a high school freshman in Skokie, Illinois, where he was a Skokie Six Meter Indian. Sam held a Technician class license for 36 years before finally upgrading to Amateur Extra Class in 1993. He is a member of ARRL, a member of the Boeing Employees Amateur Radio Society (BEARS), a member of the Saint Louis QRP Society, and breakfasts with the Saint Louis Area Microwave Society. Sam is a Registered Professional Engineer in Missouri and a life senior member of IEEE. Sam holds sixteen patents, with two more patent applications pending. Contact Sam at w0pce@arrl.net.

#### Notes

www.intersil.com/data/fn/fn2864.pdf 2www.national.com/ds/LM/LM231.pdf 3www.analog.com/static/imported-files/ data sheets/ADVFC32.pdf

<sup>4</sup>"Bit error rate test accessory makes errors audible", Samuel Green, Rev. Sci. Instrum. 72(12) 4472 (01 Dec 2001).

<sup>5</sup>TV Typewriter Cookbook, Don Lancaster, ISBN 0-672-21313-3, pp 180-181, (Jan

6http://patft.uspto.gov/netacgi/nph-Parser ?Sect1=PTO1&Sect2=HITOFF&d=PALL& p=1&u=%2Fnetahtml%2FPTO%2Fsrchnum.htm&r=1&f=G&l=50&s1=5729335. PN.&OS=PN/5729335&RS=PN/5729335 7www.analog.com/en/specialty-amplifiers/

log-ampsdetectors/products/index.html 8http://patft.uspto.gov/netacgi/nph-Parser ?Sect1=PTO1&Sect2=HITOFF&d=PALL& p=1&u=%2Fnetahtml%2FPTO%2Fsrchnum.htm&r=1&f=G&l=50&s1=7898395. PN.&OS=PN/7898395&RS=PN/7898395 9http://www.arrl.org/arrlletter?issue=2009-

10-15 <sup>10</sup>Fully Automated DDS Sweep Generator

Measurement System, QEX, Nov/Dec 2008, 11http://appft.uspto.gov/netacgi/nph-Par

ser?Sect1=PTO1&Sect2=HITOFF&d =PG01&p=1&u=%2Fnetahtml%2FP TO%2Fsrchnum.html&r=1&f=G&l=5 0&s1=%2220100079131%22.PGNR.&OS= DN/20100079131&RS=DN/20100079131 12www.uspto.gov/faq/plugins/tiff.jsp 13www.alternatiff.com/

14http://portal.uspto.gov/external/portal/ pair

QEX-

## A Precision DDS for the Frequency Measurement Tests

K6IQL describes how to create a DDS with laboratory quality performance.

The Frequency Measurement Test (FMT) is held several times a year and it provides an opportunity to test our skills at determining the actual frequency transmitted by each of several test stations. These events are great fun with friendly, but stiff, competition to determine which operator has best mastered this technically challenging activity. I have participated in several of these events and had a lot of fun. Acceptable results were achieved using surplus laboratory quality synthesizers as RF frequency references. However, not all operators have access to lab-quality synthesizers.

After some personal pontification on various Internet forums pointing out that the "resolution" limitation inherent in Direct Digital Synthesizers (DDS) may compromise their use for Frequency Measurement Tests (FMT), the mental light bulb went on. I realized that perhaps I was dead wrong; no surprise there, it has happened before. Perhaps a DDS could provide an acceptable alternative to more costly equipment?

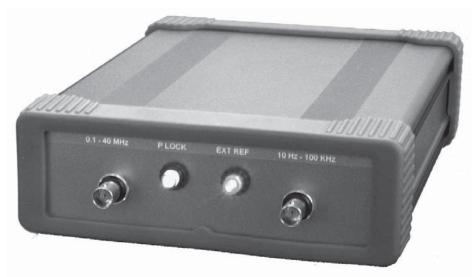

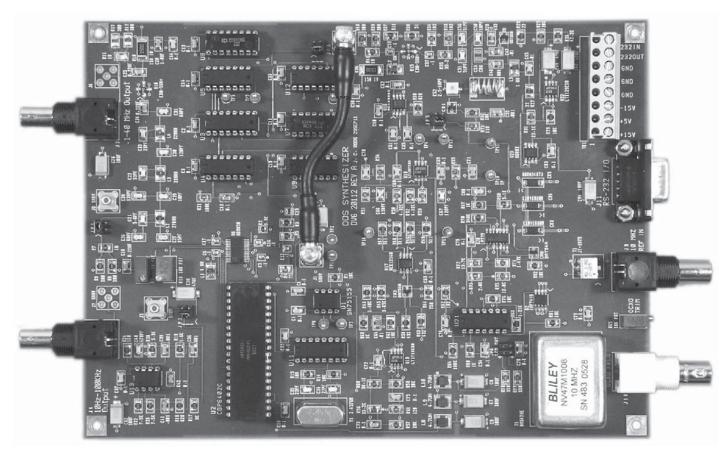

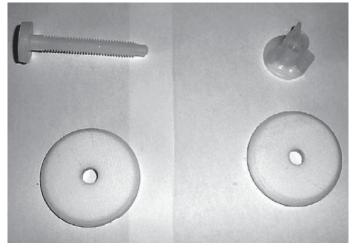

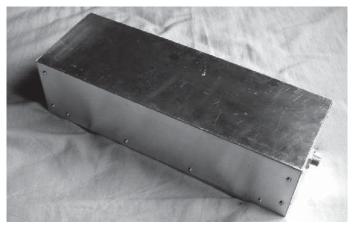

So, this project started as a simple experimental breadboard to determine if some of the difficulties inherent in using a DDS as part of a FMT measurement set up could be overcome. Like many such projects it grew in both scope and complexity, resulting in the design presented here. By the time I finished with the enhancements I had a useful PC-controlled laboratory source capable of generating highly accurate frequencies from 10 Hz to 40 MHz. The final result (see Figure 1) is a bit different from many of the DDS and Phase Locked Loop (PLL) synthesized frequency generator projects intended for amateur use. Most are aimed at applications such as a receiver Local Oscillator

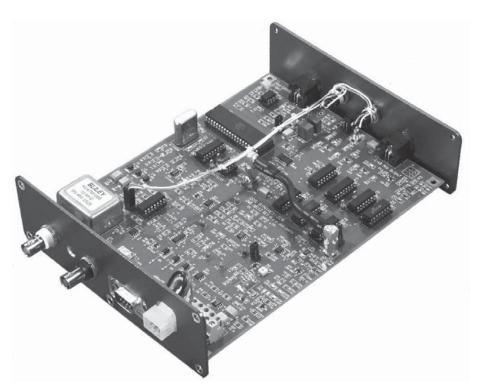

Figure 1 — The Direct Digital Synthesizer is packaged in extruded aluminum housing. Front panel BNC connectors are provided for the 10 Hz to 100 kHz and the 100 kHz to 40 MHz output. LED lamps indicate lock status of the reference PLL and the presence of an external 10 MHz reference input.

(LO) or transmitter Variable Frequency Oscillator (VFO). A number of clever and innovative circuits have been developed in recent years.1 Usually these designs incorporate an onboard processor, controls and displays for the interface between the operator and the synthesizer. The control interface typically limits the frequency "setability" to 1 to 10 Hz, which is more than adequate for their intended use.

Due to the DDS "resolution" issue and lack of readout resolution of less than 1 Hz, the indicated frequency may not be the actual output frequency. That is one limitation that

<sup>1</sup>Notes appear on page 34.

must be overcome for the FMT application. Additionally, the reference oscillators, while often very good, are not adequate for precision frequency measurements.

In approaching this project I wanted the synthesizer to do three things:

- 1. Operate from a very good internal clock, or an external GPS, Rubidium (Rb), or metrology lab quality quartz 10 MHz frequency standard.

- 2. Accept serial data control signals from any PC or processor and associated program capable of sending and receiving 5 bytes at 9600 bits per second. That allows the PC software designer to freely define the functionality and user interfaces.

The DDS would be implemented completely in hardware. It would be capable of executing any function supported by the DDS chip subject only to the limitations of the serial data rate. By hosting the controlling software in a PC, programs could be written in any high-level language to implement the desired test functions. Examples include frequency stepping, sweeping, or sequencing through a defined set of test frequencies.

3. Accurately report, to millihertz (mHz) accuracy, the actual output frequency generated by the DDS, which as we shall see, is not necessarily the frequency, the operator requests.

Before getting into the details of the actual design, it is useful to briefly review the Frequency Measurement Tests and some methods of accurately measuring the frequency of a HF signal. Then I will, somewhat whimsically, discuss the math behind the DDS resolution issues and the calculations required both to program a DDS and to determine the actual output frequency.

#### **The Frequency Measurement Tests**

Frequency Measurement Tests are conducted several times during the year. In April and November the ARRL publicizes and coordinates the tests.2 In addition, an FMT interest group, FMT-nuts, is hosted on Yahoo. This group provided the test signals used in the recent ARRL FMTs. It

also conducts a number of additional FMTs throughout the year. Connie Marshall, K5CM, coordinates the activity. Signals have been provided by K5CM, W6OQI, W8KSE, WA6ZTY and others.

For additional information visit the ARRL FMT website, and Connie's website, **K5CM.com.**<sup>3</sup> Here you'll find a wealth of information on past test results, future tests, and links to other sites describing test methods and techniques. The FMT-nuts group is very active with daily e-mail exchanges on techniques and equipment. There is a link to join the group at **K5CM.com**. If these topics are of interest, there is a lot of information on frequency standards, measurement techniques and other technical issues.

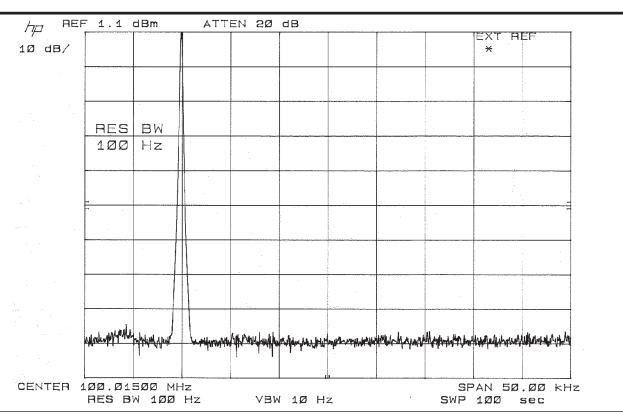

The test stations provide highly accurate signals, generally traceable to the National Institute of Standards and Technology (NIST) via GPS or WWVB. Test signals are transmitted near previously announced frequencies and are accurate to at least 0.001 Hz or 1 millihertz (mHz). This degree of accuracy is required because participating stations have gotten quite good at measuring frequency. For example, in an FMT conducted on 11 September 2011, 12 stations posted an average frequency error between 1.15 and 7.75 parts in 108. In the ARRL FMT conducted in April 2011, five stations posted average errors between 2.15 and 2.86 parts in 108. An error of 1 part in 108 is an error of only 70 mHz at 7 MHz!

From this the question arises, "How much measurement accuracy is needed?" The averages quoted above are one measure of performance and useful to determine overall performance. A detailed look at the results for each test frequency will often show results of 1 part in 10<sup>9</sup> or even better. Due to Doppler shifting of the frequency by movement of the ionosphere, a given station may have an error of only a few mHz on one test frequency and yet do poorly on another. So a good overall average may still be achieved provided there are enough good measurements to compensate for a bad one. Since it has been shown a number of times that measurement errors of less than 10 mHz are seen frequently, a system error (exclusive of ionospheric effects) of about +/- 1 mHz is in the right ballpark.

While FMTs have probably been conducted on most of the bands at one time or another, the HF tests are typically on 160, 80, 40 and occasionally 20 meters. Taking 40 meters as the typical worst case; the accuracy required of the station is simply:

Required Accuracy = 7 MHz / 0.001 Hz = 7,000,000 / 0.001 = 7 parts in  $10^9$

While this is a formidable number, the recent availability of surplus GPS-disciplined oscillators and rubidium frequency standards

Figure 2 — The Audio Beat Method of measuring the frequency of a HF signal. All measurements are referenced to a 10 MHz Rb, GPS, or quartz frequency standard. Using this approach the stability of the receiver does not affect the measured result.

at low cost provide access to the accuracy required. Given a good frequency standard, the challenge then becomes to implement an accurate measurement system.

#### **FMT Measurement Methods**

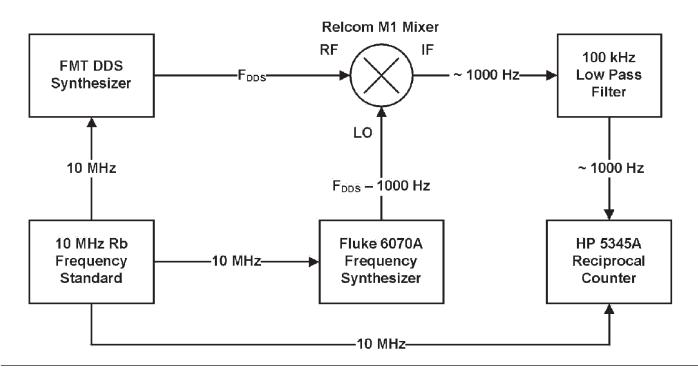

A review of the comments posted on the ARRL FMT web page4 will reveal a wide variety of techniques from a simple transceiver with a WWV-calibrated Temperature Compensated Crystal Oscillator (TCXO), to use of custom-designed receivers and software. Some operators, including myself, use some version of the "audio beat method" shown in Figure 2.

In this scheme, which is almost as old as radio, we have an HF receiver that receives the unknown frequency. The receiver is operated in the AM mode (the Beat Frequency Oscillator (BFO) is definitely off). An RF reference generator, generally a synthesized signal source, is coupled via an attenuator into the input of the HF receiver. Accuracy of the RF reference is determined by a local frequency standard. The frequency of the RF reference is adjusted to produce an audio beat note in the receiver. A frequency counter or PC running audio spectrum analysis software is used to determine the frequency of the beat note. Now, if the RF reference is set about 500 Hz below the unknown frequency, we can define:

$F_{unk}$  = Unknown frequency from the test

$F_{ref}$  = Frequency of the RF Reference Synthesizer

$$F_{\text{beat}} = F_{\text{unk}} - F_{\text{ref}}$$

By determining  $F_{\text{ref}}$  and  $F_{\text{beat}}$  the unknown frequency is simply

$$F_{unk} = F_{ref} + F_{beat}$$

[Eq 1]

An often underappreciated feature of this method is that the accuracy is determined solely by the accuracy of the RF reference and the beat frequency measurement. Stability of the receiver LO does not appear as part of the frequency calculation. As long as the receiver is stable enough to maintain the unknown and RF reference signals within the IF pass band, and has sufficient selectivity to keep out interference, it has no effect whatever upon the measurement. However, to avoid having the receiver Automatic Gain Control (AGC) suppress the desired signal, the attenuator must be adjusted so the injected reference frequency is at a level equal to or slightly below that of the incoming signal.

Nifty as this method may be, measuring the beat frequency to the required precision within the two minute FMT key-down measurement period is a challenge. In Figure 2, two methods are indicated.

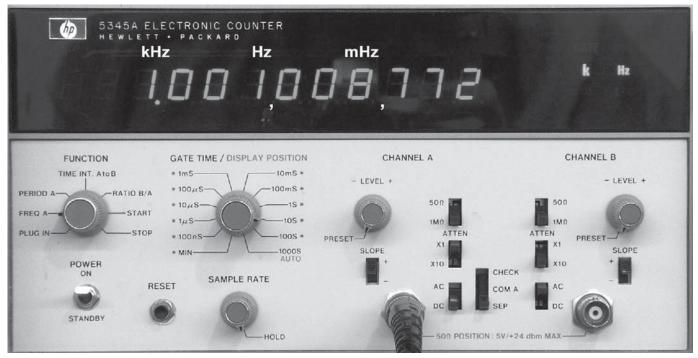

It is possible to use a frequency counter, as shown, but not of the conventional type. In a conventional counter, the resolution is determined by the gate time of the counter. A one-second gate time yields a +/-1 Hz resolution. This is hardly adequate for our purposes. Even if the gate time were extended to the entire key down period, 120 seconds, the resolution is only +/- 0.083 Hz. This is not too practical due to loss of counts during fades, false triggers and other problems. A "reciprocal" counter should be used. Reciprocal Counters<sup>5</sup> count a very high-speed internal clock that is gated by the input signal and counted. It then computes the frequency. At audio frequencies a reciprocal counter can produce very high-resolution measurements with short gate times. These devices easily achieve 1 mHz accuracy at 500-1000 Hz with only a 1 second gate time. Multiple measurements may be collected during the two minute key down period. These measurements may be averaged to obtain a better solution.

However, as explained in the referenced papers, all counters suffer triggering errors under poor Signal to Noise Ratio (SNR) conditions. A better solution is to use a PC that employs an audio spectrum analysis program in conjunction with the PC sound card. The sound card acts as a very high dynamic range A/D converter. One very capable program used for FMTs is Spectrum Lab,6 authored by Wolfgang Buscher, DL4YHC. It is available on the Internet as a free download.

Spectrum analysis software employs the Fast Fourier Transform (FFT) technique to realize the equivalent of a contiguous group of very narrow bandwidth frequency bins (filters). This has many advantages:

- The bin bandwidth can be very narrow, 1 Hz or less, thus greatly improving the processing signal to noise ratio. A 90-dB dynamic range is common and signals you cannot hear are readily visible on the spectrum display.

- Some programs, including Spectrum Lab, can interpolate the frequency measurement across bins resulting in truly outstanding measurement resolution - 1 mHz or better is easily demonstrated.

- Averaging can be used, further improving both SNR and accuracy. It is possible to get 100 or more individual measurements in a 120 second key-down period.

- The measurements may be output to a text file and then to a spreadsheet for later processing, averaging, application of statistical functions or making graphs of the data.

- Some programs provide a "waterfall" as well as a conventional spectrum display. The waterfall will show real time shifts in the frequency of the unknown due to ionospheric

effects. This can be very useful in determining the unknown frequency.

• The audio beat tone may be recorded in real time and played back later using multiple passes to better optimize the processing.

A potential disadvantage is that while great precision is possible, it is the crystal in the processor that controls the sound card sample rate that determines the ultimate accuracy.

Considering the accuracy goal to be 1 mHz, this at first seems a problem, but it really is not. Just how accurate is a 1 mHz measurement at 500 to 1000 Hz? Using 1000 Hz as about the highest beat frequency one would want to employ we have:

Required Accuracy = 1000 Hz / 0.001 Hz =  $1 \times 10^6$  or 1 part per million.

As very low cost crystals are used for computer clocks, the required initial calibration accuracy is not inherent. However, some spectrum analysis software, including Spectrum Lab, have routines to calibrate out the clock frequency error. Inputting a known accurate frequency from an audio frequency calibrator such as shown in Figure 2 does this. The operator simply tells the routine what frequency is displayed and the true frequency. From this the routine computes and stores the appropriate correction.

How well does this work? Actually, surprisingly well. If the computer is warmed up for an hour or so before calibration, the issue is reduced to the thermal drift of the crystal, which is not nearly as serious as the initial accuracy error.

Using a 1000 Hz tone derived from a rubidium frequency standard I did some tests. The processor was old Compaq EVO desktop machine purchased surplus for about 100 bucks. After a 1 hour warm-up the clock was calibrated. After calibration the indicated frequency was recorded every 10 minutes. It was determined to be within +/- 0.0005 Hz of 1 kHz for 6 hours at which point I stopped the test. Repeated checks over a period of months have shown the calibration to be stored and maintained. Ensuring the computer is calibrated and used after it has reached a stable temperature is the only precaution required.

With this overview of a typical FMT measurement technique I'll now get into the innards of typical DDS chips, their limitations and how to use one to achieve accurate results.

#### DDS Operation and Programming

Without doubt the advent of the DDS in integrated circuit form has eased the life of RF engineers. I have used them in two commercial designs: a VHF/UHF ILS transmitter

synthesizer, and as the LO for a VHF/UHF ILS monitor receiver. In both instances the performance was comparable to earlier PLL designs and with considerably less complexity and headache.

However, with any technology there is no free lunch. Some of the issues that must be considered when employing a DDS include:

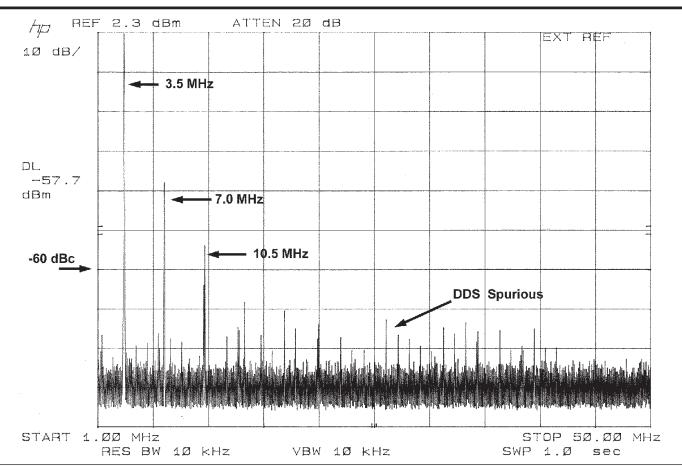

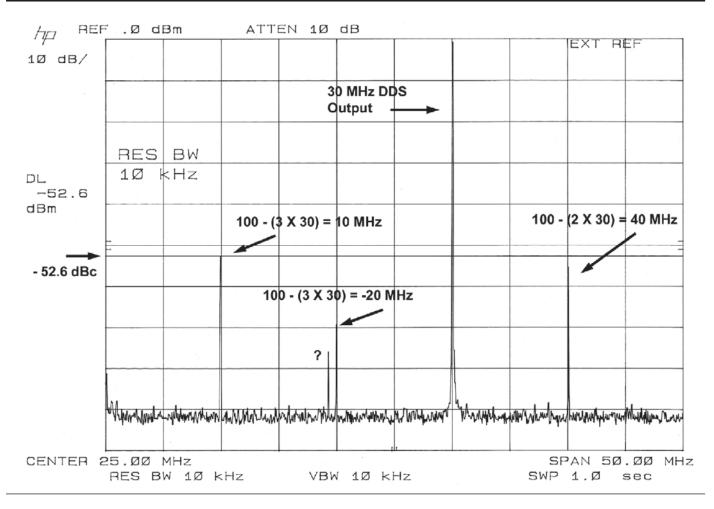

- Spurious Outputs DDSs produce spurious outputs. There are many articles<sup>7</sup> in which the spurious issues and means to mitigate spurs are treated, and since our focus is frequency measurement, please refer to the sources listed in the Notes.

- Finite Frequency Resolution In DDS speak, frequency resolution is a more polite term for frequency steps that have a predictable but varying relation to the requested frequency. As I will show, the frequency you ask for is almost never the frequency the DDS produces. Close, but not exact.

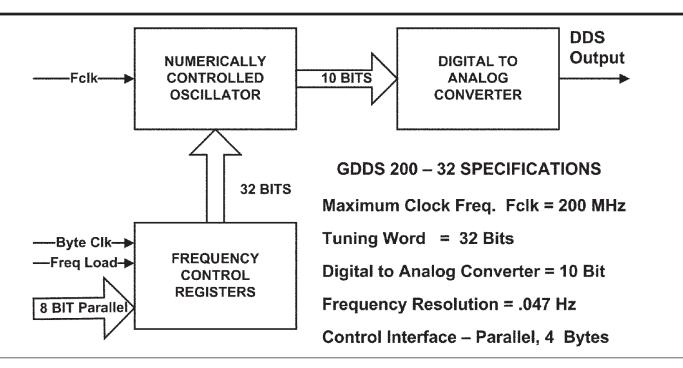

The frequency resolution issue is common to all of the simple DDS chips and at the heart of the FMT accuracy problem. To illustrate this I will define a fictional generic DDS, the GDDS 200-32, a product of Mythical Semiconductors Corp. (MSC). A block diagram and specification sheet for the MSC GDDS 200-32 is shown in Figure 3.

The first four specifications listed in the figure essentially define the overall performance of almost any simple DDS:

- Maximum clock frequency. This is obvious, but as we shall see using a lower clock frequency improves the tuning resolution.

- Width of the tuning word. This is fixed by the DDS design. The width of the tuning

word in conjunction with the actual clock frequency determines the worst case frequency error.

- Digital to Analog converter resolution. This determines the achievable spurious level. More D/A bits imply lower spur levels. The spur level will be approximately 20 x  $Log (2^N)$ , when N is the number of D/A bits.

- Frequency resolution. This is the minimum step size for a given clock frequency. It is also an indication of the worst case frequency error to be expected when the DDS is operated at a specified (normally maximum) clock frequency.

Programming and determining the actual output frequency of a DDS comes down to two versions of the same simple equation:

$$F_{\text{out}} = (T_{\text{wrd}} X F_{\text{clk}}) / 2^{N}$$

[Eq 2]

And solving for T<sub>wrd</sub> we have

$$T_{wrd} = (2^{N} X F_{out}) / F_{clk}$$

[Eq 3]

Where:

$F_{out}$  = The Output Frequency from the

$T_{wrd}$  = The Tuning Word Input to the DDS from the controlling processor

$F_{clk}$  = The DDS clock frequency derived from a frequency standard

N = Number of Bits in the Tuning Word

All frequencies are in the same units, Hz, kHz, or MHz. T<sub>wrd</sub> is the decimal equivalent of the binary word to be loaded into the DDS chip, and therein lies our error problem.

At first glance the process seems simple; use Equation 3 to solve for  $T_{\text{wrd}}$  and then load that value into Equation 2 for the DDS. Out pops the desired Fout. Well, not quite, because in most instances the result of the calculation for T<sub>wrd</sub> will be a floating-point number. That is, it will have a fractional part. While Eq 2 will accept a floating-point number, in real life the physical DDS chip will not. The T<sub>wrd</sub> input to the DDS hardware chip must first be converted to an N-bit binary number, which is (unless otherwise defined) an integer, with no fractional part.

To illustrate this I will refine Equations 2 and 3 and redefine some of the variables to help keep things sorted out. Now we have:

$$F_{\text{pred}} = (T_{\text{wint}} X F_{\text{clk}}) / 2^{N}$$

[Eq 4]

$$T_{wfp} = (2^{N} X F_{req}) / F_{clk}$$

[Eq 5]

Where:

$F_{pred}$  = The *Predicted* Output Frequency from the DDS chip as given by Eq 4

$T_{wint}$  = The Tuning Word Input to the DDS Eq 4, a N-bit integer number

$F_{req}$  = The *Requested* Output Frequency from the DDS, the input to Eq 5

$T_{wfp}$  = The computed tuning word from Eq 5, a *floating point* number

$F_{clk}$  = The DDS clock frequency derived from a frequency standard

N = Number of Bits in the Tuning Word

Now for an example using our MSC GDDS 200-32 DDS chip. We have the following:

Figure 3 — Data sheet for the MSC GDDS 200-32 DDS IC.

N = 32 bits

$F_{clk} = 100 \text{ MHz} = 100,000,000.0 \text{ Hz}$

And suppose we want a 1.000,005.0 MHz output frequency, so

$F_{req} = 1,000,005.0 \text{ Hz}$  (i.e. 5 Hz above 1 MHz) Using Equation 5 we compute

$T_{\text{wfp}} = (2^{32} \text{ X } 1,000,005.0) / 100,000,000.0$ = 42, 949, 887.708

Now since the tuning word input to the DDS must be an integer, we drop the .708 on the right of the decimal point, leaving;  $T_{wint} =$ 42, 949, 887.

Next this value is plugged into Equation 4 to predict the actual output frequency from our MSC GDDS 200-32 DDS chip.

$F_{pred} = (42, 949, 887 \times 100,000,000.0) / 2^{32}$ = 1,000,004.9835 Hz

Subtraction of the Requested Frequency from the Predicted Frequency gives the DDS

Error =  $F_{pred} - F_{req} = 1$ , 000, 004. 9835 – 1,000,005.000 = -0.0165 Hz error

So what happened? Our data sheet, Figure 3, specified the resolution of the GDDS 200-32 as 0.047 Hz and the calculated error is only 0.0165 Hz.

Two factors influence the DDS error:

1. The clock frequency. If the clock frequency is halved, the "resolution per step" number is also halved. Further the specifications for resolution are always given at the highest acceptable clock frequency for the particular chip — in this case 200 MHz.

If we take Equation 4 and make  $T_{wint} = 1$ , we get Equation 6

$$F_{act} = (1 \text{ X } F_{clk}) / 2^N = F_{clk} / 2^N \text{ when } T_{wint} = 1$$

The specified resolution is found from simply dividing...

Resolution Hz =

$$F_{clk}$$

/  $2^N$  = 200,000,000 /  $2^{32}$  = 0.047 Hz [Eq 6]

So we see that as  $T_{wint} = 1,2, 3$ , etc; then  $F_{act} = 0.047, 0.094, 0.141$  and so on throughout the entire frequency range of the DDS. So if the clock frequency is halved to 100 MHz then the step size is also halved to 0.0235, 0.047, 0.0705 Hz. etc.

2. The "resolution" does not imply a constant error; rather it is the worst case frequency error that will be encountered for a given clock frequency and number of bits in the control word. In fact, the actual error changes continually as a function of the requested frequency. This is due to rounding off of  $T_{wfp}$  to obtain the integer value for  $T_{wint}$ .

I call this variable error the "Round Off Error". Because of the round off, the actual frequency produced will always be less than the frequency requested, but the error will not exceed the "resolution" as determined by Equation 6 above. The closer the part of the floating point tuning word to the right of the decimal approaches 1 (and the next higher integer value) the greater the round off tuning error. If the output from Equation 5 is a perfectly even number (nnnn.0) then there is no round off and there will be no frequency error. Outputs with no frequency error occur many times across the tuning range of a

As the requested frequency is incremented, this round off error is repeated in a cyclical manner. This may be demonstrated analytically. By using a spreadsheet to repeat the above calculation starting at a base requested frequency and then incrementing it in small steps like 1 Hz we see what happens.

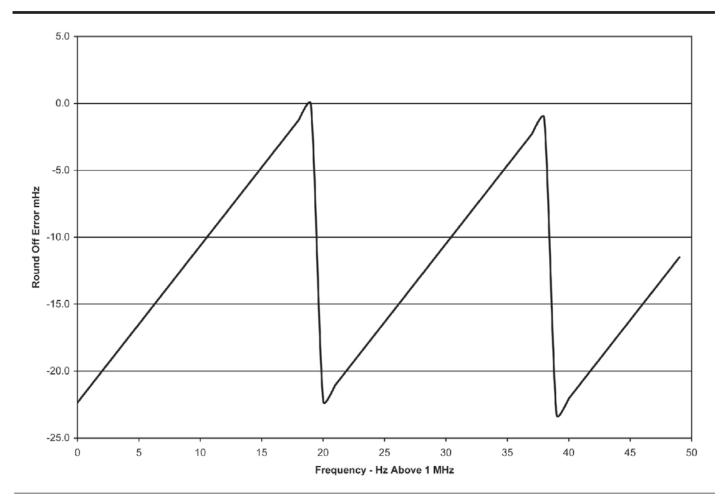

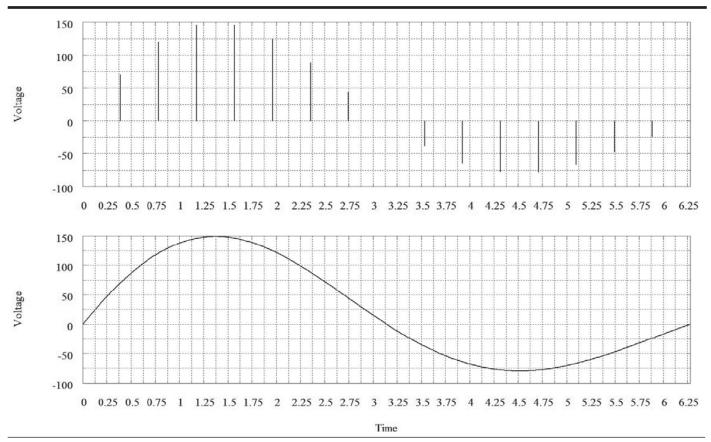

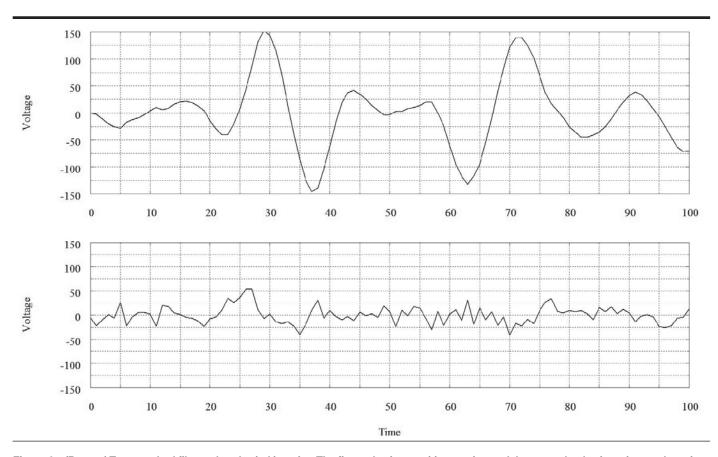

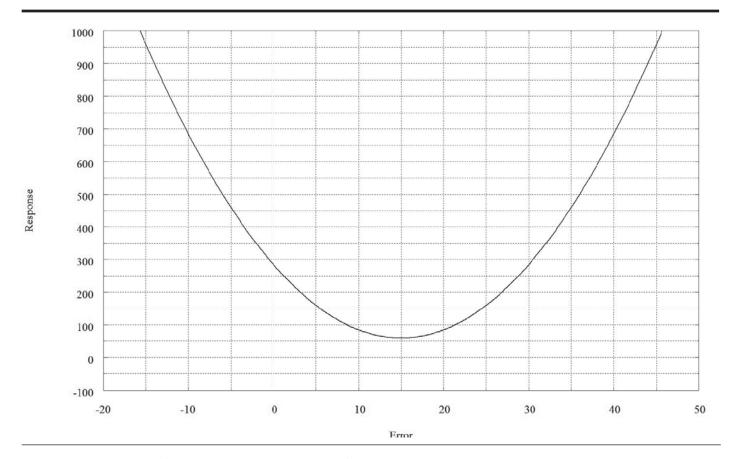

Figure 4 is a graph plotted from an Excel

Figure 4 — The predicted DDS output frequency is compared with requested frequencies in 1 Hz steps from 1,000,000 Hz to 1,000,050 Hz. The error varies cyclically from 0 to about -23 mHz. Note the error is always below the requested frequency.

Figure 5 — In this plot the frequency error is made symmetrical about the requested frequencies by adding 0.5 to the floating point tuning word prior to converting it to an integer. The error is now about +/- 11.5 mHz instead of +0 to -23 mHz.

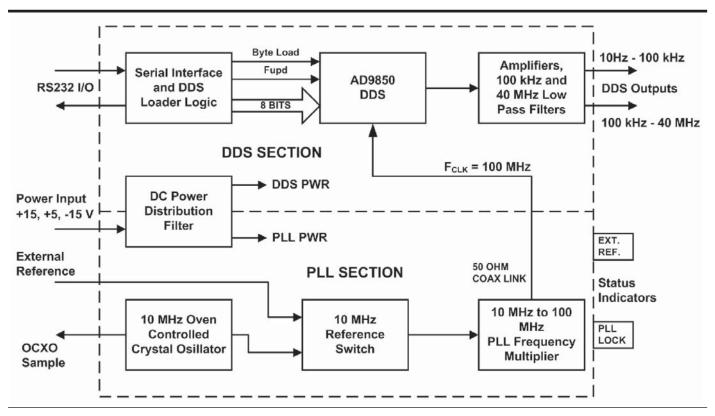

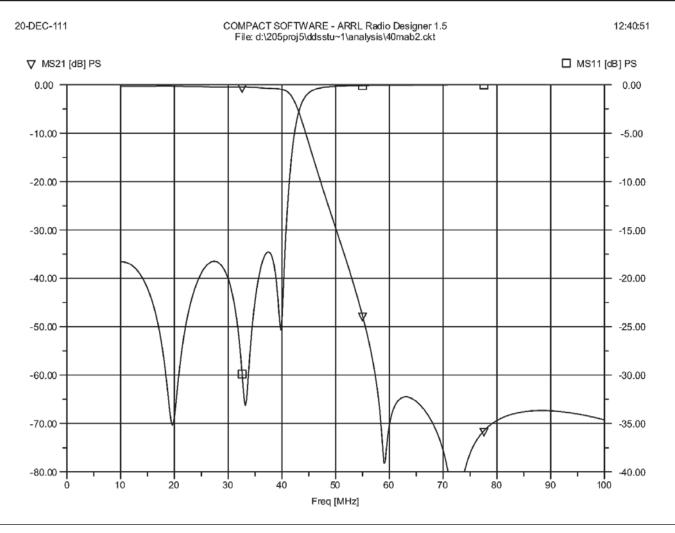

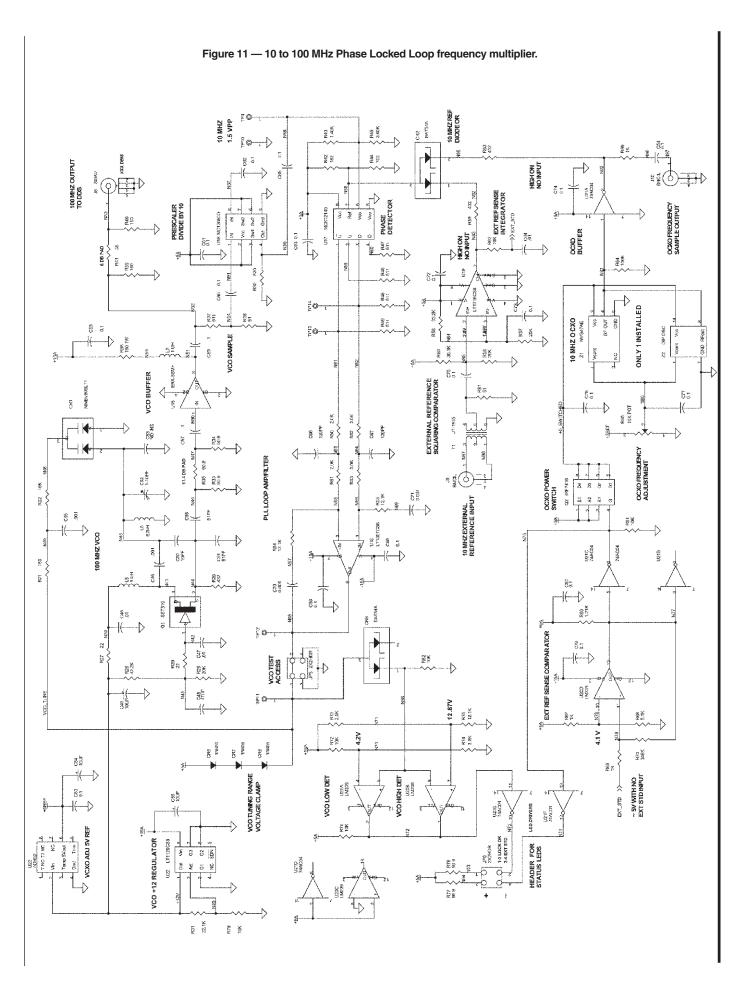

Figure 6 — The FMT DDS is divided into two sections: the DDS circuits and the 10 to 100 MHz clock frequency multiplier. DC power filtering and a coaxial connection from the 100 MHz clock multiplier to the DDS increase the isolation between sections.

spreadsheet. It shows how the frequency error changes, using a 100 MHz clock. The requested frequency was incremented in 1 Hz steps from 1,000,000 Hz to 1,000,050 Hz. Note how the DDS output frequency is always below the requested frequency due to rounding off  $T_{wfp}$  to obtain  $T_{wint}$ .

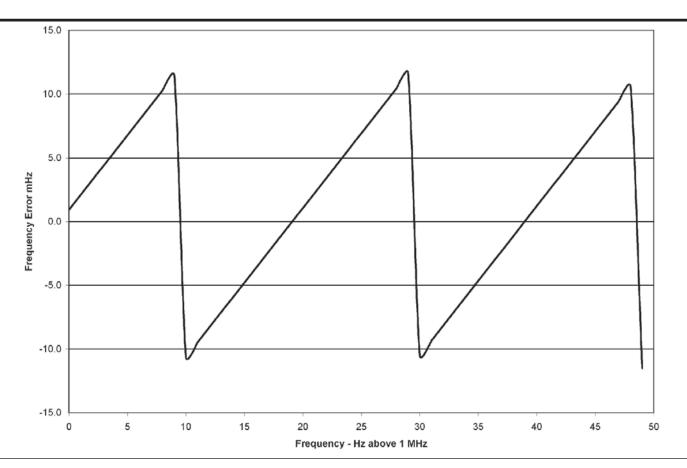

If desired, the actual DDS output frequencies can be compensated to vary symmetrically about the requested frequencies by a simple mathematical trick. Referring again to Equation 5 we can force the round off process to round  $T_{\text{wfp}}$  up to the next higher integer value if the fractional part of T<sub>wfp</sub> is more than 0.5 simply by adding 0.5 to  $T_{wfp}$ .

$$T_{wfp} = (2^N X F_{req}) / F_{clk}$$

Equation 5 is replaced by Equation 7 in which 0.5 is added *prior* to converting T<sub>wfp</sub> from a floating point to an integer number.

$$T_{\text{wfp}} = [(2^{\text{N}} \text{ X } F_{\text{req}}) / F_{\text{clk}}] + 0.5$$

[Eq 7]

Figure 5, shows that if the compensated expression 7 is used and the previous spreadsheet calculation is repeated and plotted, we see that the round off frequency error is now symmetrical about the requested frequency. Now the peak error is halved, and can be specified as being +/- 11 mHz as opposed to + 0 / - 22 mHz. The DDS does not work any differently but the worst case peak error has been halved. This is useful in applications where a simple +/- tolerance on the frequency uncertainty, rather than the exact frequency suffices.

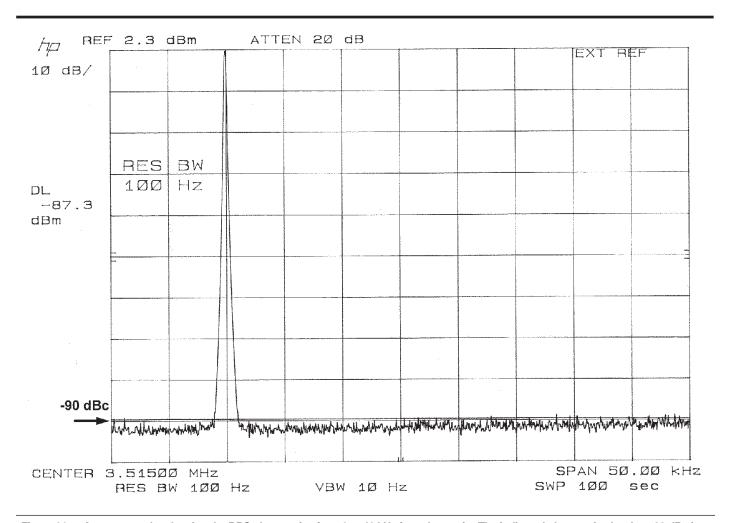

After working through the above analysis, my next step was to implement a DDS in hardware. The objective was simply to prove that  $F_{\text{pred}}$ , as predicted by the math would be identical to the DDS actual output frequency (F<sub>act</sub>) to an accuracy of better the 0.001 Hz. Recalling Equation 1...

$$F_{unk} = F_{ref} + F_{beat}$$

There is no requirement that  $F_{ref}$  is a nice integer frequency like the one I obtained from my lab generators, all we really need for an FMT is to know the frequency accurately. If the DDS control software can provide this, then a DDS can be used to implement a very capable FMT facility.

#### **FMT DDS Hardware Specification**

To frame the discussion of my FMT DDS design, first look at Table 1. It lists the specifications achieved after the dust had settled. For this table the following terms are defined as:

Requested Frequency — The operator input to the DDS control software

**Predicted Output Frequency** — The

DDS output frequency predicted by the software using Equations 4 and 7; including the Round Off Error

Maximum Round Off Error — Maximum expected difference between Requested and Predicted Frequency

**Actual Output Frequency** — Actual frequency produced by the DDS hardware and confirmed by measurement.

DDS Output Frequency Error — Difference between the Predicted Output Frequency and an Actual Measured DDS Output Frequency. Ideally this is less than 0.001 Hz.

#### **FMT DDS Block Diagram**

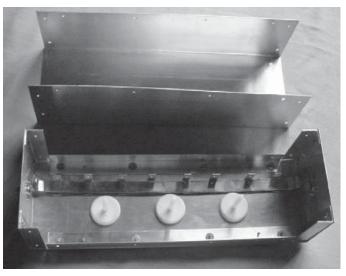

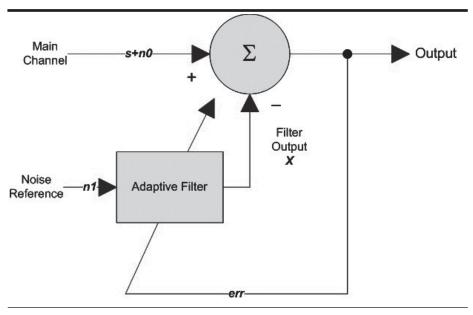

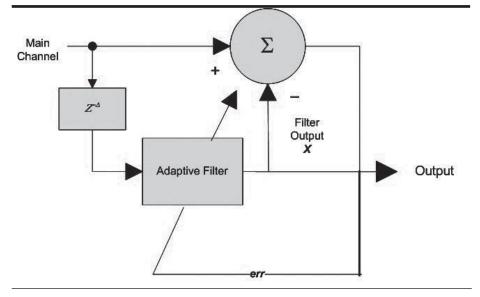

Figure 6 is a top-level block diagram of my FMT DDS showing the overall configuration and the external interfaces. The design is divided into two distinct sets of circuitry, the DDS Section, and the 10X PLL Multiplier Section. While both are on the same board the two circuits are not physically mingled and the power is filtered to keep signals from one section from entering the other. The 100 MHz DDS clock, generated by the clock frequency multiplier is routed directly to the DDS clock input via a matched 50- $\Omega$ coax cable. I did this to make the PLL output and the DDS input accessible for testing and some additional experiments. The only other connection between the sections is the filtered dc power.

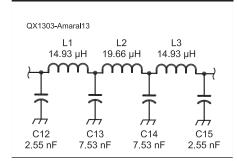

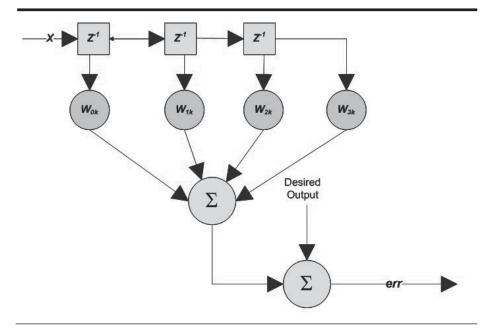

Referring again to the block diagram, the DDS section has three major elements; the serial interface and DDS loader logic, the Analog Devices AD9850 DDS chip and the output amplifiers and low pass filters.

The serial interface and DDS loader logic sequentially receives each of five bytes from the PC. As each serial byte is received it is converted to parallel format and routed to the DDS as an 8 bit parallel byte. It is also converted back to serial and sent back to the PC to check the integrity of the serial link. This proved valuable in de-bugging the design. Additionally, the PC software awaits the reply for each byte before sending the next one. This provides a simple form of software flow control.

#### Table 1 **FMT DDS Performance Specifications**

#### **Output Frequency Ranges**

Audio: 10 Hz to 100 kHz RF: 100 kHz to 40 MHz

#### **Output Levels**

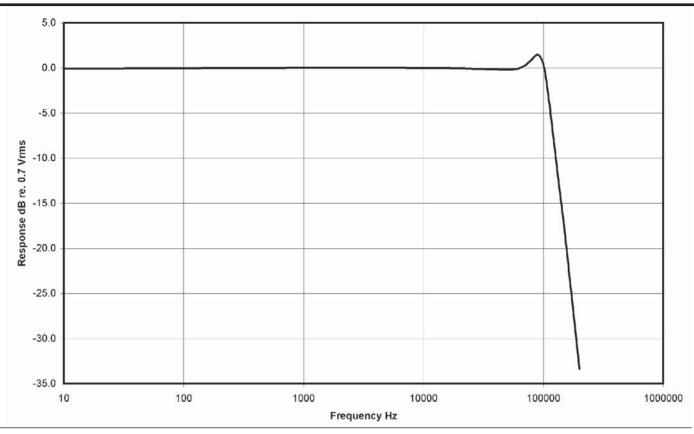

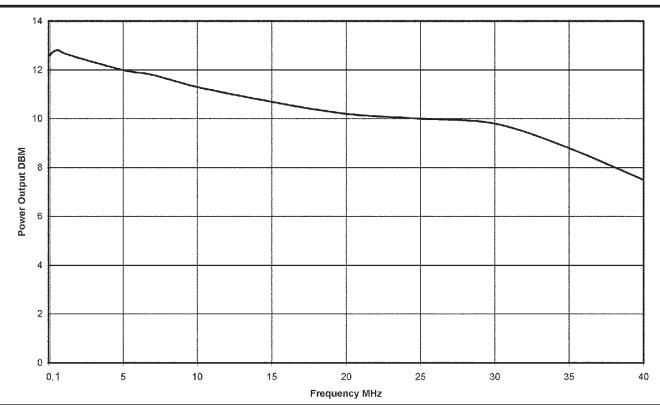

Audio: Open Circuit 0.7 V<sub>rms</sub>, 0 to + 2 dB, 10 Hz to 100 kHz RF: 50  $\Omega$  load 12.7 dBm @ 100 kHz to 7.5 dBm @ 40 MHz

Round Off Frequency Error (Maximum): +/- 11.6 mHz

Measured Output Frequency Error relative to Predicted Output Frequency: + 0.1 to - 0.2 mHz

Required Accuracy of External Reference to Achieve 0.001 Hz Accuracy at 40 MHz: 4 parts in 10<sup>10</sup>

External Reference Input Frequency: 10 MHz

External Reference Input Level Range: -10 to +16 dBm (50  $\Omega$ )

Internal Reference: Bliley NVG47AE 10 MHz OCXO

Internal Reference Stability (0 to 50° C.): Less than +/- 30 parts in 109

Less than +/- 50 parts in 109 Internal Reference Aging Rate per Year:

Internal to External Reference Switchover: Automatic

DDS Clock Frequency: 100 MHz

**DDS Tuning Word: 32 Bits**

PC Control Interface: RS-232 Bi-directional, 9600 Bits/Second, Five 8 bit bytes,

Start, Stop, No Parity

Supported DDS Control Functions: Phase — MS Byte, Frequency 4 Bytes (32 bits).

See AD9850 Data Sheet for details.

dc Power Requirements: +15 V @ 168 mA, -15V @ 13 mA, 5V @ 823 mA

While savvy DDS aficionados will be quick to point out that the AD9850 is not the latest or the best DDS chip around; it was perfect for my application. As indicated on the block diagram, the control protocol is extremely straightforward. The AD9850 supports both a serial and a parallel protocol. I used the parallel protocol that is explained in detail on page 10 of the AD9850 data sheet.8 It is summarized as follows. The control word has a total of 40 bits. The first 8 bits are used for phase control and test functions, while the remaining 32 comprise the 32-bit frequency control. To update the frequency the entire 40 bits must be used. While a serial input to the DDS is convenient, it is not especially compatible with the serial output from a PC COM port because the 40 bits must be input to the DDS in one long string without any start or stop bits. It is easier to send the serial data from the PC COM port to the DDS as 5 normal bytes, convert it to parallel at the DDS, and then load it into the DDS as 5 individual bytes using the parallel load format. Note the bytes are sent in reverse numerical order. Byte 4, the most significant byte is sent first. It is the phase control byte. Then bytes 3, 2, 1 and 0 are sent and comprise the 32-bit frequency control integer.

Because the DDS hardware requires the phase control byte to be sent first, all 5 bytes must be sent, though the AD9850 only uses four to achieve 32-bit frequency control. The fifth byte can be used to implement RF phase control. This is not used in the FMT application, though the DDS hardware described here will support it. For simple frequency control byte 4 (the first sent) is simply sent as all "0."

Upon receiving the first byte, the  $F_{upd}$  line is set low by the loader logic. The first byte is presented to the DDS and a rising edge on the Word Load line clocks it into the DDS. This process continues for four subsequent bytes. The loader logic counts the bytes and after the fifth byte has been loaded, the  $F_{\mbox{\tiny upd}}$  is set high which updates the DDS to the new frequency. For me the appeal of this scheme is the simplicity. The entire control logic was implemented with a few Complementary Metal Oxide Semiconductor (CMOS) chips and an on-board micro-controller was not needed.

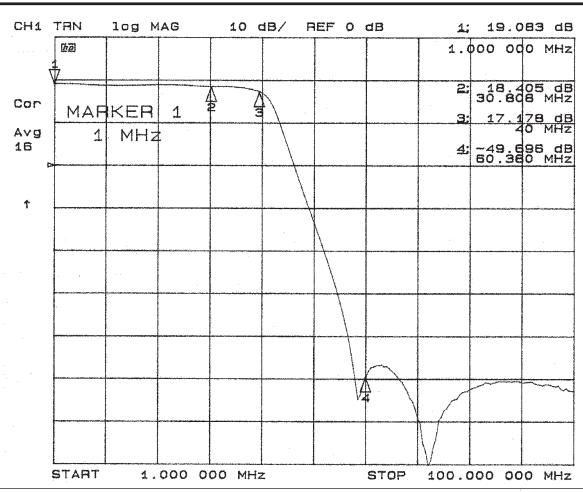

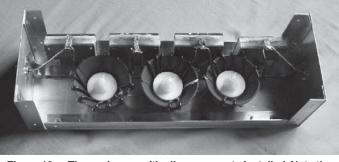

From the DDS output the synthesized frequency is routed to a pair of low pass filters and output amplifiers. Two bands are provided having separate outputs. The AF band extends from below 10 Hz to 100 kHz. An active low pass filter rolls off output above 100 kHz, primarily because the output amplifier will not perform too well above this frequency. The RF output is active from below 100 kHz to 40 MHz. Above 40 MHz an antialiasing filter rolls off the response. This filter prevents the 60 MHz alias that would show up at the output, when the DDS is set for 40 MHz, from appearing on the output. The AF and RF output levels are internally adjustable so they can be set to known levels. External step attenuators are then used to reduce the signals as required by the application.

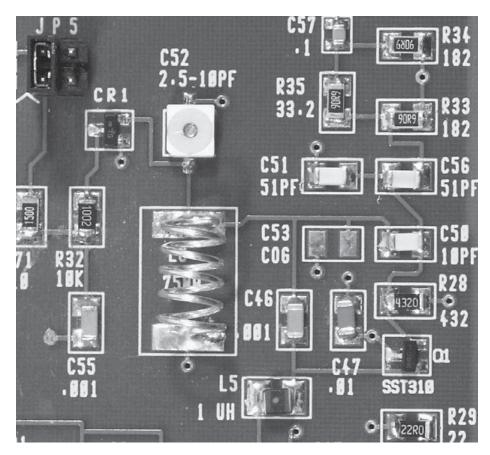

The 10X PLL frequency multiplier, which is shown in the lower half of Figure 6, generates a 100 MHz clock for the DDS. This PLL, referenced to a 10 MHz frequency standard, locks a 100 MHz Voltage Controlled Oscillator (VCO) to provide a low spurious 100 MHz clock. The 10 MHz reference is derived either from an on-board Oven Controlled Crystal Oscillator (OCXO) or from an external reference depending upon the required frequency accuracy. Selection of the reference source is automatic. Application of an external reference is sensed and the OCXO is shut down and the reference switch routes the external reference to the PLL. A sample of the OCXO frequency is routed to the rear panel enabling the oscillator to be calibrated by an externally accessible pot.

Front panel external interfaces, Figure 1, include the AF and RF output BNC connectors and two status indicating LEDs. One status indicator is illuminated when the 10X multiplier PLL is correctly in lock. The other illuminates when an external 10 MHz reference is present and of sufficient amplitude to enable switching from the internal to the external reference.

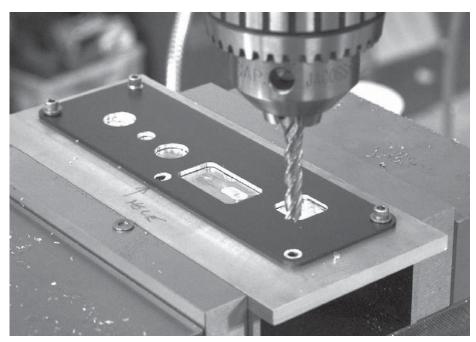

Rear panel interfaces, Figure 7, include BNC connectors for the 10 MHz external reference input, and the OCXO frequency sample output. A hole provides access to the adjustment pot for calibration of the OCXO frequency. Also located on the rear panel are the DB-9 connector for the serial control data, and the dc power connector.

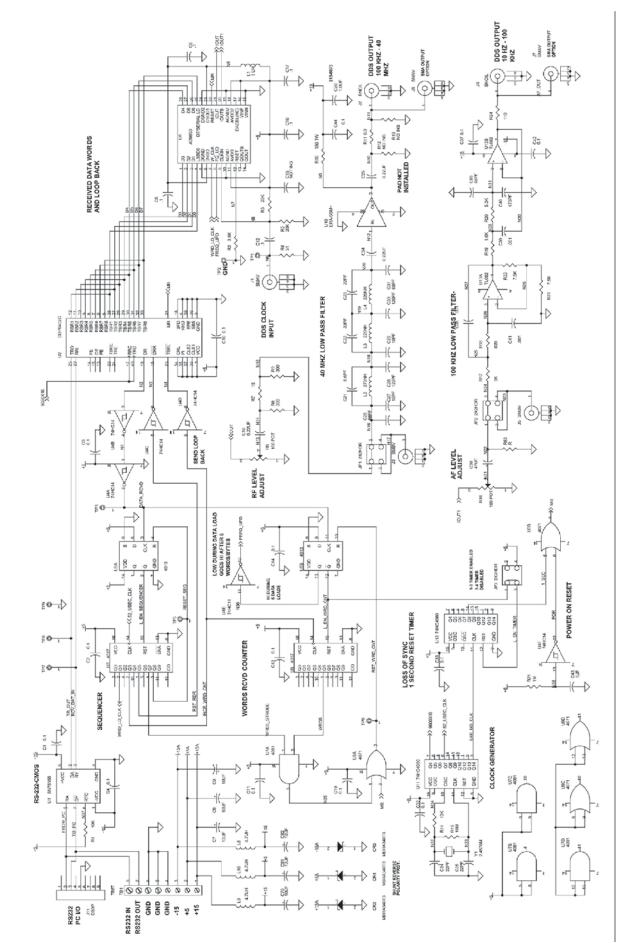

#### **DDS Section Schematic**

Full size copies of the schematics and other pertinent data will be posted on the OEX website at www.arrl.org/qexfiles in a zip file named ROOS.zip. Just look for the March/April 2013 issue in the Table.

I will also provide full (B) size PDFs directly to anyone requesting copies by e-mail. It is probably easier to follow the discussion with a full size schematic at hand.

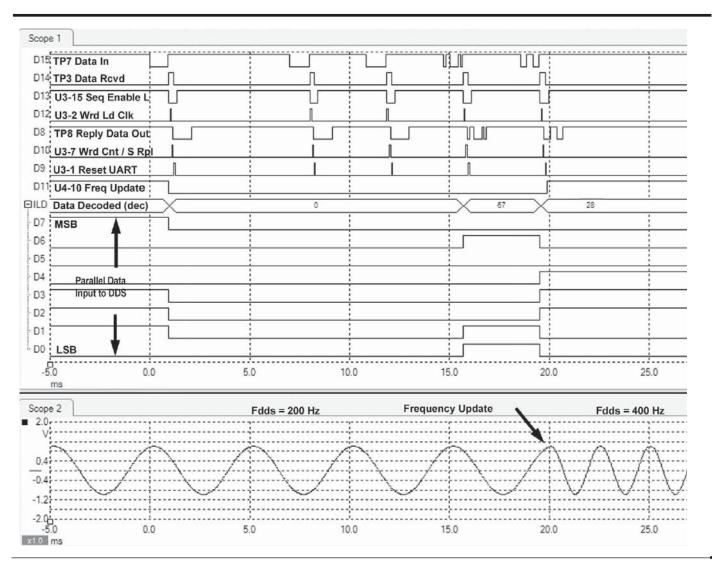

Figure 8 is the schematic of the DDS section. The logic timing diagram, Figure 9, is a mixed signal logic and analog scope<sup>9</sup> screen capture showing events as the DDS is programmed to step from 200 to 400 Hz. I used a step from 200 to 400 Hz so the frequency step would be displayable on the same time scale as the logic events. The logic analyzer probe display lines are labeled D0 to D15 for identification

Referring to Figure 8, power and optionally the control data are input to the board at TB1. TB1 is a plug-on terminal block that mates with a header on the Printed Wiring Board (PWB). This is convenient in the test environment. A separate DB9 connector is

Figure 7 — Located on the rear panel of the FMT DDS are the External Reference Input, the OCXO Sample output, the OCXO adjustment, and the PC and power connectors.

Figure 8 — Schematic of the DDS section of the synthesizer. Please see Roos.zip on the QEX website at www.arrl.org/qexfiles for a larger version of this drawing.

provided for the PC I/O. When installed in the cabinet, a short jumper cable connects TB1 to the rear panel Molex power connec-

Key to operation of the logic are the two 4017 CMOS counters, U3 and U8. The 4017 counter is handy when a simple set of events must take place in sequence because the chip has 10 internally decoded outputs. These may be connected to provide strobes as required without a lot of decoding logic. The scheme is effective and avoids race conditions, provided super high speed is not needed. U3 is the "sequence" counter. It steps the logic through its paces as each byte is received. U8 is the "words received counter." U8 keeps track of the number of bytes received and asserts the "frequency update" after receipt of the 5th byte. (Though 8 bits are commonly a Byte, the Analog Devices D data sheet uses the term Word and I have followed that convention where it applies).

RS-232 level frequency data from the PC

is converted by U1 to TTL/CMOS logic levels and sent on to U2, a CDP6402C Universal Asynchronous Receiver Transmitter (UART).<sup>10</sup> The UART converts each byte from serial to parallel and the parallel data is routed to U6, the AD9850 DDS. The data in parallel format is also looped back to the transmit side of the UART for transmission back to the PC. The data rate is fixed at 9600 bits per second.

Clocks for the data communications and the sequencer are provided by Y-1, a 2.4576 MHz crystal, and U11. The sequencer uses a 52-microsecond clock, and while a faster clock would speed up the logic it would have little effect on the DDS update rate. Figure 9 shows that most of the update time is consumed by the PC

Referring to the schematic and Figure 9, D15 shows the first serial byte (all zeros) being received. The UART outputs the pulse seen at D14, TP3 Data Received. This pulse clocks U5A, which clears the reset at U3-15 to assert D13, Sequencer Enabled Low. At the same time it also clocks U5-B which clears the reset from U8-14 to enable U8 to count the received words. The Q output from U5-B is inverted by U4-E and routed to the DDS asserting the "Frequency update" line low. This is shown as D11, U4-10 on Figure 9. The DDS can now accept new data.

Next U3 begins counting up from 0 to 1 asserting U3-2, Word Load Clock high, indicated as D12, in Figure 9. This signal is routed to the DDS U6-7 and clocks the first 8-bit word into the AD9850.

U3 continues counting up to 3 where the decoded output on U3-7, Increment Word Count, performs two actions. It is routed to the word counter U8 clock input at U8-14 to increment the received word from 0 to 1. It is also sent to U4, where after inversion it is applied to Pin 23 of the UART. See trace D10, U3-7 Increment Word Count / Send Reply in Figure 9.

The high to low transition at Pin 23 loads

Figure 9 — Mixed signal 'scope capture of the DDS Frequency Update Process as the frequency is switched from 200 to 400 Hz.

the copy of the received data word at the UART receiver output back into the UART transmitter buffer. When Pin 23 is returned low as the sequence counter increments from 3 to 4, the UART sends the copy of the data back to the PC. This is trace D8, TP8 Reply Data Out, in Figure 9.

Sequencer U3 continues counting up from 3 to 5. When the count reaches 5 output from U3-1 is routed via the inverter U4C to Pin 18 of the UART, U2. This pulse resets the UART receiver data buffer and readies it to receive the next serial byte. See trace D9. U3-1 Reset UART on Figure 9.

Next sequencer U3 counts up from 5 to 7 and outputs a strobe that is applied to one input of the AND gate U7A-1. For the first four received bytes nothing happens because the Word Counter U8 has not yet counted up to 5.